在電子工程師的日常工作中,A/D轉換器是不可或缺的關鍵組件。今天,我們要深入探討一款性能卓越的8位A/D轉換器——ADC08L060,它來自德州儀器(TI),具有低功耗、高轉換速率等諸多優點,廣泛應用于數字成像、通信系統等多個領域。

文件下載:adc08l060.pdf

一、產品概述

ADC08L060是一款低功耗、8位的單片式模擬 - 數字轉換器,內置采樣保持電路。它的獨特架構使其在輸入頻率達到甚至超過奈奎斯特頻率時,仍能實現超過7個有效位。該產品的轉換速率范圍為10 MSPS至60 MSPS,每兆赫茲時鐘頻率僅消耗0.65 mW的功率,在60 MSPS時功耗為39 mW。此外,它還具備掉電功能,當PD引腳置高時,轉換器進入掉電模式,功耗約為1 mW。

二、產品特性與關鍵規格

(一)特性

- 單端輸入:簡化了輸入電路的設計。

- 內部采樣保持功能:確保在轉換過程中輸入信號的穩定。

- 低電壓(單 +3V)運行:降低了功耗和系統復雜度。

- 小封裝:適合空間受限的應用場景。

- 掉電特性:在不需要轉換時可降低功耗。

(二)關鍵規格

- 分辨率:8位

- 轉換速率:最高可達60 MSPS

- DNL(差分非線性):典型值為±0.25 LSB

- INL(積分非線性):典型值為 +0.5/?0.2 LSB

- SNR(信噪比):在10.1 MHz時典型值為48 dB

- ENOB(有效位數):在10.1 MHz時典型值為7.6位

- THD(總諧波失真):在10.1 MHz時典型值為 -57 dB

- 延遲:5個時鐘周期

- 無丟失碼:確保轉換的準確性

三、引腳說明與功能

| ADC08L060采用24引腳塑料封裝(TSSOP),各引腳功能如下: | 引腳編號 | 符號 | 功能描述 |

|---|---|---|---|

| 6 | VIN | 模擬信號輸入,轉換范圍為VRB至VRT | |

| 3 | VRT | 參考梯形網絡的高端模擬輸入,定義VIN的轉換范圍 | |

| 9 | VRM | 參考梯形網絡的中點,需用0.1 μF電容旁路到模擬地平面的安靜點 | |

| 10 | VRB | 參考梯形網絡的低端模擬輸入,定義VIN的轉換范圍 | |

| 23 | PD | 掉電輸入,高電平時轉換器進入掉電模式 | |

| 24 | CLK | CMOS/TTL兼容的數字時鐘輸入,VIN在CLK上升沿采樣 | |

| 13 - 16和19 - 22 | DO - D7 | 轉換數據的數字輸出引腳,D0為LSB,D7為MSB | |

| 7 | VIN GND | 單端模擬輸入VIN的參考地 | |

| 1, 4, 12 | VA | 正模擬電源引腳,需連接到 +3V的安靜電壓源,并進行適當的旁路 | |

| 18 | VDR | 輸出驅動器的電源,若連接到VA,需與VA良好去耦 | |

| 17 | DR GND | 輸出驅動器電源的地返回 | |

| 2, 5, 8, 11 | AGND | 模擬電源的地返回 |

四、電氣特性分析

(一)直流精度

- INL(積分非線性):典型值為 +0.5/?0.2 LSB,最大值為 +1.9/?1.35 LSB。

- DNL(差分非線性):典型值為±0.25 LSB,最大值為±0.90 LSB。

- 丟失碼:最大值為0,確保了轉換的準確性。

(二)模擬輸入與參考特性

- VIN(輸入電壓):范圍為VRB至VRT。

- CIN(輸入電容):在CLK低電平時為3 pF,高電平時為4 pF。

- RIN(輸入電阻):大于1 MΩ。

- BW(全功率帶寬):270 MHz。

(三)數字輸入與輸出特性

- VIH(邏輯高輸入電壓):最小值為2.0 V。

- VIL(邏輯低輸入電壓):最大值為0.8 V。

- VoH(高電平輸出電壓):最小值為2.4 V。

- VoL(低電平輸出電壓):最大值為0.5 V。

(四)動態性能

- ENOB(有效位數):在10.1 MHz時典型值為7.6位,最小值為6.9位。

- SINAD(信噪失真比):在10.1 MHz時典型值為47.4 dB,最小值為43.3 dB。

- SNR(信噪比):在10.1 MHz時典型值為48 dB,最小值為44.5 dB。

五、應用設計要點

(一)參考輸入設計

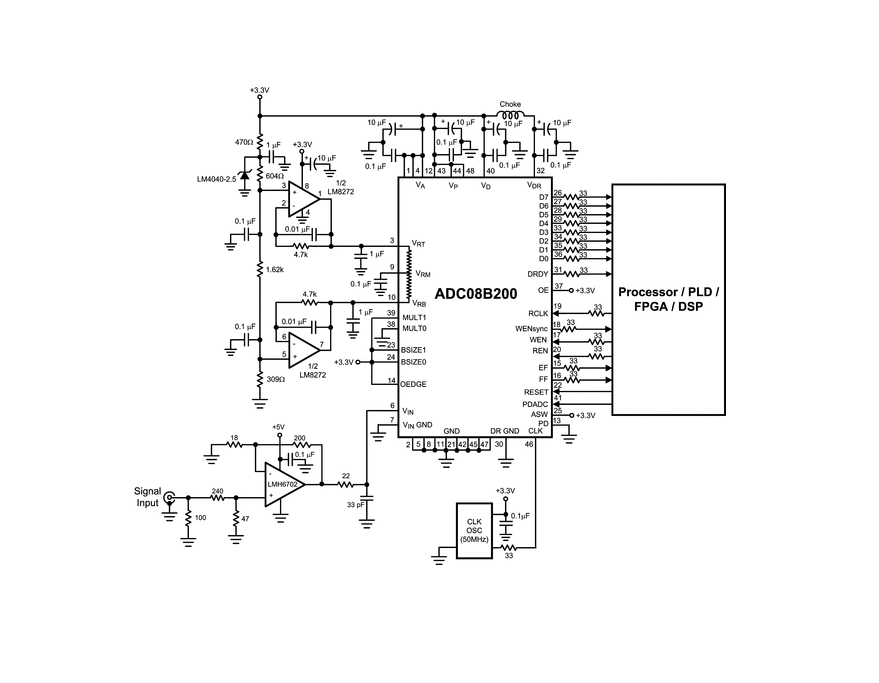

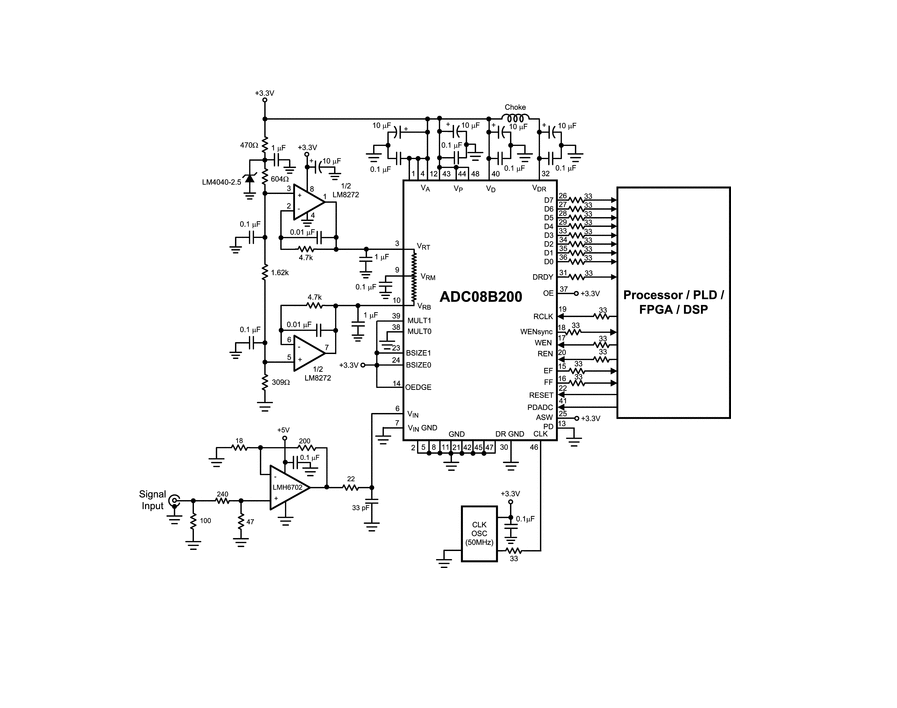

參考輸入VRT和VRB分別是參考梯形網絡的頂部和底部,輸入信號在這兩個電壓之間將被數字化為8位。為了確保參考電壓的穩定性,建議使用低阻抗源驅動參考引腳。例如,可以使用LM8272運算放大器來實現更精確的參考電壓設置。同時,VRT應始終比VRB正至少參考電壓差的最小值,以減少噪聲;VRT和VRB之間的差值不應超過電氣特性表中規定的最大值,以避免信號失真。VRM引腳是參考梯形網絡的中心,需用0.1 μF電容旁路到模擬地平面的安靜點,切勿讓該引腳浮空。

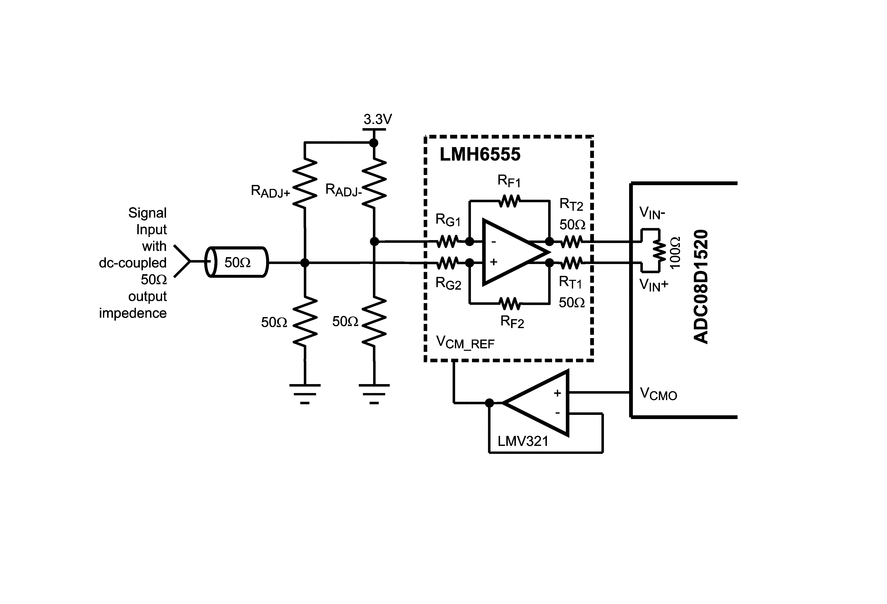

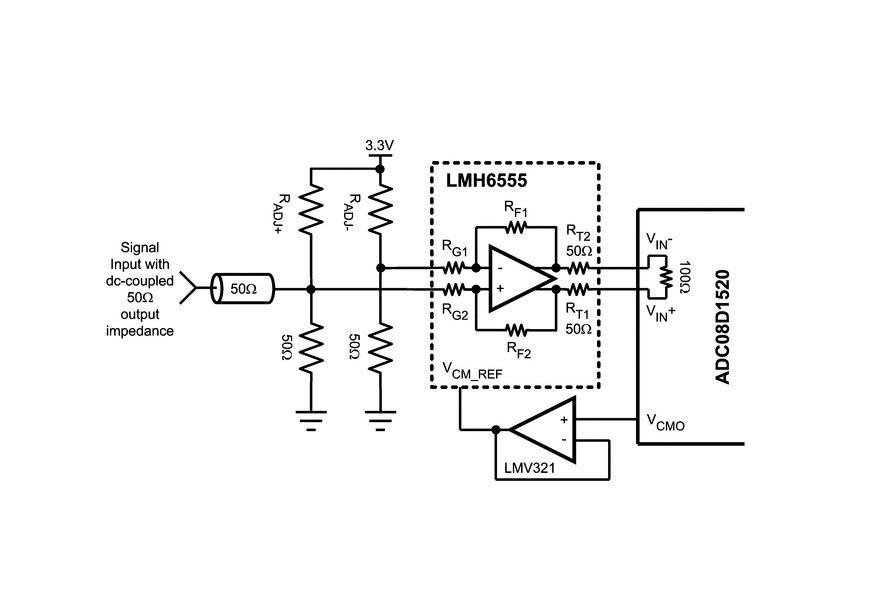

(二)模擬輸入設計

ADC08L060的模擬輸入是一個開關后跟一個積分器,輸入電容隨時鐘電平變化,時鐘低電平時為3 pF,高電平時為4 pF。這種動態電容使得驅動輸入更加困難,因此在選擇驅動器件時需要考慮這一因素。推薦使用LMH6702放大器來驅動模擬輸入,輸入放大器應具有一定的增益,以獲得最佳性能。同時,在放大器輸出端添加RC濾波器可以過濾由于輸入采樣電路產生的時鐘頻率能量,但需要根據具體情況選擇合適的電阻和電容值,以優化SNR、THD和SINAD性能。

(三)電源供應設計

A/D轉換器在工作時會產生較大的瞬態電流,如果電源旁路不足,可能會導致電源電壓波動,從而影響轉換器的性能。因此,建議在A/D電源引腳附近放置10 μF的鉭或鋁電解電容和0.1 μF的陶瓷片電容。對于ADC08L060的VA和VDR電源,雖然推薦使用單一電壓源,但這兩個電源引腳應相互隔離,以防止數字噪聲耦合到模擬部分。可以在這兩個電源線路之間使用扼流圈或27 Ω電阻,并在電源引腳附近添加適當的旁路電容。此外,由于高速轉換器的電源抑制能力較弱,建議為轉換器單獨提供電源,避免與其他數字電路共用電源。

(四)數字輸入設計

ADC08L060有兩個數字輸入引腳:PD引腳和時鐘引腳。PD引腳用于控制轉換器的掉電模式,高電平時進入掉電模式,功耗降低。時鐘引腳的頻率范圍通常為10 MHz至80 MHz,雖然該轉換器在60 MHz時鐘下進行測試和性能保證,但在其他頻率下也能正常工作。時鐘信號的占空比會影響A/D轉換器的性能,ADC08L060設計為在5%至95%的占空比范圍內保持性能穩定。為了減少時鐘信號的反射和干擾,時鐘線應在時鐘源處進行串聯端接,并在CLOCK引腳處進行交流端接。

(五)布局與接地設計

正確的接地和信號布線對于確保準確的轉換至關重要。建議使用模擬和數字組合的接地平面,以減少數字開關瞬態對模擬信號的影響。模擬和數字電路應分開布局,避免相互干擾。同時,為了減少噪聲耦合,應盡量縮短ADC時鐘線的長度,并將其與其他信號隔離。在ADC輸出引腳處,建議使用47 Ω電阻進行串聯,以減少噪聲。此外,應注意避免在ADC輸出線下方鋪設接地平面銅,以減少輻射。

六、常見應用陷阱與解決方法

(一)輸入電壓超出范圍

在使用過程中,要確保所有輸入電壓不超過電源引腳電壓300 mV或低于地引腳電壓300 mV,否則可能導致轉換器故障或不穩定。對于可能出現過沖或下沖的數字輸入,可以在輸入引腳處串聯一個51 Ω電阻來解決問題。

(二)驅動能力不足

如果使用的放大器無法驅動模擬輸入的動態電容,或者驅動VRT和VRB引腳的器件無法提供足夠的電流,會導致參考引腳不穩定,從而降低動態性能。因此,在選擇驅動器件時,要充分考慮其驅動能力。

(三)時鐘信號問題

時鐘源的抖動過大、時鐘信號走線過長或其他信號耦合到時鐘信號走線,都會導致采樣間隔變化,從而增加輸出噪聲并降低SNR性能。建議使用低抖動的時鐘源,并對時鐘信號進行適當的端接和隔離。

(四)負載電容過大

如果數字數據總線的電容過大,會導致輸出驅動器需要消耗更多的電流,從而影響動態性能。可以使用緩沖器對數字數據輸出進行緩沖,或者在每個數字輸出端添加100 Ω的串聯電阻,以減少耦合回轉換器輸入引腳的能量。

七、總結

ADC08L060是一款性能卓越的8位A/D轉換器,具有低功耗、高轉換速率、良好的動態性能等優點。在設計應用時,我們需要充分考慮其引腳功能、電氣特性和應用要點,避免常見的應用陷阱。通過合理的設計和布局,我們可以充分發揮ADC08L060的優勢,為各種電子系統提供高質量的模擬 - 數字轉換解決方案。希望本文能為廣大電子工程師在使用ADC08L060時提供一些有益的參考和幫助。

如果你在使用ADC08L060的過程中遇到任何問題,或者有其他相關的技術交流,歡迎在評論區留言分享。讓我們一起在電子設計的道路上不斷探索和進步!

-

MSPS

+關注

關注

0文章

574瀏覽量

29007 -

模數轉換器

+關注

關注

26文章

4044瀏覽量

130202 -

數字轉換器

+關注

關注

0文章

348瀏覽量

28824 -

輸入電路

+關注

關注

2文章

52瀏覽量

10995

發布評論請先 登錄

ADC08L060,pdf datasheet (8-Bit

深入解析ADC08B3000:高性能8位3GSPS A/D轉換器的技術奧秘

深入剖析ADC08500:高性能8位500 MSPS A/D轉換器的設計與應用

深入解析ADC08D1520:高性能8位ADC的卓越之選

深入解析ADC08D500:高性能低功耗8位500 MSPS A/D轉換器

深入剖析ADC10321:高性能10位A/D轉換器的設計與應用

深入剖析ADC08L060:高性能8位A/D轉換器的設計與應用

深入剖析ADC08L060:高性能8位A/D轉換器的設計與應用

評論