在電子設計領域,高速、高效的模擬 - 數字轉換器(ADC)至關重要。TI的ADC08B200就是這樣一款高性能的8位、200 MSPS A/D轉換器,它集成了捕獲緩沖器,適用于多種高速數據采集應用。今天,我們就來深入探討這款芯片的特性、應用以及設計要點。

文件下載:adc08b200-q1.pdf

芯片特性概述

高性能核心

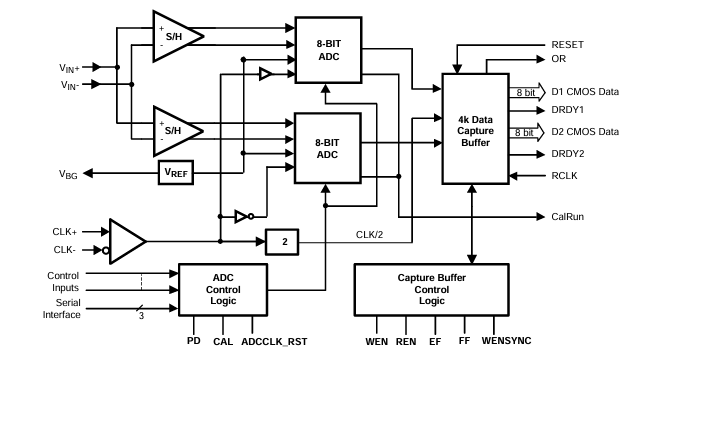

ADC08B200基于成熟的ADC08200架構,采用8位、200 MSPS的A/D核心,集成了跟蹤保持電路,優化了低功耗設計。它的輸入為單端輸入,并且捕獲緩沖器的大小可選擇,最大可達1024字節,這使得它能夠快速捕獲輸入信號,并以較慢的速率讀出數據。

豐富的功能特性

- 時鐘PLL電路:片上時鐘PLL電路可實現時鐘速率倍增,提供高速采樣時鐘。

- 參考梯級訪問:參考梯級的頂部和底部可訪問,為輸入信號提供了更廣泛的可能性。

- 線性功率縮放:功率消耗與采樣率呈線性關系,有效控制功耗。

- FPGA訓練模式:支持FPGA訓練模式,方便系統集成。

- 汽車級認證:ADC08B200Q符合AEC - Q100 2級標準,適用于汽車電子應用。

應用領域

ADC08B200具有抗閂鎖特性,輸出具有短路保護功能,數字輸出與TTL/CMOS兼容,適用于多種應用場景,如激光測距、雷達系統和脈沖捕獲等。

關鍵規格參數

| 參數 | 詳情 |

|---|---|

| 分辨率 | 8位 |

| 最大采樣頻率 | 200 MSPS(最小) |

| 差分非線性(DNL) | ±0.4 LSB(典型) |

| 有效位數(ENOB) | 7.2位(典型,$f_{IN}=49 MHz$) |

| 總諧波失真(THD) | -53 dBc(典型,$f_{IN}=49 MHz$) |

| 功耗 - 工作(50 MHz輸入) | 2 mW / Msps(典型) |

| 功耗 - 掉電模式 | 2.15 mW(典型) |

引腳配置與功能

引腳配置

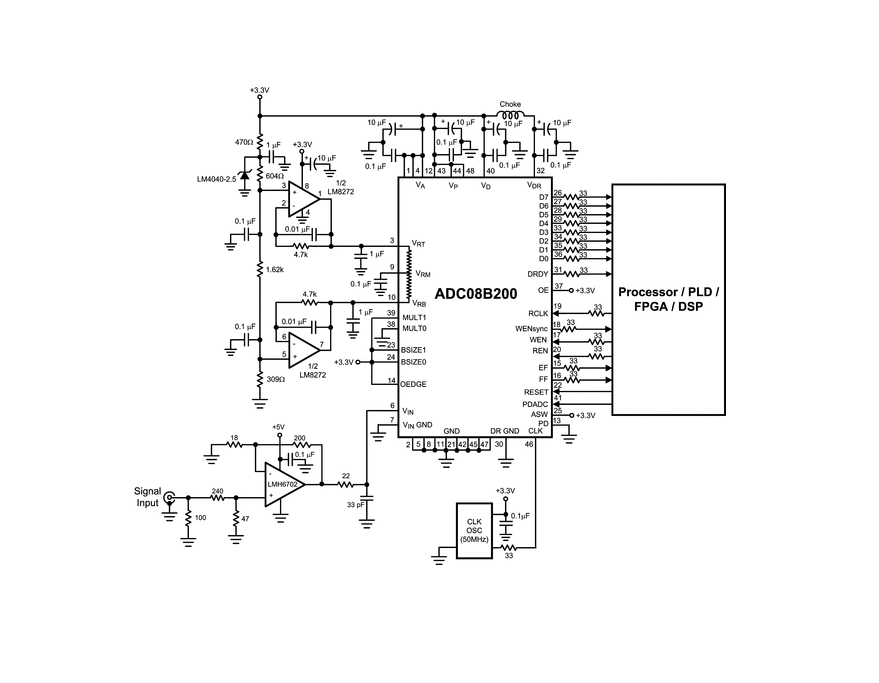

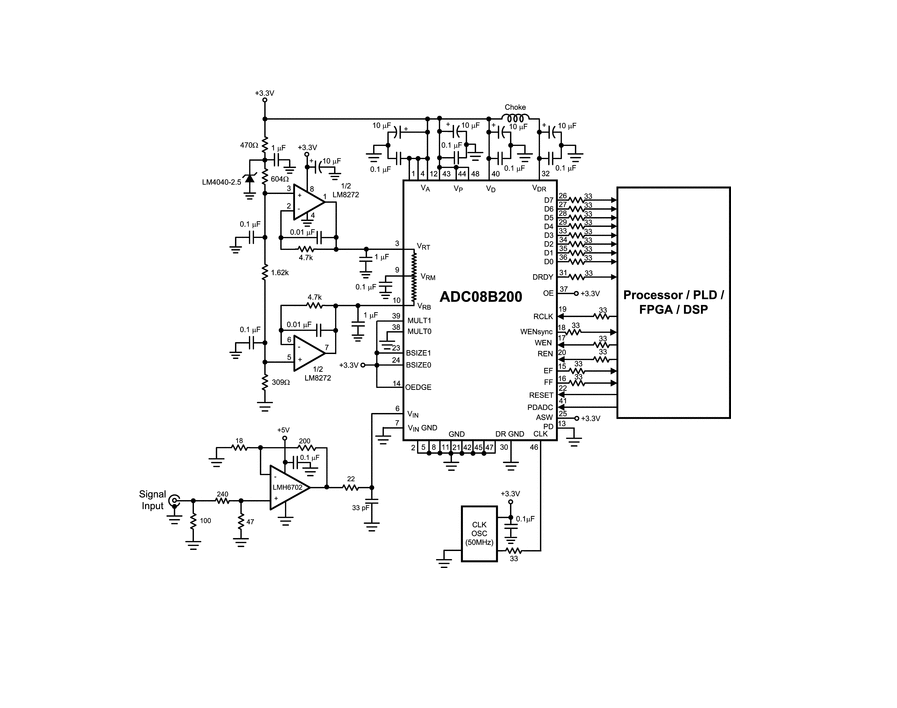

ADC08B200采用48引腳塑料封裝(TQFP),引腳配置涵蓋了模擬輸入、參考輸入、電源、時鐘、控制和數字輸出等多種功能。

引腳功能詳解

- 模擬輸入與參考引腳:$VIN$為模擬信號輸入,轉換范圍由$VRT$和$VRB$定義;$VRT$和$VRB$分別為參考梯級的高端和低端輸入,$VRM$為參考梯級的中點輸入。

- 電源與掉電引腳:$PD$為芯片掉電輸入,$PDADC$為ADC掉電輸入,可實現不同級別的功耗控制。

- 時鐘與控制引腳:$CLK$為數字時鐘輸入,$RCLK$為緩沖器讀取時鐘輸入,$WEN$為寫使能輸入,$REN$為讀使能輸入,$RESET$為設備復位輸入,$OE$為輸出使能輸入。

- 狀態標志引腳:$FF$為緩沖器滿標志,$EF$為緩沖器空標志,$DRDY$為數據準備好輸出,$WENSYNC$為同步寫使能輸出。

電氣特性與性能

直流精度

ADC08B200在直流精度方面表現出色,積分非線性(INL)最大為±1.3 LSB,差分非線性(DNL)最大為±0.9 LSB,無丟失碼。

模擬輸入與參考特性

輸入電壓范圍為$VRB$到$VRT$,輸入電容在時鐘低電平時為3 pF,高電平時為4 pF,模擬輸入電阻大于1 MΩ,全功率帶寬為500 MHz。

數字輸入特性

邏輯高輸入電壓($VIH$)和邏輯低輸入電壓($VIL$)在不同引腳有不同的要求,以確保正確的邏輯電平識別。

電源特性

不同電源的電流消耗在不同輸入條件下有所不同,如模擬電源電流($IA$)在直流輸入時為72.5 mA,$f_{IN}=50 MHz$時為76.8 mA(最大88.3 mA)。

諧波與失真特性

在不同輸入頻率和幅度下,ADC08B200的總諧波失真(THD)和互調失真(IMD)表現良好,如在$f_{IN}=49 MHz$,$VIN=FS - 0.25 dB$時,THD為 - 63 dBc。

時鐘與定時特性

時鐘選項

ADC08B200的PLL可實現時鐘倍增,用戶可根據需要選擇不同的時鐘倍增因子,也可選擇旁路PLL。

定時特性

時鐘的最大和最小輸入速率、高低電平時間等都有嚴格的要求,以確保ADC的正常工作。例如,最小$CLK$低電平時間和高電平時間均為1.7 ns(最小)。

功能描述與操作模式

數據采集與處理

數據在采樣時鐘的上升沿采集,在緩沖器旁路模式下,數字數據在6個時鐘周期加$t_{OD}$后在輸出引腳可用。當緩沖器啟用時,轉換后的數據寫入緩沖器,并可通過$RCLK$信號讀出。

緩沖器控制

緩沖器的讀寫操作由$WEN$和$REN$控制,且不能同時進行。緩沖器有滿標志($FF$)和空標志($EF$),可用于管理緩沖器的狀態。

操作模式

ADC08B200有多種操作模式,包括關機模式、緩沖器活動 - ADC關機模式、數據讀取模式和數據捕獲模式等,可通過不同的引腳組合實現。

應用設計要點

參考輸入設計

參考輸入$VRT$和$VRB$的電壓應在規定范圍內,外部驅動設備應能提供足夠的電流。可采用低阻抗源驅動參考引腳,以提高參考電壓的精度。

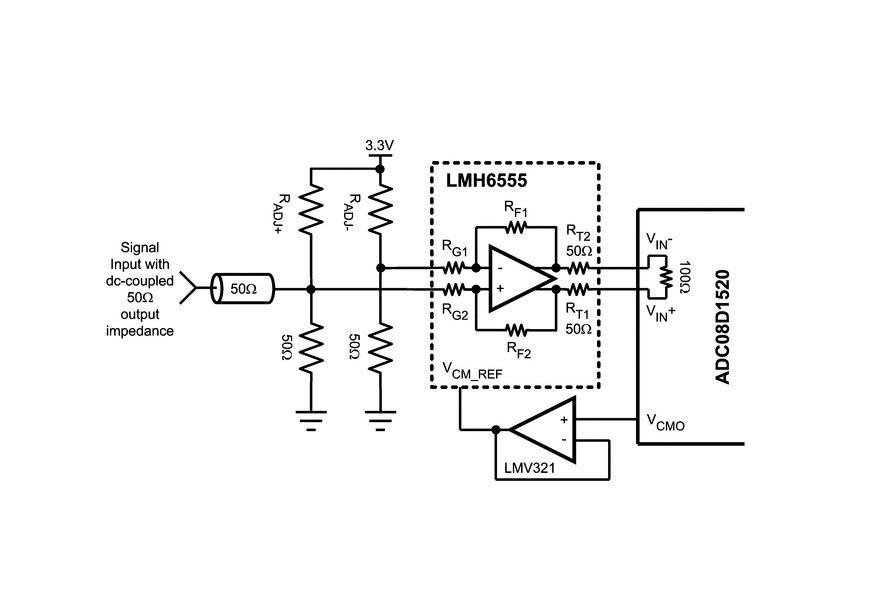

模擬輸入設計

模擬輸入為開關加積分器結構,輸入電容隨時鐘電平變化。為減少輸入電壓尖峰對驅動放大器的影響,可在放大器和ADC輸入之間使用單極RC濾波器。

電源設計

電源設計至關重要,每個電源引腳應使用適當的旁路電容,以降低電源噪聲。建議使用相鄰的電源和接地平面,以降低電源分配系統的阻抗。

時鐘設計

時鐘信號應盡量短且遠離其他信號,以減少時鐘抖動。時鐘輸入線應根據長度進行適當的終端匹配,以確保信號完整性。

常見應用陷阱與解決方法

- 輸入電壓超出范圍:所有輸入電壓不應超過電源引腳電壓±300 mV,可在數字輸入串聯47Ω電阻解決過沖問題。

- 驅動高電容數據總線:輸出驅動電容過大可能影響動態性能,可緩沖數字數據輸出或在數字輸出添加12Ω - 27Ω串聯電阻。

- 使用不當的放大器:應選擇能夠快速響應輸入電壓尖峰的放大器,并使用單極RC濾波器確保放大器穩定性。

- 參考引腳驅動不足:確保驅動設備能為$VRT$和$VRB$提供足夠的電流,以保證參考引腳的穩定性。

- 時鐘信號問題:避免使用抖動過大的時鐘源,保持時鐘線短且遠離其他信號。

總結

ADC08B200是一款功能強大、性能優越的高速8位A/D轉換器。在設計應用時,我們需要充分考慮其電氣特性、引腳功能、時鐘與定時要求以及各種應用設計要點,以確保系統的穩定性和可靠性。希望本文能為電子工程師們在使用ADC08B200進行設計時提供有價值的參考。

你在使用ADC08B200的過程中遇到過哪些問題?又是如何解決的呢?歡迎在評論區分享你的經驗和見解。

-

緩沖器

+關注

關注

6文章

2234瀏覽量

48938 -

adc

+關注

關注

100文章

7528瀏覽量

556408 -

數字轉換器

+關注

關注

0文章

347瀏覽量

28804 -

輸入信號

+關注

關注

0文章

559瀏覽量

13195 -

PLL電路

+關注

關注

0文章

94瀏覽量

7109

發布評論請先 登錄

ADC08B200/ADC08B200Q,pdf datas

深入解析ADC08B3000:高性能8位3GSPS A/D轉換器的技術奧秘

ADC08B200:高速8位A/D轉換器的全方位解析

深入解析ADC08D500:高性能低功耗8位500 MSPS A/D轉換器

ADC08B200:高速8位A/D轉換器的設計與應用指南

ADC08B200:高速8位A/D轉換器的設計與應用指南

評論