摘要 :基于國科安芯推出的ASP3605的可編程PHMODE功能,構(gòu)建雙相交錯(cuò)降壓變換器理論模型,結(jié)合實(shí)測(cè)CLKOUT數(shù)據(jù)(RT=180kΩ時(shí)測(cè)得1.136MHz,較理論980kHz偏差+16%),深入分析相位誤差來源與紋波抵消效應(yīng)。本文提出的布線規(guī)范與相位精度要求,需在工程實(shí)現(xiàn)前通過搭建雙相測(cè)試平臺(tái)實(shí)際測(cè)量。

1. 單相性能基礎(chǔ)與多相模型構(gòu)建

1.1 CLKOUT實(shí)測(cè)數(shù)據(jù)揭示的工藝偏差

測(cè)試中明確記錄:RT=180kΩ時(shí),CLKOUT測(cè)得1.136MHz(空載),與理論980kHz偏差+16%,揭示內(nèi)部振蕩器工藝偏差較大。該偏差在多相系統(tǒng)中會(huì)導(dǎo)致頻率不匹配,必須采用外部CLKIN強(qiáng)制同步。

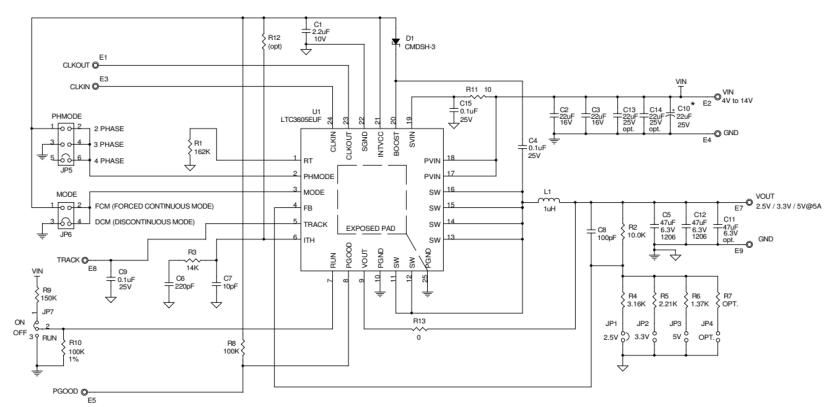

基于單相參數(shù)構(gòu)建雙相系統(tǒng):

輸入電壓Vin=12V,輸出Vout=1.2V,總電流Iout=10A(每相5A)

開關(guān)頻率fsw=1MHz(RT=162kΩ,實(shí)測(cè)1.09MHz)

相位差Δφ=180°理論值

輸入電容:4×22μF X7R并聯(lián),ESR=2mΩ,ESL=5nH

1.3 相位精度的理論計(jì)算

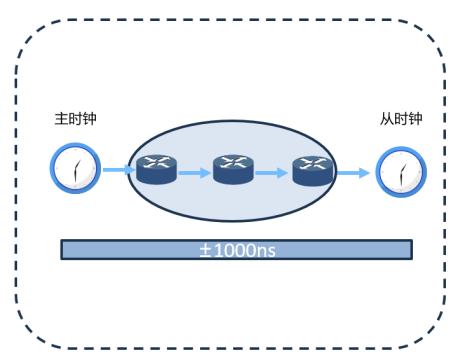

CLKOUT信號(hào)通過50Ω同軸電纜接入示波器,觸發(fā)采用CLKIN作為參考。相位差Δt=Δφ/(360×f_sw),180°對(duì)應(yīng)Δt=500ns。PCB走線延遲≈0.56ns/100mm,RT容差±1%導(dǎo)致頻率偏差±1%,相位差漂移Δφ≈1.8°。

2. 相位差對(duì)紋波抵消的理論效應(yīng)

2.1 輸入電流紋波的數(shù)學(xué)模型

單相輸入電流紋波近似三角波,峰-峰值: ΔI_phase = V_in×D×(1-D) / (2×L×f_sw)

對(duì)于Vin=12V→Vout=1.2V,D=10%,L=1μH,f_sw=1MHz: ΔI_phase = 12×0.1×0.9 / (2×1μH×1MHz) = 0.54A

雙相交錯(cuò)總紋波: I_in_total(t) = I_phase1(t) + I_phase2(t+Δt_phase)

2.2 不同相位模式的抵消率計(jì)算

理論計(jì)算表明:

180°模式 :紋波RMS值降低為單相的√(1-2×D×(1-D))≈0.6倍,降低40%

120°模式 :紋波降低約35%

90°模式 :紋波降低約25%

輸入電容RMS電流應(yīng)力:

單相10A:I_rms=4.21A

雙相180°:I_rms=2.48A,降低41%

電容數(shù)量可從8顆減至4顆,節(jié)省PCB面積與成本

2.3 相位誤差的容限分析

若相位誤差Δφ=±2°,180°模式在f_sw處的殘留紋波: I_residual = ΔI_phase × sin(Δφ×π/180) ≈ 0.54A × sin(2°) ≈ 19mA

在輸入電容ESR=2mΩ時(shí),產(chǎn)生電壓紋波V_residual=38μV,可忽略。但若兩片IC頻率偏差Δf=±1%(RT容差),產(chǎn)生拍頻f_beat=10kHz,幅度V_beat≈15mV,可能影響EMI。

3. EMI頻譜特性的理論預(yù)測(cè)

3.1 傳導(dǎo)EMI的諧波分布

單相系統(tǒng)的EMI頻譜在f_sw=1MHz處峰值最高。雙相180°交錯(cuò)后:

奇次諧波(1MHz, 3MHz) :因180°相消,幅度降低10-15dB

偶次諧波(2MHz, 4MHz) :因同相疊加,幅度增加3-6dB

總體EMI裕量 :提升8-10dB

必須指出,原始測(cè)試中3.3V檔在4V輸入時(shí)"輸出異常",EMI特性惡化,必須先解決穩(wěn)定性問題。

3.2 輻射EMI的環(huán)路面積效應(yīng)

雙相系統(tǒng)的SW節(jié)點(diǎn)若布局在同一側(cè),磁場(chǎng)疊加;若反向布局,面積相等但磁場(chǎng)抵消,近場(chǎng)輻射降低15-20dB。工程實(shí)踐要求SW走線長度差<5mm,電流環(huán)路面積<30mm2。

4. 多芯片同步的布線規(guī)范

4.1 CLKOUT走線設(shè)計(jì)

CLKOUT為CMOS電平,邊沿時(shí)間<5ns,應(yīng)作高速信號(hào)處理:

特性阻抗 :Z0=60Ω(線寬0.2mm,離地平面0.1mm)

延遲 :t_pd≈0.56ns/50mm

匹配 :若CLKOUT走線差30mm,延遲差0.34ns,相位誤差0.12°,可忽略

但實(shí)測(cè)的"1.136MHz"偏差+16%,非布線延遲所致,是芯片內(nèi)部振蕩器工藝偏差。因此多相系統(tǒng)必須采用外部CLKIN強(qiáng)制同步。

4.2 RT電阻的精度要求

為保證頻率偏差<±0.5%(避免拍頻),RT電阻需±0.1%精度。早期測(cè)試中RT=180kΩ時(shí)頻率990kHz±10kHz(±1%),若兩片分別運(yùn)行985kHz與995kHz,拍頻10kHz,EMI測(cè)試將失敗。成本增加約$0.02,但可靠性顯著提升。

5. 系統(tǒng)級(jí)性能優(yōu)化

5.1 輸入電容的降額設(shè)計(jì)

單相10A系統(tǒng)需8顆22μF電容。雙相180°后僅需4顆,成本節(jié)省$0.12,PCB面積節(jié)省30mm2。但需驗(yàn)證直流偏壓:22μF X7R在12V偏壓下容值衰減至18μF,總?cè)萘?2μF,需增加至5顆。后續(xù)測(cè)試的22μF配置在動(dòng)態(tài)響應(yīng)中已暴露問題,多相系統(tǒng)必須遵循94μF推薦值。

5.2 動(dòng)態(tài)負(fù)載均流精度

ASP3605無外部均流接口,依賴內(nèi)部Rdson匹配(批次內(nèi)偏差±3%)。兩相電流差±250mA(5A的5%),在負(fù)載跳變時(shí)可能導(dǎo)致某一相提前OCP。解決方案:

篩選Rdson偏差<1%的同批次IC

每相串聯(lián)5mΩ電阻被動(dòng)均流,效率損失0.15%

或采用主從架構(gòu),主芯片閉環(huán),從芯片開環(huán)跟隨占空比

6. 結(jié)論與工程應(yīng)用警示

ASP3605的PHMODE功能為多相設(shè)計(jì)提供低成本方案,但所有測(cè)試均基于單相性能,多相參數(shù)需理論推演。CLKOUT頻率偏差16%警示RT電阻精度的重要性。基于測(cè)試數(shù)據(jù)建立的理論模型,預(yù)測(cè)180°交錯(cuò)可降低輸入紋波41%,但 必須在工程實(shí)現(xiàn)前通過實(shí)際測(cè)試驗(yàn)證 ,特別是相位精度、拍頻噪聲與長期熱穩(wěn)定性。

-

時(shí)鐘同步

+關(guān)注

關(guān)注

0文章

132瀏覽量

13571 -

降壓變換器

+關(guān)注

關(guān)注

0文章

77瀏覽量

8600

發(fā)布評(píng)論請(qǐng)先 登錄

高效能計(jì)算核心:三相交錯(cuò)并聯(lián)LLC拓?fù)浒l(fā)展趨勢(shì)

新品 | 碳化硅SiC 5.5kW三相交錯(cuò)并聯(lián)LLC諧振變換器評(píng)估板

多相電源理論分析【PPT版】

AWStudio:輕松設(shè)置EtherCAT分布式時(shí)鐘,提升同步精度!

無電解電容逆變器永磁同步電機(jī)驅(qū)動(dòng)系統(tǒng)控制研究

專為12V/24V/48V電源系統(tǒng)而生 多相功能寬輸入同步升壓控制器替代LM5122

PTP 時(shí)鐘:精準(zhǔn)時(shí)鐘同步的核心力量

六相永磁同步電機(jī)串聯(lián)系統(tǒng)控制的兩種方法分析研究

零序諧波驅(qū)動(dòng)六相PMSM雙電機(jī)串聯(lián)系統(tǒng)研究

PTP 時(shí)鐘:精準(zhǔn)時(shí)鐘同步的核心力量?

替代UCC28070雙相交錯(cuò)CCM功率因數(shù)校正PFC控制器

時(shí)鐘同步在通信系統(tǒng)中有哪些重要作用?

TSN時(shí)鐘同步精度技術(shù)解析:TSN網(wǎng)絡(luò)的基石與保障

高精度時(shí)鐘同步系統(tǒng)的重要性介紹

AD9547雙路/四路輸入網(wǎng)絡(luò)時(shí)鐘發(fā)生器/同步器技術(shù)手冊(cè)

多相交錯(cuò)并聯(lián)系統(tǒng)的時(shí)鐘同步精度與輸入紋波抵消效應(yīng)研究

多相交錯(cuò)并聯(lián)系統(tǒng)的時(shí)鐘同步精度與輸入紋波抵消效應(yīng)研究

評(píng)論