【博主簡介】本人“愛在七夕時”,系一名半導體行業質量管理從業者,旨在業余時間不定期的分享半導體行業中的:產品質量、失效分析、可靠性分析和產品基礎應用等相關知識。常言:真知不問出處,所分享的內容如有雷同或是不當之處,還請大家海涵。當前在各網絡平臺上均以此昵稱為ID跟大家一起交流學習!

隨著電子技術在工業、交通、消費、醫療等領域的蓬勃發展,當代社會對電力電子設備的要求也越來越高,功率半導體就是影響這些電力電子設備成本和效率的直接因素之一。自從二十世紀五十年代真空管被固態器件代替以來,以硅(Si)材料為主的功率半導體器件就一直扮演著重要的角色,功率MOSFET是其中最典型的代表。

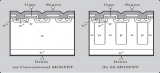

MOSFET的中文全稱是金屬-氧化物半導體場效應晶體管。它的基本機構如下圖所示:P型半導體作為襯底,其兩端各有一個重摻雜N+,分別作為源極(SOURCE,S)和漏極(DRAIN, D),在P型半導體表面涂上一層sio2絕緣層并在絕緣層上引出一端,作為柵極(GATE, G)。

當柵源兩端電壓為零時,不論漏源之間的電壓是正偏還是反偏,半導體中始終有反向偏置的PN結致使器件無法導通。當柵源兩端加上一個正向電壓且VGS上升到閾值時,P區形成一個反型層,為柵極和漏極之間創造了通路,此時MOS管導通。

為了增加MOS的耐壓能力,常在P區和漏極的N+之間增加一段漂移區,承受器件在反向耐壓狀態下的高電壓。漂移區的摻雜濃度也決定了器件的大部分電阻,此即為LDMOS的基本結構。

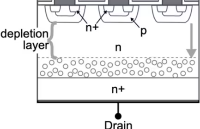

除了橫向結構以外,還存在一種縱向結構模式,稱為VDMOS。在VDMOS結構中,漏端和源端、柵端不在同一平面(如下圖所示)。但與LDMOS相同的是,VDMOS的耐壓和導通電阻同樣主要由漂移區決定。所以提高漂移區摻雜濃度自然成為降低功率MOS導通電阻的方法之一。

在這樣的背景下,為了得到大功率低損耗的功率器件,有學者提出,可以通過設置交替的PN條來提高器件漂移區的摻雜濃度進而實現低導通電阻,此即SUPER JUNCTION MOSFET(SJ MOS)。所以以下就是今天我要跟大家分享的關于半導體超結MOSFET及其發展的相關知識,希望有興趣的朋友可以一起多交流學習。

一、超結MOSFET的定義

半導體超級結 MOSFET (SJ-MOS),英文名稱:Super Junction MOSFET。為了解決額定電壓提高而導通電阻增加的問題,超結結構MOSFET在D端和S端排列多個垂直pn結的結構,其結果是在保持高電壓的同時實現了低導通電阻。超級結的存在大大突破了硅的理論極限,而且額定電壓越高,導通電阻的下降越明顯。

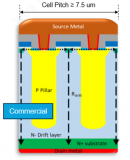

以下圖為例,超結在S端和D端增加了長長的柱子,形成垂直的PN結,交替排列。N層和P層在漂移層中設置垂直溝槽,當施加電壓時耗盡層水平擴展,很快合并形成與溝槽深度相等的耗盡層。耗盡層僅擴展至溝槽間距的一半,因此形成厚度等于溝槽深度的耗盡層。耗盡層的膨脹小且良好,允許漂移層雜質濃度增加約5倍,從而可以降低RDS(ON)。

超級結的性能提升方法:使溝槽和溝槽間距盡可能小和深。SJ-MOS 可以設計為具有較低電阻的 N 層,從而實現低導通電阻產品。

超級結存在的問題:本質上超級結MOSFET比平面MOSFET具有更大的pn結面積,因此trr比平面MOSFET快,但更大的irr流動。內部二極管的反向電流irr和反向恢復時間trr會影響晶體管關斷開關特性。

二、超結MOSFET的結構

高壓的功率MOSFET的外延層對總的導通電阻起主導作用,要想保證高壓的功率MOSFET具有足夠的擊穿電壓,同時,降低導通電阻,最直觀的方法就是:在器件關斷時,讓低摻雜的外延層保證要求的耐壓等級,同時,在器件導通時,形成一個高摻雜N+區,作為功率MOSFET導通時的電流通路,也就是將反向阻斷電壓與導通電阻功能分開,分別設計在不同的區域,就可以實現上述的要求。

基于超結SuperJunction的內建橫向電場的高壓功率MOSFET就是基本這種想法設計出的一種新型器件。內建橫向電場的高壓MOSFET的剖面結構及高阻斷電壓低導通電阻的示意圖如圖3所示。Infineon最先將這種結構生產出來,并為這種結構的MOSFET設計了一種商標CoolMOS,這種結構從學術上來說,通常稱為超結型功率MOSFET。

垂直導電N+區夾在兩邊的P區中間,當MOS關斷時,形成兩個反向偏置的PN結:P和垂直導電N+、P+和外延epi層N-。柵極下面的的P區不能形成反型層產生導電溝道,P和垂直導電N+形成PN結反向偏置,PN結耗盡層增大,并建立橫向水平電場;同時,P+和外延層N-形成PN結也是反向偏置形,產生寬的耗盡層,并建立垂直電場。

由于垂直導電N+區摻雜濃度高于外延區N-的摻雜濃度,而且垂直導電N+區兩邊都產生橫向水平電場,這樣垂直導電的N+區整個區域基本上全部都變成耗盡層,即由N+變為N-,這樣的耗盡層具有非常高的縱向的阻斷電壓,因此,器件的耐壓就取決于高摻雜P+區與低摻雜外延層N-區的耐壓。

當MOS導通時,柵極和源極的電場將柵極下的P區反型,在柵極下面的P區產生N型導電溝道,同時,源極區的電子通過導電溝道進入垂直的N+區,中和N+區的正電荷空穴,從而恢復被耗盡的N+型特性,因此導電溝道形成,垂直N+區摻雜濃度高,具有較低的電阻率,因此導通電阻低。

比較平面結構和溝槽結構的功率MOSFET,可以發現,超結型結構實際是綜合了平面型和溝槽型結構兩者的特點,是在平面型結構中開一個低阻抗電流通路的溝槽,因此具有平面型結構的高耐壓和溝槽型結構低電阻的特性。

內建橫向電場的高壓超結型結構與平面型結構相比較,同樣面積的硅片可以設計更低的導通電阻,因此具有更大的額定電流值和雪崩能量。

由于要開出N+溝槽,它的生產工藝比較復雜,目前N+溝槽主要有兩種方法直接制作:通過一層一層的外延生長得到N+溝槽和直接開溝槽。前者工藝相對的容易控制,但工藝的程序多,成本高;后者成本低,但不容易保證溝槽內性能的一致性。

三、超結MOSFET的工作原理

1、關斷狀態

從下圖中可以看到,垂直導電N+區夾在兩邊的P區中間,當MOS關斷時,也就是G極的電壓為0時,橫向形成兩個反向偏置的PN結:P和垂直導電N+、P+和外延epi層N-。

柵極下面的的P區不能形成反型層產生導電溝道,左邊P和中間垂直導電N+形成PN結反向偏置,右邊P和中間垂直導電N+形成PN結反向偏置,PN結耗盡層增大,并建立橫向水平電場。

當中間的N+的滲雜濃度和寬度控制得合適,就可以將中間的N+完全耗盡,如下圖b所示,這樣在中間的N+就沒有自由電荷,相當于本征半導體,中間的橫向電場極高,只有外部電壓大于內部的橫向電場,才能將此區域擊穿,所以,這個區域的耐壓極高,遠大于外延層的耐壓,功率MOSFET管的耐壓主要由外延層來決定。

注意到,P+和外延層N-形成PN結也是反向偏置形,有利于產生更寬的耗盡層,增加垂直電場。

2、開通狀態

當G極加上驅動電壓時,在G極的表面將積累正電荷,同時,吸引P區的電子到表面,將P區表面空穴中和,在柵極下面形成耗盡層,如圖5示。

隨著G極的電壓提高,柵極表面正電荷增強,進一步吸引P區電子到表面,這樣,在G極下面的P型的溝道區中,積累負電荷,形成N型的反型層,同時,由于更多負電荷在P型表面積累,一些負電荷將擴散進入原來完全耗盡的垂直的 N+,橫向的耗盡層越來越減小,橫向的電場也越來越小。

G極的電壓進一步提高,P區更寬范圍形成N型的反型層,最后,N+區域回到原來的高滲雜的狀態,這樣,就形成的低導通電阻的電流路徑,如下圖所示。

四、傳統MOS管的瓶頸

下面,我就跟大家分享一下傳統MOS管的瓶頸:

五、超結MOSFET的缺點和改進

當然,超結理論在現實應用中也并不是完美的,那具體有哪些缺點和可以改善的地方呢?

六、超結MOSFET的優點

超結MOSFET與傳統的VDMOS相比,具有導通電阻低、開關速度快、芯片體積小、發熱低的特點。一般來說,相同電流、電壓規格的超結MOSFET導通電阻僅為傳統VDMOS的一半左右,器件開通和關斷速度較傳統VDMOS下降30%以上。這些特點可以使超結MOSFET在替代傳統VDMOS時具有更好的溫升和效率表現,一般來說,使用超結MOSFET后,電源效率可以上升1~2百分點。同時超結MOSFET也完全可以與驅動IC一起進行集成封裝,大幅度降低產品體積。

超級結具有更小的結電容,對超級結器件而言,電阻的減小會帶來明顯的好處,例如在相同RDS(on)下的更低導通損耗或更小管芯。另外,芯片面積的減小會導致更低的結電容以及柵極和輸出電荷,這可減小動態損耗。在低壓溝槽式或平面式MOS管中,通常需要考慮以更高結電容為讓步條件來降低RDS(on)。在超級結技術情況下,讓步程度是最小的。電荷平衡機制可同時減小RDS(on)和器件結電容,使之成為一種雙贏解決方案。

七、超結MOSFET的主要作用

1、降低導通電阻

相較于傳統VDMOS,相同電流、電壓規格的超結MOSFET的導通電阻僅為傳統VDMOS的一半左右。這得益于其特殊的芯片內部結構設計,使得在相同的芯片面積下,超結MOS的內阻更低。

2、提高開關速度

超結MOSFET的開通和關斷速度較傳統VDMOS快30%以上,這有助于降低動態損耗,提高電源系統的效率。

3、減小芯片體積

由于超結MOS的內阻低,可以在保證性能的同時減小芯片面積,從而有利于設計更小體積的電源電路,降低產品成本。

4、降低發熱

較低的導通電阻和開關速度意味著更低的損耗,進而減少了發熱量,這對于對溫度要求高的產品如充電頭等尤為重要。

5、提升效率

使用超結MOSFET后,電源效率可以上升1~2個百分點,這對于提高整體能源利用效率具有重要意義。

6、易于集成封裝

超結MOSFET可以與驅動IC一起進行集成封裝,進一步降低產品體積和成本。

7、適用領域廣泛

超結MOSFET以其優異的性能被廣泛應用于電源、電機

寫在最后面的話

超結MOS作為一種創新的半導體器件技術,通過其獨特的超結結構設計,在降低導通電阻、提高開關速度、減小芯片體積、降低發熱和提升效率等方面展現出顯著優勢。這些特點使得超結MOS在高壓、高頻、高效率的電力電子應用中具有廣闊的前景。

免責聲明

【我們尊重原創,也注重分享。文中的文字、圖片版權歸原作者所有,轉載目的在于分享更多信息,不代表本號立場,如有侵犯您的權益請及時私信聯系,我們將第一時間跟蹤核實并作處理,謝謝!】

審核編輯 黃宇

-

MOSFET

+關注

關注

151文章

10298瀏覽量

234577 -

半導體

+關注

關注

339文章

31085瀏覽量

265793

發布評論請先 登錄

龍騰半導體超結MOSFET重新定義AI算力電源

芯源的MOSFET采用什么工藝

功率半導體“超結MOS”基礎知識的詳解;

龍騰半導體650V 99mΩ超結MOSFET重磅發布

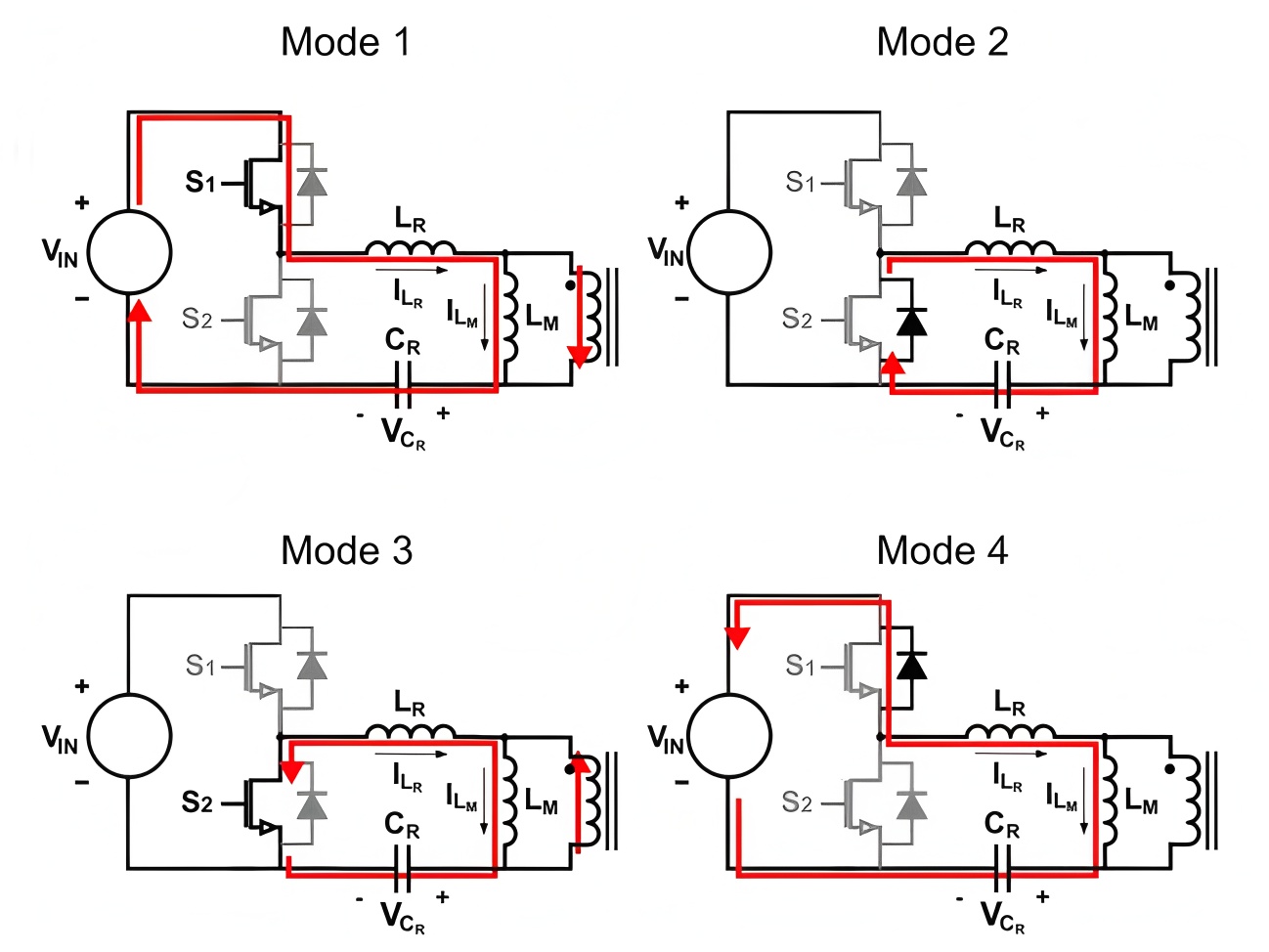

SiC碳化硅MOSFET在LLC應用中取代超結MOSFET的優勢和邏輯

現代集成電路半導體器件

新品 | 650V CoolMOS? 8超結 (SJ) MOSFET

浮思特 | 一文讀懂何為超結MOSFET (Super Junction MOSFET)?

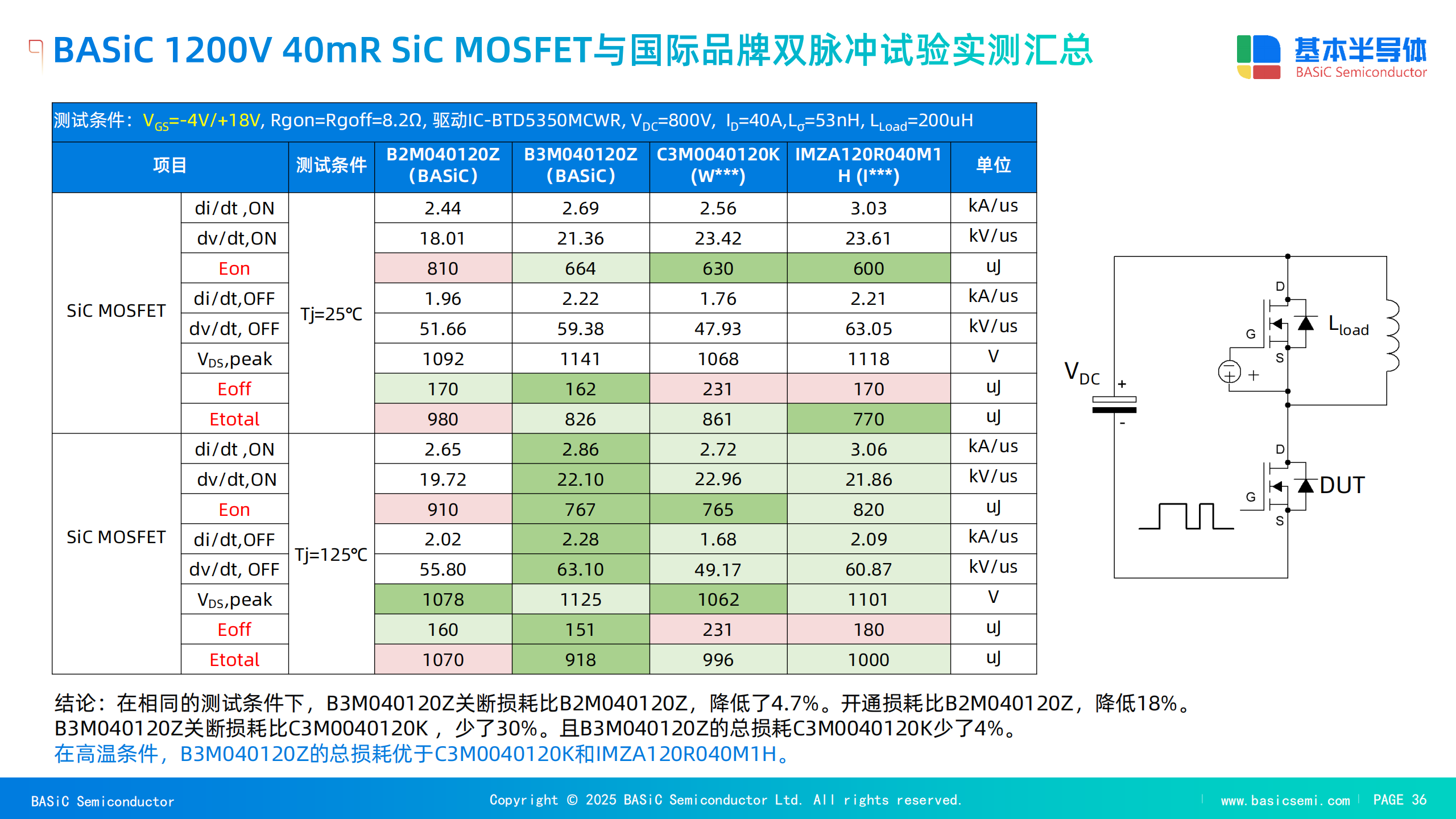

基本半導體碳化硅 MOSFET 的 Eoff 特性及其在電力電子領域的應用

瑞能半導體第三代超結MOSFET技術解析(1)

伯恩半導體新品推薦 | 超結MOS管在TV電視上的應用

新潔能Gen.4超結MOSFET 800V和900V產品介紹

關于半導體“超結MOSFET”及其發展的詳解;

關于半導體“超結MOSFET”及其發展的詳解;

評論