在當(dāng)今的電子設(shè)計(jì)領(lǐng)域,高速、低功耗的模數(shù)轉(zhuǎn)換器(ADC)需求日益增長(zhǎng)。TI的ADC08D1500就是這樣一款性能卓越的產(chǎn)品,它能在高速采樣的同時(shí)保持低功耗,為眾多應(yīng)用場(chǎng)景提供了理想的解決方案。今天,咱們就來深入剖析一下這款A(yù)DC。

文件下載:adc08d1500.pdf

一、核心特性概覽

ADC08D1500具有諸多令人矚目的特性。它采用內(nèi)部采樣保持電路,單+1.9V ±0.1V供電,支持SDR或DDR輸出時(shí)鐘模式,還具備交錯(cuò)模式以實(shí)現(xiàn)2倍采樣率,能確保無丟失碼,擁有串行接口用于擴(kuò)展控制,可精細(xì)調(diào)整輸入滿量程范圍和偏移,采用占空比校正的采樣時(shí)鐘。這些特性使得它在不同的應(yīng)用場(chǎng)景中都能游刃有余。

二、關(guān)鍵參數(shù)解讀

2.1 分辨率與轉(zhuǎn)換速率

ADC08D1500的分辨率為8位,最大轉(zhuǎn)換速率可達(dá)1.5 GSPS(典型值),誤差率低至$10^{-18}$,在748 MHz輸入時(shí)有效位數(shù)(ENOB)可達(dá)7.25位(典型值),差分非線性(DNL)為±0.15 LSB(典型值)。這些參數(shù)保證了其在高速轉(zhuǎn)換的同時(shí),還能保持較高的精度。

2.2 功耗表現(xiàn)

在功耗方面,它表現(xiàn)出色。正常工作時(shí)功耗為1.8 W(典型值),進(jìn)入掉電模式后功耗可降至3.5 mW(典型值)。這種低功耗特性對(duì)于一些對(duì)功耗敏感的應(yīng)用場(chǎng)景,如電池供電設(shè)備,具有重要意義。

三、功能特性詳解

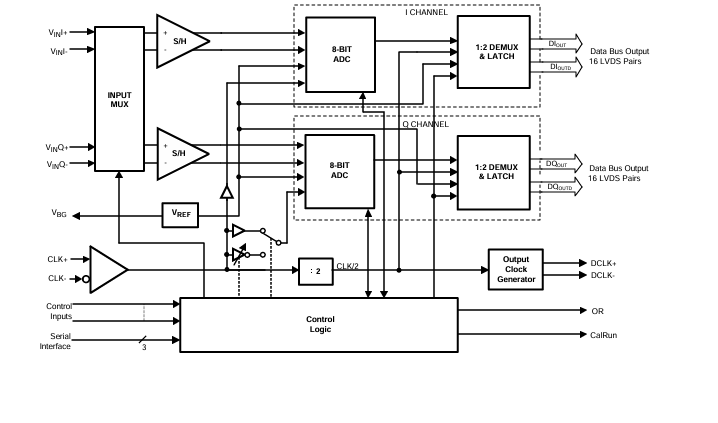

3.1 獨(dú)特架構(gòu)與高性能

ADC08D1500采用校準(zhǔn)折疊插值架構(gòu),實(shí)現(xiàn)了7.4有效位。折疊放大器的使用大幅減少了比較器數(shù)量和功耗,插值技術(shù)減少了前端放大器需求,降低了輸入信號(hào)負(fù)載和功耗。片上校準(zhǔn)還減少了折疊架構(gòu)常見的積分非線性(INL)彎曲。這些使得它成為一款高速、高性能、低功耗的轉(zhuǎn)換器。

3.2 輸入與輸出處理

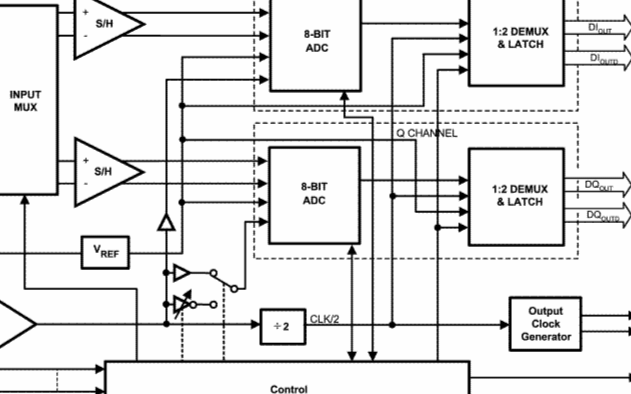

模擬輸入信號(hào)在轉(zhuǎn)換器輸入電壓范圍內(nèi)可被數(shù)字化為8位,采樣速度典型為200 MSPS至1.7 GSPS。當(dāng)差分輸入電壓低于負(fù)滿量程時(shí),輸出字全為零;高于正滿量程時(shí),輸出字全為一。任一通道出現(xiàn)這些情況都會(huì)激活超出范圍(OR)輸出。每個(gè)轉(zhuǎn)換器都有1:2解復(fù)用器,將數(shù)據(jù)輸出到兩個(gè)LVDS總線,用戶需對(duì)這些數(shù)據(jù)進(jìn)行交織以獲得完整轉(zhuǎn)換速率的輸出字。輸出電平可選擇正常或降低,降低電平可節(jié)省功耗,但可能影響數(shù)據(jù)捕獲。

3.3 自校準(zhǔn)功能

自校準(zhǔn)是ADC08D1500的重要特性之一。上電時(shí)會(huì)自動(dòng)進(jìn)行自校準(zhǔn),也可由用戶按需觸發(fā)。校準(zhǔn)可微調(diào)100Ω模擬輸入差分終端電阻,最小化滿量程誤差、偏移誤差、DNL和INL,從而最大化信噪比(SNR)、總諧波失真(THD)、信噪失真比(SINAD)和ENOB。校準(zhǔn)過程還會(huì)設(shè)置內(nèi)部偏置電流。需要注意的是,自校準(zhǔn)必須在上電時(shí)運(yùn)行,且在FSR引腳狀態(tài)改變時(shí)也需重新運(yùn)行。為獲得最佳性能,建議在上電20秒后或環(huán)境溫度顯著變化時(shí)進(jìn)行自校準(zhǔn)。校準(zhǔn)期間,輸入終端電阻會(huì)被調(diào)整為$R{EXT} / 33$($R{EXT}$必須為3300Ω±0.1%),所有輸出數(shù)據(jù)和OR輸出無效,所有時(shí)鐘會(huì)暫停以減少噪聲。CalRun輸出在校準(zhǔn)期間為高電平。

3.4 輸入采集與控制模式

數(shù)據(jù)在CLK+的下降沿被采集,DI和DQ輸出總線在13個(gè)輸入時(shí)鐘周期后、DId和DQd輸出總線在14個(gè)輸入時(shí)鐘周期后可獲得數(shù)字?jǐn)?shù)據(jù)。ADC08D1500只要有輸入時(shí)鐘信號(hào)就會(huì)進(jìn)行轉(zhuǎn)換。它提供多種控制模式,包括正常控制模式和擴(kuò)展控制模式。在擴(kuò)展控制模式下,可通過串行接口訪問配置寄存器,實(shí)現(xiàn)更多功能的靈活配置,如SDR或DDR模式選擇、DDR時(shí)鐘相位選擇、SDR數(shù)據(jù)轉(zhuǎn)換邊緣選擇、LVDS輸出電平選擇、上電校準(zhǔn)延遲設(shè)置、滿量程范圍調(diào)整和輸入偏移調(diào)整等。

3.5 時(shí)鐘與采樣模式

ADC08D1500需要交流耦合的差分時(shí)鐘信號(hào)驅(qū)動(dòng),提供SDR或DDR輸出時(shí)鐘模式選擇。它還可使用占空比校正的時(shí)鐘接收器,默認(rèn)啟用該功能,允許使用占空比為80/20%的信號(hào)源進(jìn)行時(shí)鐘驅(qū)動(dòng)。雙邊緣采樣(DES)模式下,一個(gè)輸入可被兩個(gè)ADC采樣,采樣率翻倍至3 GSPS(輸入時(shí)鐘為1.5 GHz時(shí))。輸出數(shù)據(jù)按DQd、DId、DQ、DI的順序輸出。非擴(kuò)展模式下只有“I”輸入可用于DES模式,擴(kuò)展模式下用戶可選擇采樣輸入。此外,它還具備自動(dòng)時(shí)鐘相位背景校準(zhǔn)功能,可自動(dòng)連續(xù)調(diào)整I和Q通道的時(shí)鐘相位,提供最佳的DES ENOB性能。

3.6 LVDS輸出與電源管理

LVDS輸出包括數(shù)據(jù)輸出和DCLK,輸出電流源在OutV輸入為高時(shí)提供3 mA電流,為低時(shí)提供2.2 mA電流。短LVDS線路和低噪聲系統(tǒng)可選擇低輸出電平以節(jié)省功耗,長(zhǎng)線路或高噪聲系統(tǒng)則應(yīng)選擇高輸出電平。電源管理方面,PD引腳為高時(shí)設(shè)備進(jìn)入掉電模式,數(shù)據(jù)輸出引腳呈高阻態(tài),功耗降至最低;PDQ引腳為高時(shí),“Q”通道掉電,“I”通道保持活動(dòng)。需要注意的是,掉電時(shí)若正在進(jìn)行校準(zhǔn),設(shè)備會(huì)在校準(zhǔn)完成后才進(jìn)入掉電狀態(tài);若上電時(shí)PD已為高,設(shè)備需等PD變低才開始校準(zhǔn);掉電狀態(tài)下手動(dòng)校準(zhǔn)請(qǐng)求無效。

四、多ADC同步與應(yīng)用信息

4.1 多ADC同步

ADC08D1500具備精確重置采樣時(shí)鐘輸入與DCLK輸出關(guān)系的能力,通過用戶提供的DCLK_RST脈沖,可使多個(gè)ADC的DCLK和數(shù)據(jù)輸出在共享CLK輸入下同時(shí)轉(zhuǎn)換。DCLK_RST信號(hào)需滿足一定的時(shí)序要求,且不能在校準(zhǔn)期間置高,否則可能導(dǎo)致數(shù)字電路出現(xiàn)毛刺,影響校準(zhǔn)結(jié)果。

4.2 應(yīng)用信息

4.2.1 參考電壓

ADC08D1500的參考電壓源自1.254V帶隙參考,緩沖版本通過引腳31提供給用戶。該輸出可提供±100 μA電流,若需要更大電流,需進(jìn)行緩沖處理。內(nèi)部帶隙參考電壓由FSR引腳決定,無外部參考電壓接口,但可在擴(kuò)展控制模式下通過配置寄存器調(diào)整滿量程輸入電壓。此外,引腳$V_{BG}$還可用于提高LVDS輸出的共模電壓。

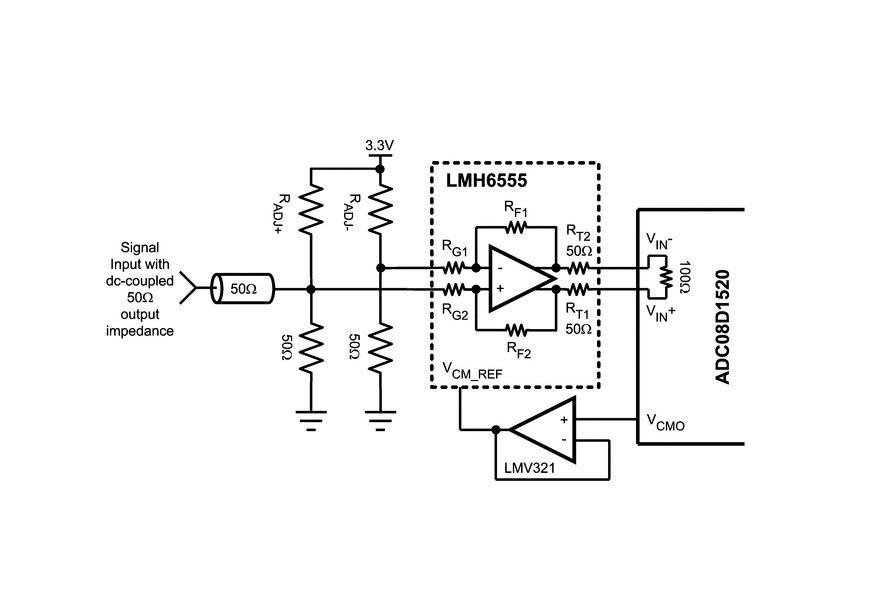

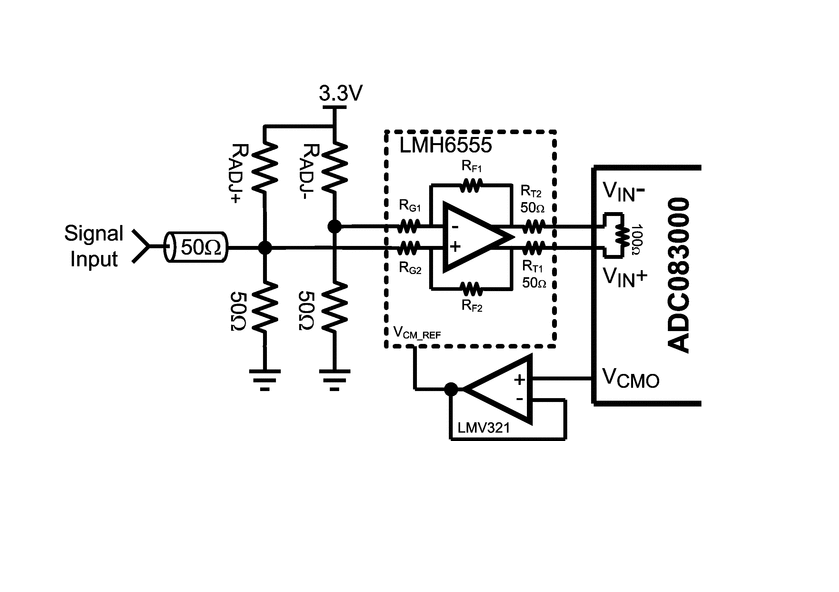

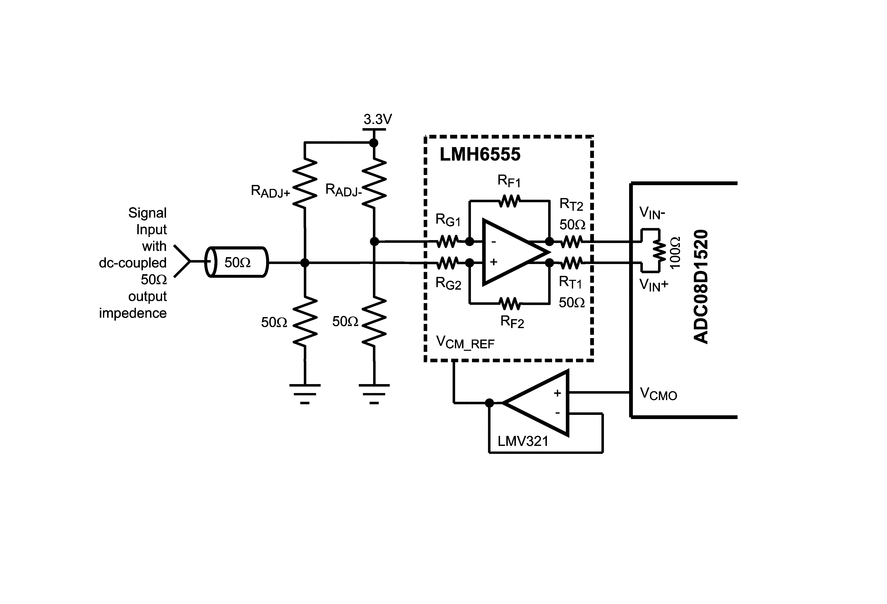

4.2.2 模擬輸入

模擬輸入為差分輸入,可采用交流或直流耦合方式。正常模式下,通過FSR引腳選擇滿量程輸入范圍;擴(kuò)展控制模式下,可通過串行接口編程FullScale Voltage Adjust寄存器來調(diào)整。輸入信號(hào)需保持共模電壓在$V{CMO}$的±50 mV范圍內(nèi),以確保良好的滿量程失真性能。未使用的輸入通道在交流耦合時(shí)應(yīng)浮空,直流耦合時(shí)應(yīng)連接到$V{CMO}$電壓。對(duì)于單端輸入信號(hào),可通過合適的巴倫變壓器或LMH6555進(jìn)行轉(zhuǎn)換。

4.2.3 時(shí)鐘輸入

ADC08D1500采用差分LVDS時(shí)鐘輸入,需交流耦合的差分時(shí)鐘信號(hào)驅(qū)動(dòng)。雖然測(cè)試時(shí)使用1.5 GHz差分時(shí)鐘,但在規(guī)定的輸入時(shí)鐘頻率范圍內(nèi)通常也能正常工作。時(shí)鐘輸入內(nèi)部有終端和偏置,輸入時(shí)鐘信號(hào)需電容耦合。為確保設(shè)備可靠性和壽命,應(yīng)避免在超出規(guī)定環(huán)境溫度下以高采樣率運(yùn)行,同時(shí)要注意熱管理。輸入時(shí)鐘電平應(yīng)在規(guī)定范圍內(nèi),過高可能導(dǎo)致輸入偏移電壓變化,影響轉(zhuǎn)換結(jié)果。

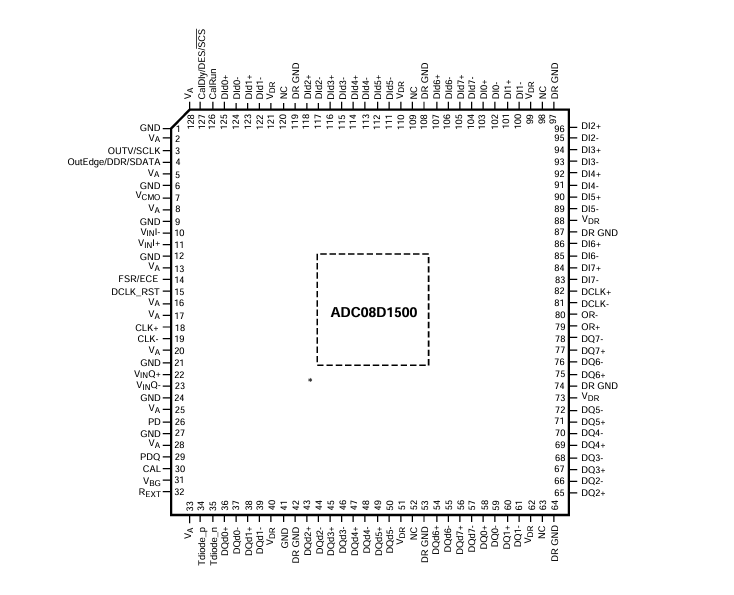

4.2.4 控制引腳

六個(gè)控制引腳為ADC08D1500的操作提供了豐富的可能性,包括滿量程輸入范圍設(shè)置、自校準(zhǔn)、校準(zhǔn)延遲、輸出邊緣同步選擇、LVDS輸出電平選擇和掉電功能。這些引腳的合理設(shè)置對(duì)于實(shí)現(xiàn)設(shè)備的最佳性能至關(guān)重要。

4.2.5 數(shù)字輸出

ADC08D1500將每個(gè)ADC的輸出數(shù)據(jù)解復(fù)用至兩個(gè)LVDS總線,每個(gè)總線的字速率為ADC輸入時(shí)鐘速率的一半,用戶需對(duì)這些數(shù)據(jù)進(jìn)行復(fù)用。可選擇單數(shù)據(jù)速率(SDR)或雙數(shù)據(jù)速率(DDR)模式,DDR模式下數(shù)據(jù)在DCLK的兩個(gè)邊緣輸出,DCLK頻率為輸入時(shí)鐘頻率的1/4。輸出格式為偏移二進(jìn)制,滿量程輸入時(shí)輸出全為1或全為0,輸入相等時(shí)輸出代碼在127和128之間變化。

4.2.6 電源考慮

為防止電源噪聲影響ADC性能,需對(duì)電源進(jìn)行適當(dāng)旁路處理,在ADC電源引腳附近放置33 μF電容和0.1 μF電容。若使用同一電源為$V{A}$和$V{DR}$供電,建議在兩者之間使用鐵氧體磁珠。ADC應(yīng)使用模擬電路電源或?qū)S秒娫矗苊馐褂脭?shù)字電路電源。供電電壓為1.9V ±0.1V,過高電壓可能縮短設(shè)備壽命。所有引腳電壓不應(yīng)超過電源電壓或低于地電壓150 mV,上電和掉電時(shí)需注意電源順序,可采用合適的電路提供過沖保護(hù)。若上電時(shí)無輸入時(shí)鐘信號(hào),設(shè)備電流可能較低,時(shí)鐘建立后電流恢復(fù)正常。

4.2.7 熱管理

盡管ADC08D1500在低功耗下能實(shí)現(xiàn)高速性能,但仍需關(guān)注熱管理。為保證可靠性,芯片溫度應(yīng)控制在130°C以下。器件內(nèi)置熱二極管用于溫度測(cè)量,但未進(jìn)行特性表征,無法提供溫度測(cè)量精度信息。建議將器件暴露焊盤焊接到PCB的熱焊盤上,以實(shí)現(xiàn)最佳散熱和電氣接地性能。可在PCB另一側(cè)設(shè)置銅面積和熱過孔,將熱量傳導(dǎo)至另一側(cè)進(jìn)行散熱。若要監(jiān)測(cè)芯片溫度,可在熱過孔附近安裝溫度傳感器,但需考慮熱梯度。

4.2.8 布局與接地

正確的接地和信號(hào)布線對(duì)于確保準(zhǔn)確轉(zhuǎn)換至關(guān)重要。建議使用單一接地平面,避免將接地平面分為模擬和數(shù)字區(qū)域。模擬和數(shù)字電路應(yīng)分開布局,避免相互干擾。輸入時(shí)鐘線應(yīng)與其他線路隔離,避免交叉。模擬輸入應(yīng)遠(yuǎn)離噪聲信號(hào)跡線,外部元件應(yīng)連接到干凈的模擬接地平面。

4.2.9 動(dòng)態(tài)性能

ADC08D1500經(jīng)過交流測(cè)試,動(dòng)態(tài)性能有明確規(guī)定。為滿足規(guī)格要求并避免抖動(dòng)噪聲,驅(qū)動(dòng)CLK輸入的時(shí)鐘源應(yīng)具有低均方根抖動(dòng)。輸入時(shí)鐘線應(yīng)盡量短,遠(yuǎn)離其他信號(hào),并按傳輸線處理。將器件背面暴露焊盤良好接地可獲得最佳動(dòng)態(tài)性能。

4.2.10 串行接口使用

ADC08D1500可在非擴(kuò)展控制模式或擴(kuò)展控制模式下運(yùn)行。非擴(kuò)展控制模式通過引腳設(shè)置實(shí)現(xiàn)各種功能;擴(kuò)展控制模式下,引腳3、4和127分別用作串行時(shí)鐘(SCLK)、串行數(shù)據(jù)(SDATA)和串行接口芯片選擇(SCS),用戶可通過串行接口訪問配置寄存器來設(shè)置各種功能。

五、常見應(yīng)用誤區(qū)

在使用ADC08D1500時(shí),有一些常見的應(yīng)用誤區(qū)需要避免。比如在擴(kuò)展控制模式下,使用串行接口時(shí)要確保所有8個(gè)用戶寄存器都寫入默認(rèn)或所需值,首次寫入DES Enable寄存器時(shí)要加載默認(rèn)值。輸入電壓不能超過電源軌±150 mV,避免輸入過驅(qū)動(dòng)。直流耦合模式下,輸入共模電壓要保持在$V{CMO}$的±50 mV范圍內(nèi)。選擇驅(qū)動(dòng)模擬輸入的放大器時(shí)要注意其失真性能。不要試圖通過驅(qū)動(dòng)$V{BG}$引腳改變參考電壓。輸入時(shí)鐘電平要在規(guī)定范圍內(nèi),避免輸入時(shí)鐘抖動(dòng)過大、線路過長(zhǎng)或與其他信號(hào)耦合。同時(shí),要注意提供足夠的散熱措施,確保設(shè)備正常工作。

ADC08D1500是一款功能強(qiáng)大、性能卓越的ADC,但在使用過程中需要我們充分了解其特性和要求,避免常見的應(yīng)用誤區(qū),才能發(fā)揮出它的最佳性能,為我們的電子設(shè)計(jì)帶來更多的可能性。希望今天的分享能對(duì)大家有所幫助,如果你在使用過程中有任何問題,歡迎留言交流。

-

adc

+關(guān)注

關(guān)注

100文章

7511瀏覽量

555943 -

A/D轉(zhuǎn)換器

+關(guān)注

關(guān)注

1文章

177瀏覽量

11780 -

串行接口

+關(guān)注

關(guān)注

3文章

520瀏覽量

45221 -

模數(shù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

26文章

4013瀏覽量

130102

發(fā)布評(píng)論請(qǐng)先 登錄

分享一款不錯(cuò)的基于ADC08D1500和FPGA Vertex-5的采集系統(tǒng)設(shè)計(jì)方案

超高速轉(zhuǎn)換器ADC08xxxx系列的校準(zhǔn)

ADC08D1500,pdf datasheet (High

新型流水線實(shí)現(xiàn)高速低功耗ADC的原理及方法

基于FPGA和高速A/D轉(zhuǎn)換芯片ADC08D1500的相關(guān)系統(tǒng)設(shè)計(jì)

模數(shù)轉(zhuǎn)換器ADC08D1500的性能特點(diǎn)及應(yīng)用分析

ADC08D1500高性能CMOS模數(shù)轉(zhuǎn)換器規(guī)格書

ADC08D1500雙通道、低功耗、高性能CMOS模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

ADC10D1000/ADC10D1500低功耗ADC數(shù)據(jù)表

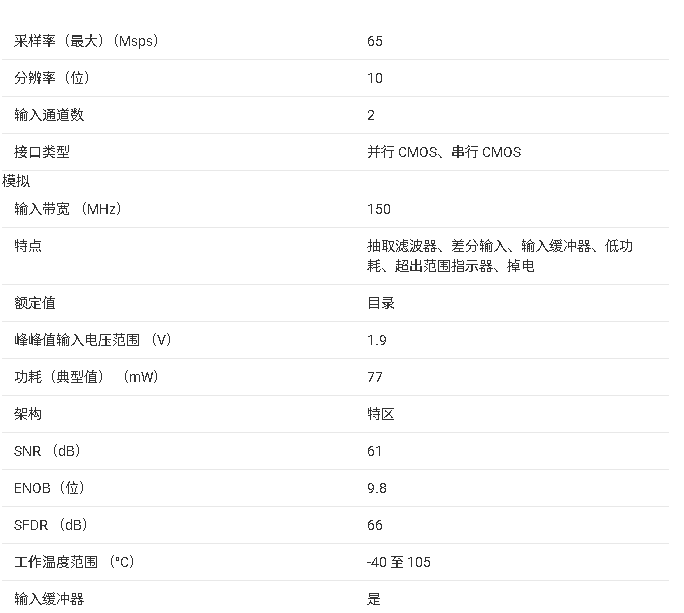

ADC3910D065 10 位高速低功耗 ADC 技術(shù)文檔總結(jié)

ADC08D1020:高性能8位A/D轉(zhuǎn)換器的深度解析

高速低功耗利器:ADC083000 8位3GSPS A/D轉(zhuǎn)換器深度解析

深入解析ADC08D1520:高性能8位ADC的卓越之選

深入解析ADC08D500:高性能低功耗8位500 MSPS A/D轉(zhuǎn)換器

ADC08D1000:高性能低功耗8位A/D轉(zhuǎn)換器的設(shè)計(jì)與應(yīng)用

高速低功耗利器:ADC08D1500 ADC深度解析

高速低功耗利器:ADC08D1500 ADC深度解析

評(píng)論