該DAC5681為16位1.0 GSPS數(shù)字轉模擬轉換器(DAC),支持寬帶LVDS 數(shù)據(jù)輸入和內部電壓參考。DAC5681提供了更優(yōu)越的線性和噪聲性能。

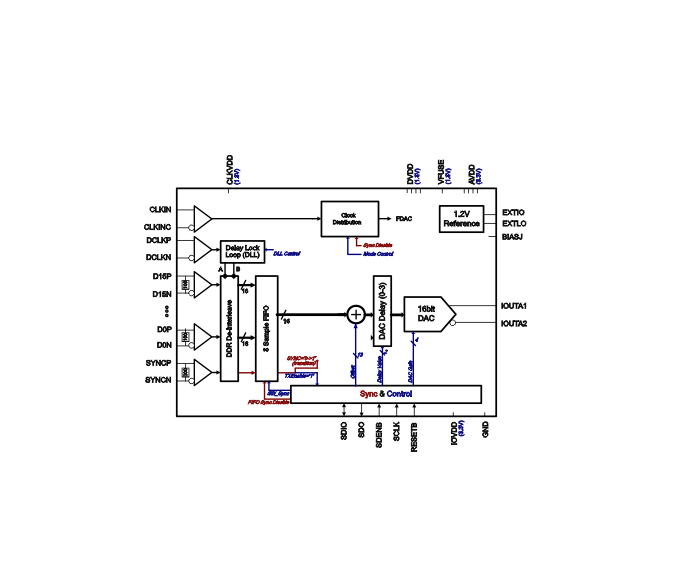

該DAC5681集成了帶片上終端的寬帶LVDS端口,提供完整的1.0 GSPS數(shù)據(jù)傳輸?shù)紻AC,電干擾比傳統(tǒng)CMOS數(shù)據(jù)接口更低。一個芯片 延遲鎖環(huán)(DLL)通過為LVDS輸入數(shù)據(jù)提供偏斜控制,簡化了LVDS的接口 時鐘。

*附件:dac5681.pdf

DAC5681的電流引導架構由分段電流陣列組成 下沉開關可將最高20mA的全功率電流導向互補輸出節(jié)點。一 精確的片上電壓參考是溫度補償?shù)模⑻峁┓€(wěn)定的1.2伏參考 電壓。可選地,也可以使用外部參考。

該DAC5681適用于工業(yè)溫度范圍——-40°C至85°C,并采用64針QFN封裝。該設備可通過引腳升級到家族的其他成員:DAC5681Z和DAC5682Z。單通道DAC5681Z和雙通道DAC5682Z都提供可選的2倍/4倍插值和時鐘倍增PLL。

特性

- 16位數(shù)模轉換器(DAC)

- 1.0 GSPS更新速率

- 16位寬帶輸入LVDS數(shù)據(jù)總線

- 8 樣本輸入FIFO

- 片上延遲鎖環(huán)

- 高性能

- 芯片1.2V參考

- 差分可擴展輸出:2至20毫安

- 封裝:64針9針 × 9毫米QFN

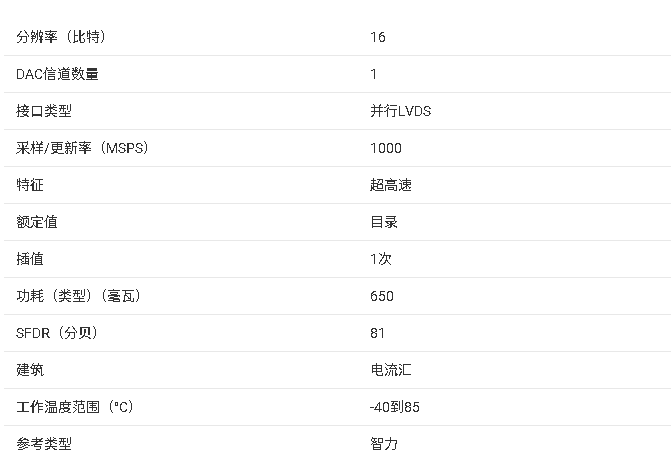

參數(shù)

方框圖

一、產品核心概述

DAC5681 是德州儀器推出的高性能高速數(shù)模轉換器,核心優(yōu)勢為超高更新率、寬頻帶輸出與高線性度。產品分辨率 16 位,最高更新率 1GSPS,工作溫度范圍 -40°C~85°C,采用 64 引腳 QFN 封裝(9mm×9mm),支持多電源供電(1.8V/3.3V),集成 LVDS 高速輸入接口、片上 1.2V 參考電壓、延遲鎖定環(huán)(DLL)及 8 級輸入 FIFO,專為蜂窩基站、寬帶無線接入、雷達系統(tǒng)、測試儀器等對帶寬和線性度要求嚴苛的高速信號生成場景設計。

二、關鍵特性與規(guī)格

1. 核心性能參數(shù)

- 分辨率與線性度 :16 位無丟失碼,積分非線性(INL)±4LSB,微分非線性(DNL)±2LSB;增益誤差 ±1% FSR(外部參考)/±0.7% FSR(內部參考),偏移誤差 0.01% FSR,增益溫漂 ±15~30ppm/°C,參考電壓溫漂 ±8ppm/°C。

- 動態(tài)性能:180MHz 單載波 WCDMA 信號的鄰道泄漏比(ACLR)73dBc;1GSPS 時 SFDR 典型 80dBc(5.1MHz 輸入),SNR 60dBc(180MHz 輸入);三階互調失真(IMD3)88dBc(20.1/21.1MHz 雙音),輸出帶寬支持多奈奎斯特 zones。

- 輸入與輸出:16 位 LVDS 差分輸入(DDR 模式),內置 100Ω 終端電阻;差分電流輸出,滿量程電流 2~20mA 可調;輸出阻抗 300kΩ,輸出電容 5pF,輸出擺幅適配 AVDD±0.5V 合規(guī)電壓。

- 功耗與延遲:典型功耗 605mW(1GSPS),睡眠模式僅 20

30mW;輸出建立時間 10.4ns(0.1% 精度),上升 / 下降時間 220ps;數(shù)字延遲 76 個 DAC 時鐘周期,啟動時間 880μs(取決于濾波器配置)。

2. 核心功能

- 高速數(shù)據(jù)接口:16 位 LVDS 輸入總線支持 DDR 數(shù)據(jù)傳輸,數(shù)據(jù)率達 1GSPS,內置 DLL 實現(xiàn)輸入時鐘與數(shù)據(jù)的 skew 校準,適配 125~500MHz 輸入時鐘頻率,降低時序設計難度。

- 靈活輸出配置:通過外部電阻(BIASJ 引腳)可調節(jié)滿量程輸出電流(2~20mA),4 位數(shù)字增益控制(CONFIG7 寄存器)支持 16 級增益微調;差分輸出架構抑制偶次諧波與共模噪聲,適配 50Ω 負載(需變壓器匹配)。

- 片上輔助功能:集成 1.2V 溫度補償參考電壓(支持外部參考替代),8 級輸入 FIFO 緩沖減少數(shù)據(jù)丟失;內置數(shù)字自測試模式(SLFTST),支持板級功能驗證無需外部測試圖案。

- 多設備同步:支持多 DAC 時鐘分頻器與 FIFO 指針同步,通過 SYNCP/N 引腳可實現(xiàn)多芯片輸出同步,同步精度達 ±1 個 DAC 時鐘周期。

三、封裝與引腳

1. 封裝信息

- 64 引腳 QFN 封裝:外露熱焊盤(7.4mm×7.4mm)需接地以優(yōu)化散熱;結到環(huán)境熱阻 20°C/W(無風)/16°C/W(150LFM 氣流),MSL 等級 3,支持 260°C 回流焊,符合 RoHS 標準。

2. 關鍵引腳功能

- 電源與地:CLKVDD(1.8V,時鐘緩沖供電)、DVDD/VFUSE(1.8V,數(shù)字供電)、AVDD/IOVDD(3.3V,模擬 / IO 供電),對應地引腳 GND(熱焊盤與引腳共地),需就近并聯(lián) 0.1μF 去耦電容。

- 輸入與控制:D [15:0] P/N(16 位 LVDS 數(shù)據(jù)輸入)、DCLKP/N(LVDS 輸入時鐘)、SYNCP/N(同步 / 使能輸入);CLKIN/CLKINC(外部時鐘輸入)、RESETB(復位)、SPI 接口(SCLK/SDENB/SDIO/SDO,配置寄存器)。

- 輸出與參考:IOUTA1/IOUTA2(差分電流輸出)、BIASJ(滿量程電流編程,外接 960Ω 電阻對應 20mA 輸出);EXTIO(內部參考輸出 / 外部參考輸入)、EXTLO(參考選擇:接地選內部,接 AVDD 選外部)。

四、工作模式與核心功能

1. 核心工作模式

- 數(shù)據(jù)輸入模式:LVDS 接口支持 DDR 數(shù)據(jù)傳輸,每時鐘周期傳輸 2 個數(shù)據(jù)樣本,內置 DLL 自動校準時鐘與數(shù)據(jù)的時序 skew,適配 250~1000MSPS 數(shù)據(jù)率;8 級 FIFO 緩沖吸收輸入數(shù)據(jù)抖動,降低源端時序要求。

- 輸出模式:差分電流輸出,通過變壓器匹配可驅動 50Ω 負載;支持單端或差分電壓輸出配置,1:1 變壓器對應 0.5Vpp 輸出,4:1 變壓器對應 1Vpp 輸出,適配不同功率需求。

- 低功耗模式:支持睡眠模式,關閉 DAC 核心與 DLL 后功耗降至 20~30mW;偏置電路集成低通濾波器,可通過寄存器選擇 95kHz 或 472kHz 截止頻率,平衡功耗與響應速度。

2. 關鍵功能

- DLL 時序校準:片上 DLL 自動調整 LVDS 輸入時鐘與數(shù)據(jù)的相位關系,支持 125~500MHz 輸入時鐘頻率,可通過寄存器微調延遲(50°~125°),確保高速傳輸時的時序裕量。

- 寄存器配置:通過 3 線 / 4 線 SPI 接口訪問 16 個配置寄存器,支持數(shù)據(jù)格式(二進制補碼 / 偏移二進制)、增益、偏移、FIFO 偏移、DLL 模式等參數(shù)配置,適配不同系統(tǒng)需求。

- 自測試與診斷:內置數(shù)字自測試模式,通過 LFSR 生成測試圖案并校驗,無需外部數(shù)據(jù)即可驗證數(shù)字信號鏈完整性;STATUS 寄存器實時反饋 DLL 鎖定狀態(tài)、FIFO 錯誤、測試結果等。

五、應用場景與設計支持

1. 典型應用

- 通信系統(tǒng):蜂窩基站(4G/5G)、WiMAX 基站、電纜調制解調器終端系統(tǒng)(CMTS)的信號生成。

- 測試與國防:雷達系統(tǒng)、電子戰(zhàn)設備、高速任意波形發(fā)生器、射頻測試儀器。

- 寬帶接入:固定無線回程、視頻點播(VOD)傳輸系統(tǒng)的 QAM 信號調制。

2. 設計資源

- 電源與去耦:模擬電源(AVDD)與數(shù)字電源(DVDD)分開布線,每個電源引腳就近放置 0.1μF 多層陶瓷電容;熱焊盤必須接地,確保散熱與電氣性能。

- 布局要點:LVDS 輸入走線需等長、差分阻抗控制 100Ω,遠離模擬輸出路徑;CLKIN/CLKINC 時鐘走線需短且隔離,推薦差分驅動以降低抖動;輸出變壓器中心抽頭接 AVDD,確保直流偏置。

- 輸入驅動:LVDS 輸入可由 FPGA/ASIC 的 SERDES 模塊驅動,推薦使用 TI CDCM7005 時鐘分配芯片提供相位對齊的時鐘;數(shù)據(jù)格式默認二進制補碼,可通過寄存器切換為偏移二進制。

- 同步設計:多 DAC 同步需先同步時鐘分頻器,再同步 FIFO 指針,通過 SYNCP/N 引腳同時觸發(fā);推薦使用相同型號時鐘源,確保多通道相位一致性。

六、可靠性與訂單信息

- 可靠性保障:絕對最大額定值:電源電壓 1.71V

3.6V,引腳電壓 -0.5VAVDD+0.5V,結溫 125°C;ESD 防護等級 2500V(人體模型),符合工業(yè)級可靠性標準。 - 可訂購型號:DAC5681IRGCR(卷盤 2000 片)、DAC5681IRGCT(小卷盤 250 片),引腳鍍層 NIPDAU,支持無鉛焊接,適配批量生產與原型開發(fā)。

-

dll

+關注

關注

0文章

120瀏覽量

46889 -

dac

+關注

關注

44文章

2728瀏覽量

197306 -

lvds

+關注

關注

2文章

1238瀏覽量

70028 -

模擬轉換器

+關注

關注

0文章

62瀏覽量

13006 -

GSPS

+關注

關注

0文章

58瀏覽量

17764

發(fā)布評論請先 登錄

高性能16位數(shù)模轉換器AD9164怎么樣?

如何設計16位高速數(shù)模轉換器(DAC)?

AD9172BBPZ——數(shù)模轉換器DAC

DAC5681,pdf(16-bit 1.0 GSPS Di

AD9122 雙通道、1.2GSPS、16位的DAC(數(shù)模轉

UG-1631:評估AD9148四路16位1 GSPS DAC TxDAC+?數(shù)模轉換器

DAC34SH84四通道16位1.5GSPS數(shù)模轉換器(DAC)數(shù)據(jù)表

DAC3484四通道16位1.25GSPS數(shù)模轉換器(DAC)數(shù)據(jù)表

DAC5681Z一款16位1.0 GSPS數(shù)模轉換器(DAC)數(shù)據(jù)表

DAC5687雙通道16位高速數(shù)模轉換器(DAC)數(shù)據(jù)表

DAC5686雙通道16位高速數(shù)模轉換器(DAC)數(shù)據(jù)表

DAC3482雙通道、16位、1.25GSPS數(shù)模轉換器(DAC)數(shù)據(jù)表

DAC5670-SP 14位2.4 GSPS數(shù)模轉換器(DAC)數(shù)據(jù)表

DAC5681 16位1.0 GSPS數(shù)模轉換器(DAC)數(shù)據(jù)表

DAC5681Z 16 位 1.0 GSPS 插值型數(shù)模轉換器(DAC)產品手冊總結

DAC5681 16 位 1GSPS 高速數(shù)模轉換器(DAC)產品手冊總結

DAC5681 16 位 1GSPS 高速數(shù)模轉換器(DAC)產品手冊總結

評論