以下文章來源于逍遙設計自動化,作者逍遙科技

引言

人工智能和機器學習應用的爆炸式增長已經將高性能計算系統推向極限。在訓練日益復雜的AI模型時,計算需求從2010年的petaFLOPs飆升到今天的yottaFLOPs,預計到2030年將達到quettaFLOPs。這種大規模增長暴露出現代計算架構中的一個關鍵瓶頸:芯片間數據傳輸所消耗的能量遠遠超過計算操作本身。要理解新興的3D電子-光子互連平臺如何解決這一挑戰,需要深入研究當前銅基系統的根本限制以及光學技術提供的解決方案[1]。

01互連性能挑戰的本質

在評估互連技術時,需要同時考慮多個性能維度。能效衡量傳輸每比特數據需要多少皮焦耳能量。帶寬密度表示給定區域可以流通多少數據,通常以每平方毫米千兆比特每秒來衡量。硅效率指收發器線路消耗多少芯片面積,而鏈路延遲則反映數據傳輸的時間延遲。這些指標組合成一個綜合性能指標,揭示了不同互連方法在各種鏈路長度和應用場景下的表現。

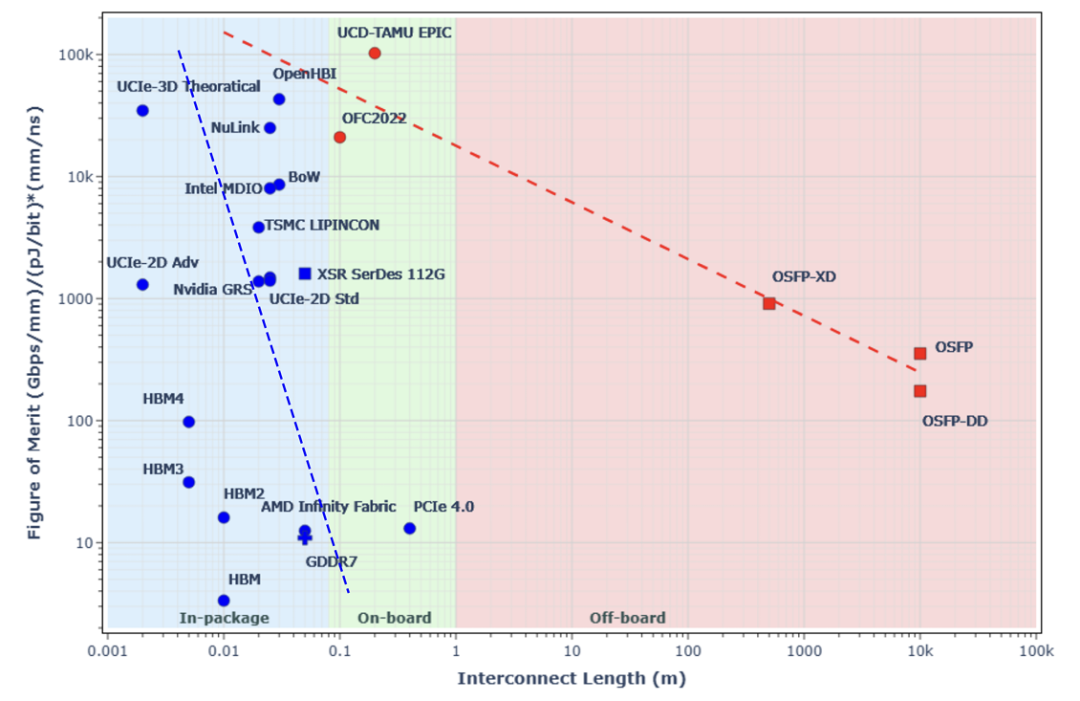

圖1:性能對比展示不同互連技術如何隨鏈路長度擴展,光學互連在較長距離保持優異性能,而電氣互連僅在極短距離表現出色。

性能格局在不同互連類型中呈現出明顯的模式。使用銅傳輸線的傳統電氣互連在極短距離(如3D堆疊高帶寬存儲器模塊內的連接)表現良好。然而,當鏈路長度超過幾毫米時,性能會急劇下降。相比之下,光學互連在更長距離上保持穩定的高性能,使其成為封裝內芯片到芯片通信及更遠距離的理想選擇。考慮所有性能因素后,光學方案變得更優的交叉點出現在出乎意料的短距離處。

02銅與光的基礎物理學

要理解光學互連的優勢,必須了解銅互連的物理限制。當高速電信號通過銅傳輸線傳播時,會經歷多種形式的衰減。導電損耗發生在電子遇到金屬電阻時。介電損耗源于導體周圍的絕緣材料。相鄰信號線之間的串擾會產生干擾并破壞數據。色散導致信號的不同頻率分量以不同速度傳播,使數字脈沖展寬并造成時序錯誤。這些損傷都會隨頻率和距離的增加而惡化,迫使設計者添加復雜且耗能的數字信號處理線路。

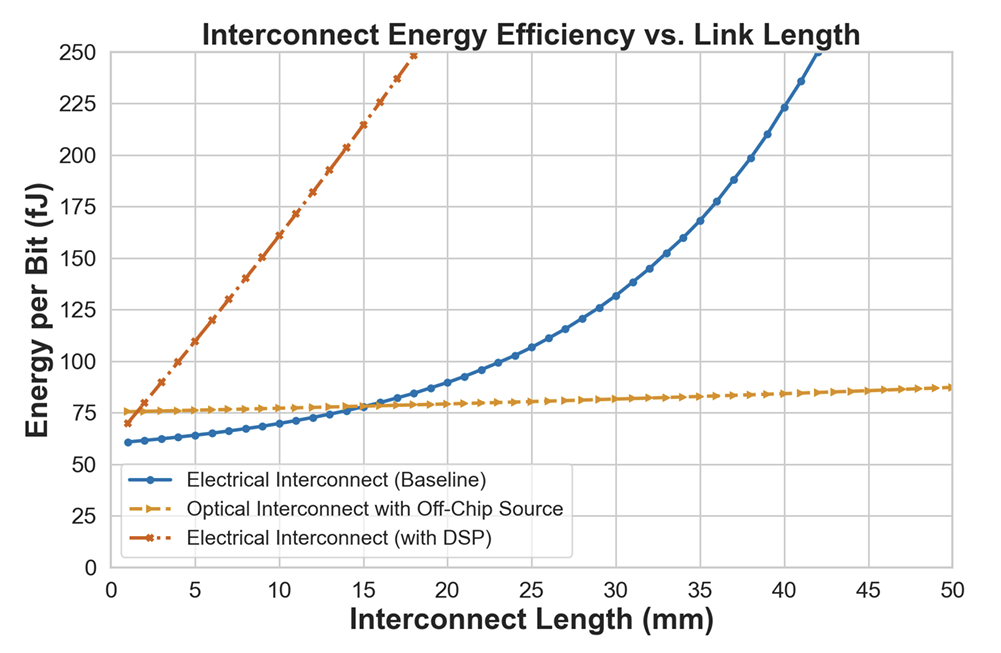

圖2:能效對比揭示了光學互連比電氣互連更節能的分界長度,在此分析中僅為15.1毫米。

考慮在8 Gbps數據速率下的實際對比。銅互連在極短鏈路中消耗相對適中的能量,但每比特能量隨距離呈指數增長。光學互連則保持幾乎恒定的能耗,與長度無關。對于這種配置,稱為分界長度的臨界轉換點出現在約15毫米處。當考慮到銅鏈路需要用于均衡、糾錯和時鐘恢復的數字信號處理線路時,分界長度急劇縮短至僅2.5毫米。這些線路每比特可消耗20到1900飛焦耳,對電氣系統構成顯著的能量負擔。

033D電子-光子架構

提出的解決方案涉及通過光學硅通孔(TSOV)垂直穿過堆棧,將多個chiplet以3D方式堆疊并用光學互連連接。這種架構從根本上改變了對芯片間通信的思考方式。高速連接不再局限于可放置銅凸塊的芯片邊緣,光信號可以從芯片區域的任何位置發出。堆棧中的每個chiplet都可以與同一堆棧或不同堆棧中的任何其他chiplet直接通信,創建真正的全局互連fabric。

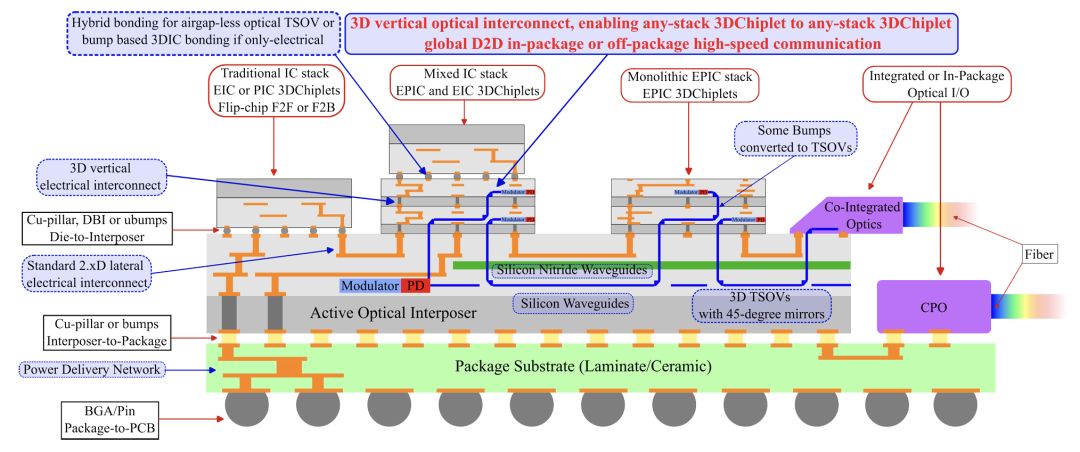

圖3:3D chiplet堆疊平臺的架構概覽,展示光學TSOV如何實現垂直通信,而傳統電氣TSV處理功率傳輸和低延遲控制信號。

該平臺巧妙地結合了電氣和光學領域的優勢。傳統的硅通孔和2.5D互連繼續處理功率傳輸以及短距離、延遲敏感的通信,如緩存一致性內存訪問。光學層接管所有高帶寬、長距離的數據移動。這種混合方法保持了與現有標準(如高帶寬內存接口)的向后兼容性,同時通過波分復用實現帶寬密度的大幅提升。

04通過波長復用擴展帶寬密度

當研究波分復用如何擴展容量時,這種光學方法的帶寬優勢變得顯著。通過將一小部分電氣凸塊轉換為光學TSOV,然后在每個TSOV中復用多個波長通道,系統實現了電氣互連無法達到的帶寬密度。從每個TSOV僅4個波長通道開始就能提供有競爭力的性能,但擴展到32或64個通道可實現超過每平方毫米10太比特每秒的帶寬密度。

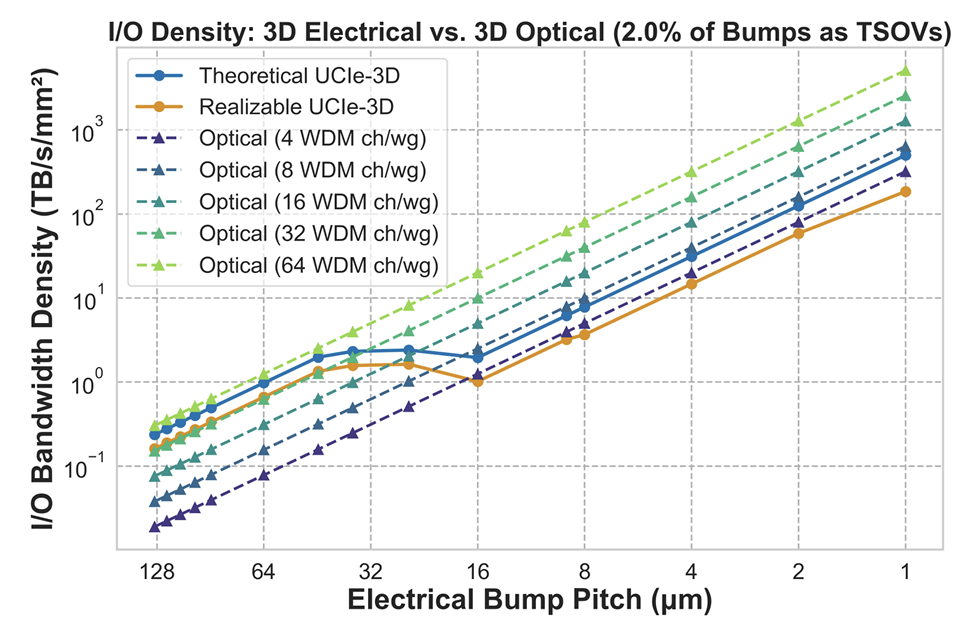

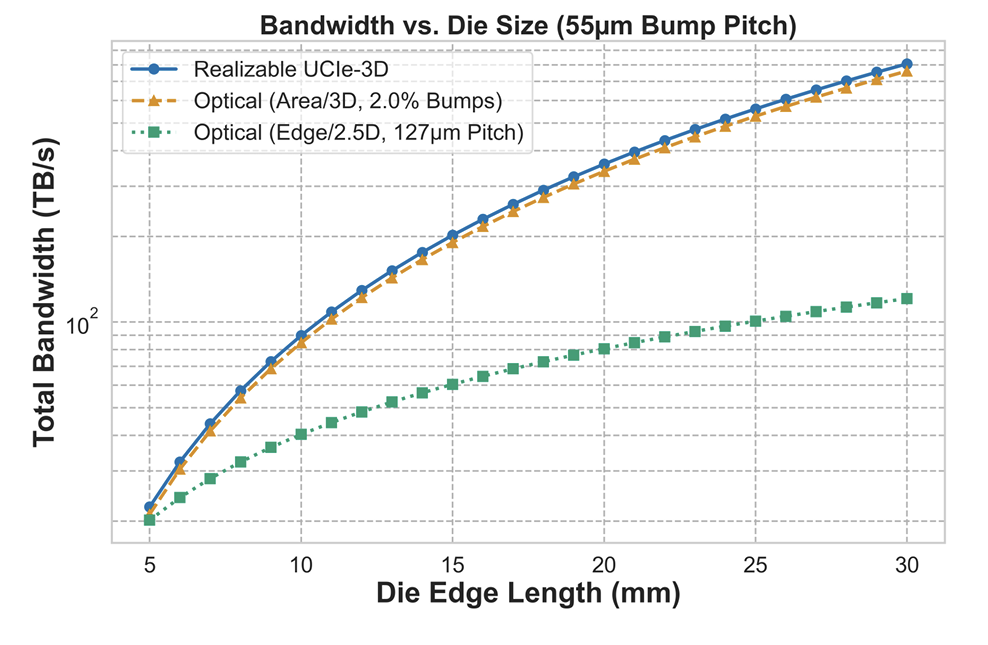

圖4:帶寬密度對比顯示具有不同波長數的3D光學互連在各種凸塊間距范圍內超越電氣互連。

擴展數學對光學系統有利,因為基于面積的互連隨芯片邊長的平方擴展,而基于周邊的方法線性擴展。隨著芯片尺寸增長到30毫米邊長及以上,面積分布光學I/O的優勢變得壓倒性。在55微米間距下,2%的凸塊轉TSOV轉換率可以匹配甚至超過最密集電氣互連的總帶寬,同時在更寬松的電氣互連密度下運行,簡化了功率傳輸網絡設計。

圖5:總帶寬隨芯片尺寸的擴展,說明基于面積的3D光學互連相對于基于周邊的2.5D光學方法的平方優勢。

05使能技術與實現路徑

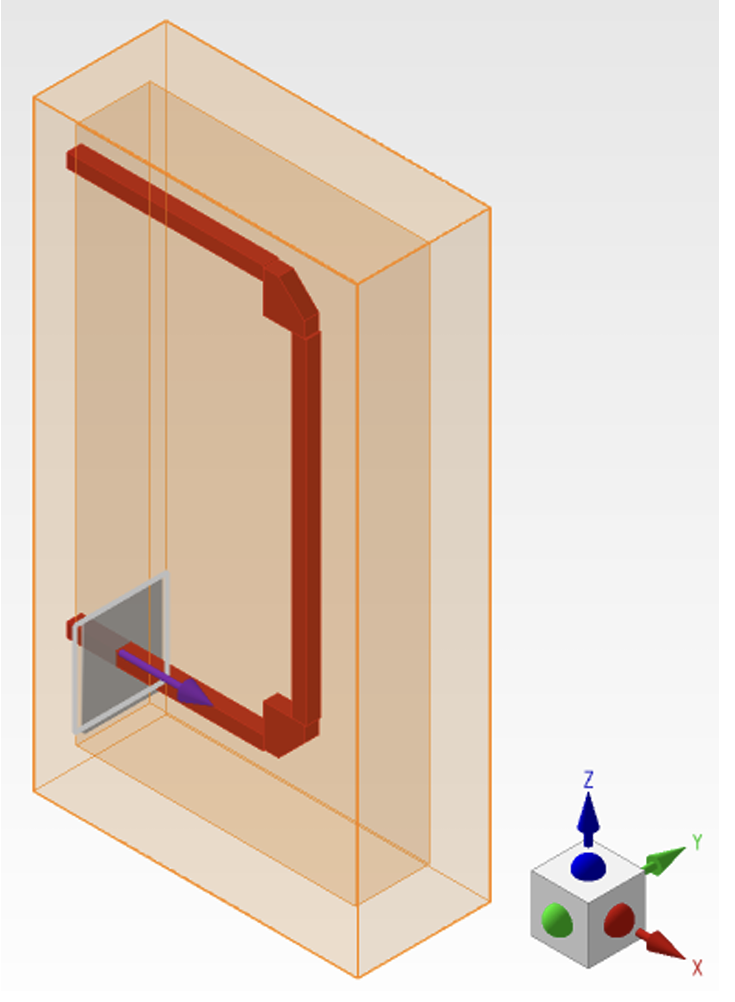

實現這一愿景需要幾項關鍵的使能技術。光學硅通孔代表了最核心的創新。這種結構使用45度鏡面將光從水平波導重定向到穿過硅基板的垂直波導中。仿真顯示在通信C波段的耦合損耗低于1分貝,優化設計可實現低至0.42分貝。使用Bosch刻蝕的制造已成功生產出20微米高、縱橫比為54:1的通孔,開發目標是100微米高度,縱橫比超過270:1。

圖6:TSOV結構的詳細FDTD仿真模型,顯示45度鏡面部分和垂直波導每次轉換的損耗小于1分貝。

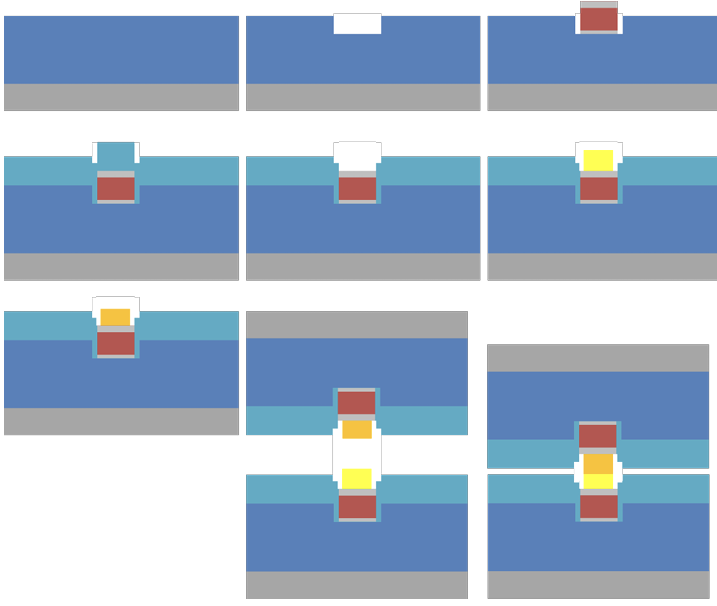

電子和光電子芯片chiplet的集成需要先進的鍵合技術。金錫共晶鍵合為最終實現無氣隙鍵合提供了路徑,這對TSOV的最佳對準是必需的。這種方法相比傳統焊料凸塊鍵合的優勢在于能夠進行多級assembly而無回流風險。目前的開發已實現超過22千克力的鍵合強度,芯片斷裂發生在鍵合斷裂之前,展示了穩固的機械連接。

圖7:分步鍵合工藝開發,展示共晶冶金方法,實現可靠的芯片對芯片集成,無需面對與氣隙相關的對準挑戰。

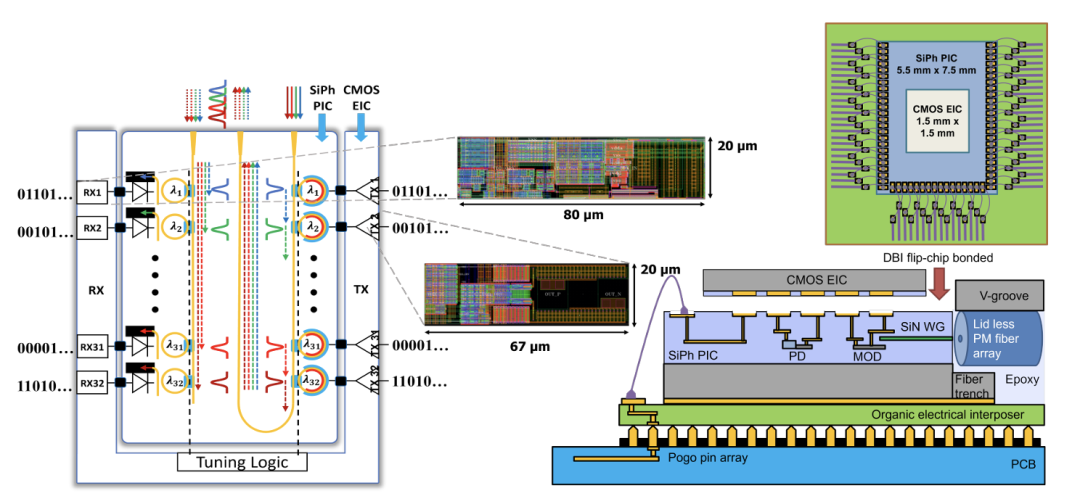

光電子芯片和電子線路之間的寄生電容對接收器靈敏度和整體系統能效起決定性作用。直接鍵合互連技術將互連電容降低至僅7.2飛法,而傳統C4凸塊為31.6飛法。這種降低使得在25 Gbps下實現了創紀錄的負17.01分貝光調制幅度接收器靈敏度,能效達到191飛焦耳每比特。未來的單片集成可將總輸入電容降至3.2飛法,將靈敏度再提高8.36分貝,為最終目標100飛焦耳每比特或更低提供了清晰的路徑。

圖8:3D異構收發器完整系統架構,顯示共同設計的電子和光電子集成芯片以及使用波分復用的32個光學通道。

光學路由、先進鍵合和異構集成方面的這些創新融合,創建了一個解決未來高性能計算可擴展性所有主要限制的平臺,在帶寬和密度方面實現節能通信。

-

光學

+關注

關注

4文章

829瀏覽量

37860 -

互連技術

+關注

關注

0文章

29瀏覽量

10607

原文標題:3D光電互連技術

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Altium 3D模式提示 action not available in 3D view

一文解讀3D打印技術的應用及發展

一文帶你看懂3D視覺

基于HFSS的3D多芯片互連封裝MMIC仿真設計

一文詳解3D光電互連技術

一文詳解3D光電互連技術

評論