ADC342x是一款高線性度、超低功耗、四通道、12位、25MSPS至125MSPS模數(shù)轉換器(ADC)系列。這些器件專為支持具有大動態(tài)范圍要求的苛刻高輸入頻率信號而設計。輸入時鐘分頻器為系統(tǒng)時鐘架構設計提供了更大的靈活性,SYSREF輸入可實現(xiàn)完整的系統(tǒng)同步。ADC342x系列支持串行低壓差分信號(LVDS),以減少接口線的數(shù)量,從而實現(xiàn)高系統(tǒng)集成密度。串行LVDS接口為雙線接口,其中每個ADC數(shù)據(jù)通過兩個LVDS對串行輸出。內(nèi)部鎖相環(huán)(PLL)將輸入ADC采樣時鐘相乘,以得出用于序列化每個通道的12位輸出數(shù)據(jù)的位時鐘。除了串行數(shù)據(jù)流外,幀和位時鐘也作為LVDS輸出傳輸。

*附件:adc3421.pdf

特性

- 四通道

- 12 位分辨率

- 單電源:1.8 V

- 串行LVDS接口

- 靈活的輸入時鐘緩沖器,具有1、-2、-4分頻功能

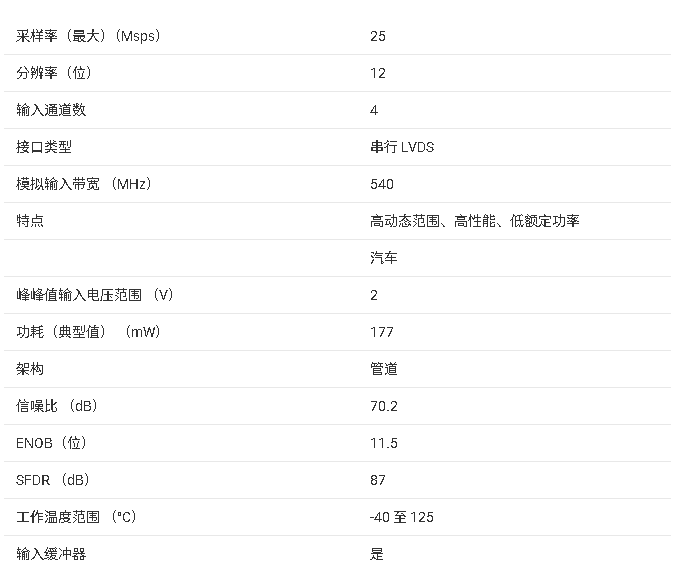

- SNR = 70.2 dBFS,SFDR = 87 dBc(f

在= 70兆赫 - 超低功耗:

- 98 mW/通道,125 MSPS

- 信道隔離度:105 dB

- 內(nèi)部抖動和斬波器

- 支持多芯片同步

- 引腳對引腳兼容,與14位版本兼容

- 封裝:VQFN-56(8 mm × 8 mm)

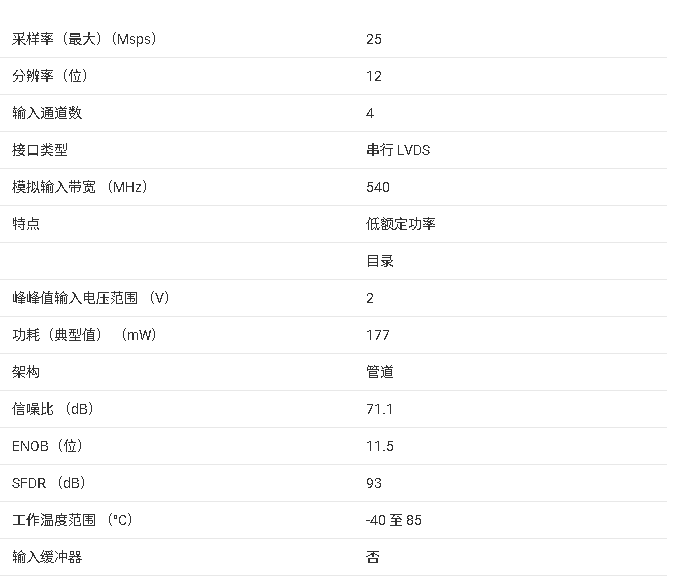

參數(shù)

方框圖

ADC3421 系列是德州儀器推出的四通道高速高精度 ADC,采樣率覆蓋 25 MSPS(ADC3421)至 125 MSPS(ADC3424),核心優(yōu)勢是高線性度、低功耗、寬輸入帶寬及 LVDS 串行接口,適用于蜂窩基站、雷達、軟件無線電(SDR)等對多通道、高動態(tài)范圍要求嚴苛的場景。

一、核心性能與定位

- 精度與頻譜性能 :12 位分辨率,70 MHz 輸入時 SNR 達 70.2 dBFS、SFDR 達 87 dBc;通道隔離度 105 dB,內(nèi)置抖動(Dither)和斬波(Chopper)功能,降低噪聲與諧波失真;積分非線性(INL)、微分非線性(DNL)性能優(yōu)異,無失碼輸出。

- 輸入與帶寬 :差分輸入滿量程 2 VPP,3 dB 輸入帶寬達 540 MHz,支持高頻信號采集;輸入共模電壓固定為 0.95 V,輸入阻抗 6.6 kΩ(差分)、輸入電容 3.7 pF,適配多種信號源驅(qū)動。

- 速率與功耗 :單通道功耗低至 98 mW(125 MSPS 時),四通道總功耗最高 475 mW;支持 1 倍 / 2 倍 / 4 倍輸入時鐘分頻,靈活適配系統(tǒng)時鐘架構。

- 環(huán)境適應性 :工作溫度 -40°C

85°C,模擬 / 數(shù)字電源均為 1.7 V1.9 V(標稱 1.8 V);抗靜電性能達 HBM ±2000 V,兼容 1.8 V/3.3 V CMOS 數(shù)字輸入。

二、關鍵功能與硬件特性

1. 集成功能模塊

- 四通道獨立 ADC 核心,每通道數(shù)據(jù)通過 LVDS 串行接口輸出,支持 1 線(12 倍串行化)或 2 線(6 倍串行化)模式,減少接口線數(shù),提升系統(tǒng)集成度。

- 內(nèi)置 PLL 電路,將采樣時鐘倍頻為位時鐘,用于數(shù)據(jù)串行化;支持 SYSREF 同步輸入,實現(xiàn)多芯片同步采集,滿足大規(guī)模多通道系統(tǒng)需求。

- 提供全局掉電、待機及單通道掉電模式,全局掉電功耗僅 5 mW,待機模式喚醒時間 35 μs,平衡性能與節(jié)能需求。

2. 工作模式

- 連續(xù)采樣模式:四通道同步高速采集,適用于實時數(shù)據(jù)傳輸場景。

- 低功耗模式:支持全局掉電(功耗 5 mW)和待機模式(功耗 45 mW),可通過引腳或寄存器配置,適配低吞吐量場景。

- 測試模式:支持全 0、全 1、偽隨機序列(PRBS)等多種測試圖案輸出,便于系統(tǒng)自檢與調(diào)試。

3. 封裝與引腳

- 采用 56 引腳 8mm×8mm VQFN 封裝,含獨立模擬電源(AVDD)、數(shù)字電源(DVDD)及接地引腳,底部熱焊盤需接地優(yōu)化散熱。

- 引腳包括四組差分模擬輸入(INAP/INAM

INDM/INDP)、LVDS 數(shù)據(jù)輸出(DAxP/DAxMDDxP/DDxM)、時鐘輸入(CLKP/CLKM)、同步信號(SYSREFP/SYSREFM)及 SPI 控制引腳。

三、編程與配置

- 寄存器控制 :通過 SPI 接口訪問多頁寄存器,配置采樣模式、LVDS 輸出格式、掉電控制、抖動 / 斬波功能使能等;支持寄存器讀寫校驗,確保配置可靠性。

- 數(shù)據(jù)格式與接口 :輸出 12 位二進制補碼或偏移二進制格式,LVDS 輸出差分電壓 280 mV~460 mV,支持 100 Ω 差分阻抗匹配;幀時鐘(FCLK)、位時鐘(DCLK)同步輸出,便于后端數(shù)據(jù)解析。

- 同步與校正 :SYSREF 信號實現(xiàn)多芯片同步,時鐘分頻功能適配不同輸入時鐘頻率;內(nèi)置孔徑抖動校正,降低外部時鐘抖動對采樣精度的影響。

四、典型應用場景

五、設計關鍵要點

- 電源與去耦 :模擬電源(AVDD)與數(shù)字電源(DVDD)需獨立供電,各電源引腳就近配置 0.1 μF 陶瓷電容 + 10 μF 電解電容去耦,減少電源噪聲耦合;電源平面需分離,降低數(shù)字噪聲對模擬電路的干擾。

- 時鐘與同步:采用低抖動時鐘源(建議外部時鐘抖動盡可能小),時鐘輸入支持差分( sine/LVPECL/LVDS)或單端(LVCMOS)驅(qū)動;多芯片同步時需保證 SYSREF 信號與采樣時鐘的時序關系,滿足建立 / 保持時間要求。

- 信號接口:模擬輸入采用差分布線,長度匹配,串聯(lián) 5 Ω~15 Ω 電阻抑制寄生振蕩;LVDS 輸出通道需阻抗匹配(100 Ω 差分),遠離模擬信號路徑,避免串擾。

- 布局規(guī)范:分離模擬與數(shù)字區(qū)域,采用完整接地平面;熱焊盤可靠接地以優(yōu)化散熱;模擬輸入與時鐘信號布線避免交叉,數(shù)字輸出走線與模擬輸入走線保持垂直,減少電磁干擾。

-

接口

+關注

關注

33文章

9561瀏覽量

157392 -

MSPS

+關注

關注

0文章

574瀏覽量

29012 -

adc

+關注

關注

100文章

7694瀏覽量

556585 -

模數(shù)轉換器

+關注

關注

26文章

4057瀏覽量

130208 -

差分信號

+關注

關注

4文章

409瀏覽量

29040

發(fā)布評論請先 登錄

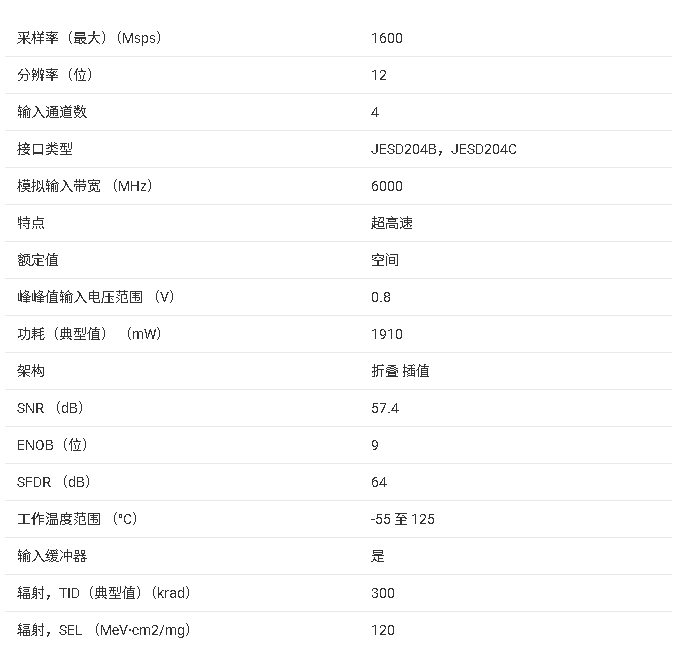

ADC12QJ1600-SEP四通道1.6GSPS 12位模數(shù)轉換器(ADC)數(shù)據(jù)表

ADC12QJ1600-SP具有JESD204C接口的四通道1.6GSPS 12位模數(shù)轉換器(ADC)數(shù)據(jù)

ADC12xJ800-Q1四通道/雙通道/單通道、800MSPS、12位模數(shù)轉換器(ADC)數(shù)據(jù)表

ADC12xJ800四通道/雙通道/單通道800MSPS 12位模數(shù)轉換器(ADC)數(shù)據(jù)表

ADC12xJ1600-Q1四通道/雙通道/單通道、1.6GSPS、12位模數(shù)轉換器(ADC)數(shù)據(jù)表

ADC12xJ1600四通道/雙通道/單通道模數(shù)轉換器(ADC)數(shù)據(jù)表

ADC09xJ800四通道/雙通道/單通道800MSPS 9位模數(shù)轉換器(ADC)數(shù)據(jù)表

ADC09xJ1300四通道/雙通道/單通道1.3GSPS 9位模數(shù)轉換器(ADC)數(shù)據(jù)表

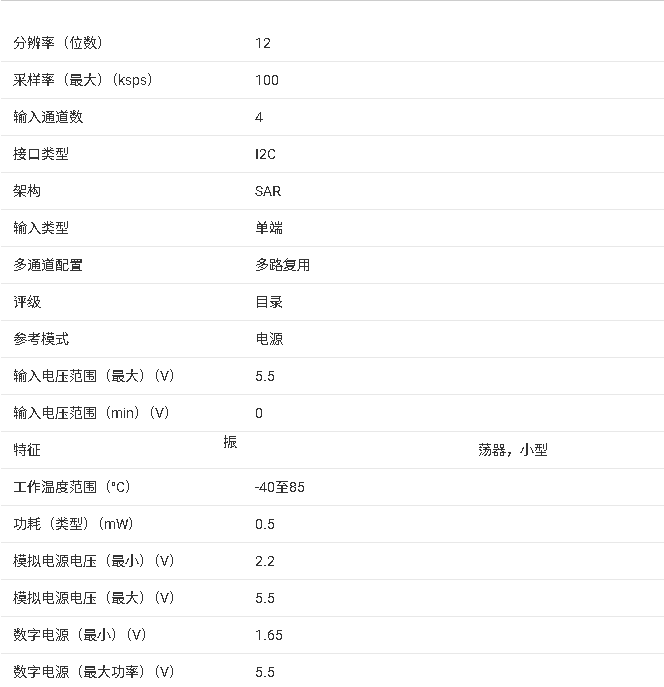

ADC12QS065四通道12位65 MSPS模數(shù)轉換器數(shù)據(jù)表

ADC084S051四通道CMOS 8位模數(shù)轉換器數(shù)據(jù)表

ADC3421 系列 12 位四通道高速模數(shù)轉換器(ADC)技術文檔總結

ADC3421 系列 12 位四通道高速模數(shù)轉換器(ADC)技術文檔總結

評論