在大規(guī)模 MIMO (mMIMO)等高密度無(wú)線系統(tǒng)中,信道估計(jì)不僅是衡量性能的核心指標(biāo),更是決定系統(tǒng)能效的關(guān)鍵一環(huán)。隨著頻譜擁塞問(wèn)題日益突出,移動(dòng)環(huán)境也愈發(fā)動(dòng)態(tài)多變,傳統(tǒng)信道估計(jì)方法已難以滿足現(xiàn)代網(wǎng)絡(luò)對(duì)速度和復(fù)雜性的更高要求。

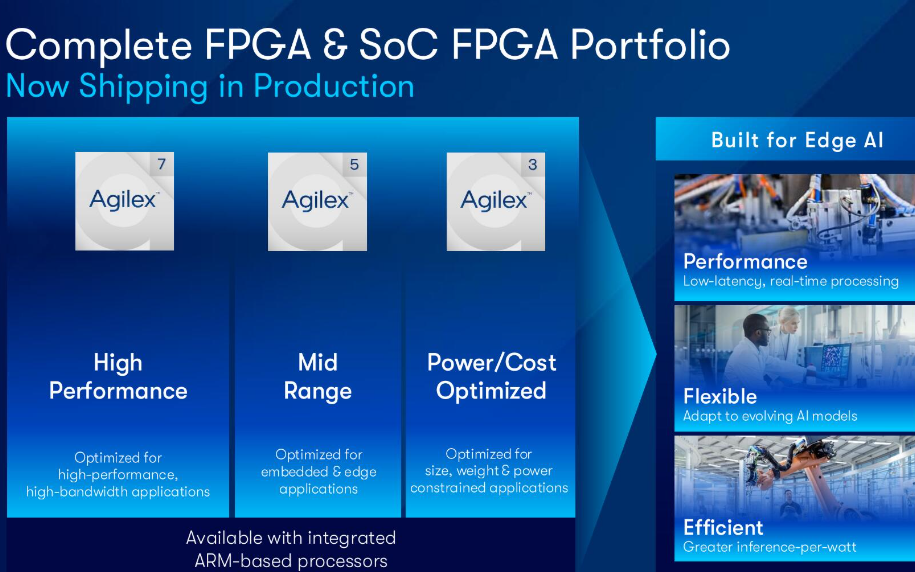

Altera FPGAi 解決方案來(lái)破局,mMIMO 系統(tǒng)智能和能效表現(xiàn)全面提升!依托部署在Agilex SoC FPGA上的魯棒神經(jīng)網(wǎng)絡(luò),Altera 實(shí)現(xiàn)了快速準(zhǔn)確的信道系數(shù)估計(jì)。與最小均方誤差 (MMSE) 等傳統(tǒng)方法相比,硬件資源占用和時(shí)延均實(shí)現(xiàn)了顯著降低。

神經(jīng)網(wǎng)絡(luò)賦能新一代 RAN

傳統(tǒng)信道估計(jì)方法對(duì)實(shí)際噪聲敏感度較高,且計(jì)算強(qiáng)度偏大,面臨著巨大的挑戰(zhàn),這一問(wèn)題在天線數(shù)量和調(diào)制方案持續(xù)升級(jí)時(shí)尤為明顯。Altera 基于 AI 的信道估計(jì)模型具備差異化優(yōu)勢(shì),通過(guò)輸入信噪比 (SNR)和時(shí)延擴(kuò)展等關(guān)鍵參數(shù),能夠生成精準(zhǔn)度更高,且具備上下文感知能力的無(wú)線信道估計(jì)結(jié)果,有效適配復(fù)雜應(yīng)用場(chǎng)景。

利用 Altera 的 DSP Builder 軟件及其與 Quartus Prime 軟件的無(wú)縫集成,該方案實(shí)現(xiàn)了以下顯著優(yōu)勢(shì):

動(dòng)態(tài)無(wú)線電環(huán)境下的高吞吐量信道估計(jì)

相較于非 AI 實(shí)施方案,減少 FPGA 設(shè)備資源占用,降低設(shè)備功耗,從而降低運(yùn)營(yíng)成本(OpEx):

DSP 模塊數(shù)量減少多達(dá) 67%

M20K 模塊數(shù)量減少多達(dá) 58%

在 FPGA 邏輯架構(gòu)上優(yōu)化推理流水線,從而實(shí)現(xiàn)更低時(shí)延

增強(qiáng) 5G 及未來(lái) 6G RAN 架構(gòu)的可擴(kuò)展性

對(duì) mMIMO 等技術(shù)的重要意義

隨著網(wǎng)絡(luò)向開放式 RAN 和日益虛擬化的基礎(chǔ)設(shè)施不斷演進(jìn),緊湊高效且具備靈活部署能力的 AI 模型,已成為了關(guān)鍵差異化優(yōu)勢(shì)。憑借并行處理能力和可編程性,F(xiàn)PGA 為執(zhí)行信道估計(jì)等 AI 增強(qiáng)型信號(hào)處理任務(wù)提供了兼具性能和靈活性的理想平臺(tái)。

Altera 的 AI 原生 Agilex FPGA 設(shè)備架構(gòu),可將智能計(jì)算部署至更貼近信號(hào)源的位置,助力 RAN 實(shí)現(xiàn)更快速的相應(yīng)、更精簡(jiǎn)的架構(gòu)和更強(qiáng)的環(huán)境適應(yīng)性。無(wú)論是構(gòu)建高移動(dòng)性用例,還是設(shè)計(jì)具有能耗感知功能的小基站,該方案都能提供更卓越的性能表現(xiàn)和更優(yōu)異的 FPGA 功耗控制,從而有效降低無(wú)線運(yùn)營(yíng)商運(yùn)營(yíng)成本。

本演示是 Altera 利用 FPGAi 重塑無(wú)線接入網(wǎng)的關(guān)鍵成果之一,集中展現(xiàn)了 AI 與信號(hào)處理深度融合后,無(wú)線通信領(lǐng)域新潛能的解鎖路徑。通過(guò)提供先進(jìn)工具鏈,Altera 支持神經(jīng)網(wǎng)絡(luò)模型在硬件中的快速部署與精準(zhǔn)調(diào)優(yōu),有效加速了從算法到芯片的轉(zhuǎn)化進(jìn)程。

-

FPGA

+關(guān)注

關(guān)注

1656文章

22317瀏覽量

631092 -

Altera

+關(guān)注

關(guān)注

37文章

819瀏覽量

158242 -

無(wú)線系統(tǒng)

+關(guān)注

關(guān)注

0文章

292瀏覽量

22219 -

Agilex

+關(guān)注

關(guān)注

0文章

26瀏覽量

3989

原文標(biāo)題:AI 驅(qū)動(dòng) + Agilex? SoC FPGA 搞定高級(jí)信道估計(jì),mMIMO 降本增效雙在線

文章出處:【微信號(hào):英特爾FPGA,微信公眾號(hào):英特爾FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Altera攜手合作伙伴共建FPGA創(chuàng)新未來(lái)

Altera進(jìn)一步擴(kuò)展 Agilex? FPGA 產(chǎn)品組合,全面提升開發(fā)體驗(yàn)

Linux系統(tǒng)性能優(yōu)化技巧

使用Altera SoC FPGA提升AI信道估計(jì)效率

Linux系統(tǒng)性能調(diào)優(yōu)方案

通信設(shè)備EMC整改:從測(cè)試到優(yōu)化的系統(tǒng)性解決方案

Altera Agilex 3 FPGA和SoC產(chǎn)品介紹

Altera FPGAi解決方案助力mMIMO系統(tǒng)性能提升

Altera FPGAi解決方案助力mMIMO系統(tǒng)性能提升

評(píng)論