ADC12DJ5200-EP器件是一款射頻采樣、千兆采樣、模數轉換器(ADC),可直接對從直流到10GHz以上的輸入頻率進行采樣。ADC12DJ5200-EP可配置為雙通道5.2GSPS ADC或單通道10.4GSPS ADC。支持高達 10GHz 的可用輸入頻率范圍,可對頻率捷變系統進行 L 波段、S 波段、C 波段和 X 波段的直接射頻采樣。

*附件:adc12dj5200-ep.pdf

ADC12DJ5200-EP 采用高速JESD204C輸出接口,具有多達 16 個串行通道,支持高達 17.16Gbps 的線速。通過JESD204C子類 1 支持確定性延遲和多設備同步。JESD204C接口可以配置為權衡線路速率和通道數。支持 8b/10b 和 64b/66b 數據編碼方案。64b/66b 編碼支持前向糾錯 (FEC),以提高誤碼率。該接口向后兼容JESD204B接收器。

創新的同步功能,包括無噪聲孔徑延遲調整和 SYSREF 窗口,簡化了多通道應用的系統設計。可選的數字下變頻器(DDC)可提供到基帶的數字轉換并降低接口速率。可編程FIR濾波器允許片內均衡。

特性

- 高可靠性增強型產品:

- 受控基線:一個裝配和測試站點、一個制造站點、延長產品生命周期、延長產品變更通知和產品可追溯性

- ADC內核:

- 12 位分辨率

- 單通道模式下高達 10.4GSPS

- 雙通道模式下高達 5.2GSPS

- 性能規格:

- 本底噪聲(–20dBFS,VFS = 1VPP-DIFF):

- 雙通道模式:–151.8dBFS/Hz

- 單通道模式:–154.4dBFS/Hz

- ENOB(雙通道,FIN = 2.4GHz):8.6位

- 本底噪聲(–20dBFS,VFS = 1VPP-DIFF):

- VCMI為0V的緩沖模擬輸入:

- 模擬輸入帶寬 (–3dB):8GHz

- 可用輸入頻率范圍:> 10GHz

- 滿量程輸入電壓(VFS,默認):0.8VPP

- 無噪聲孔徑延遲 (tAD) 調節:

- 精確采樣控制:19fs 步長

- 簡化同步和交錯

- 溫度和電壓不變延遲

- 易于使用的同步功能:

- 自動 SYSREF 定時校準

- 樣品標記的時間戳

- JESD204C串行數據接口:

- 最大通道速率:17.16Gbps

- 支持 64b/66b 和 8b/10b 編碼

- 8b/10b 模式JESD204B兼容

- 可選數字下變頻器 (DDC):

- 4 倍、8 倍、16 倍和 32 倍復數抽取

- 每個DDC有四個獨立的32位NCO

- 峰值射頻輸入功率(差分):+26.5dBm(+ 27.5dBFS,560倍滿量程功率)

- 用于均衡的可編程 FIR 濾波器

- 功耗:4W

- 電源:1.1V、1.9V

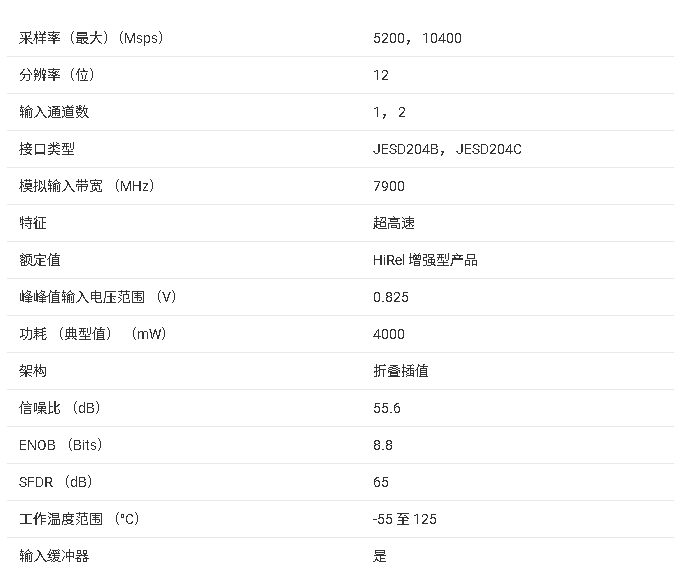

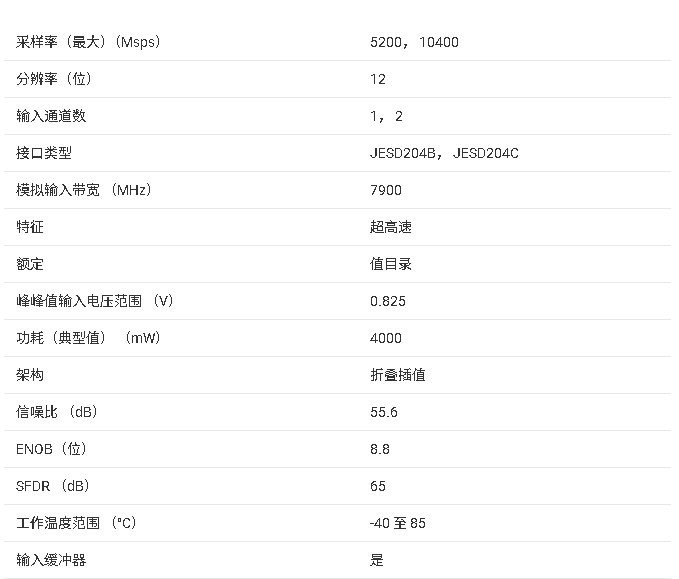

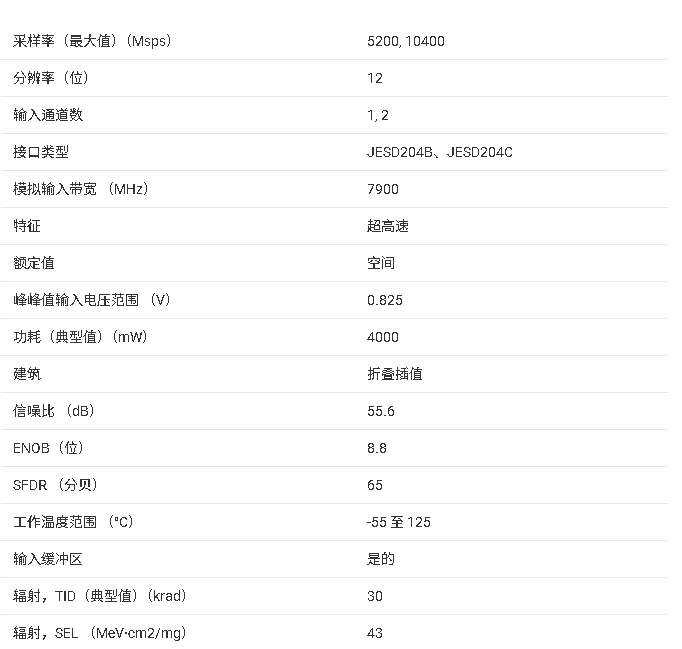

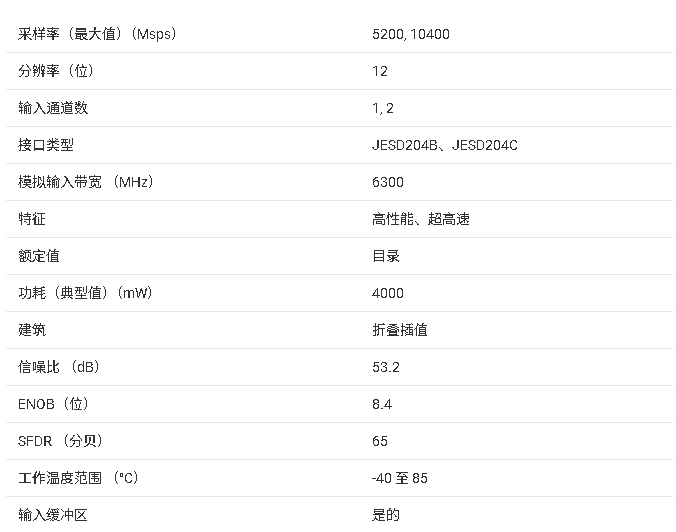

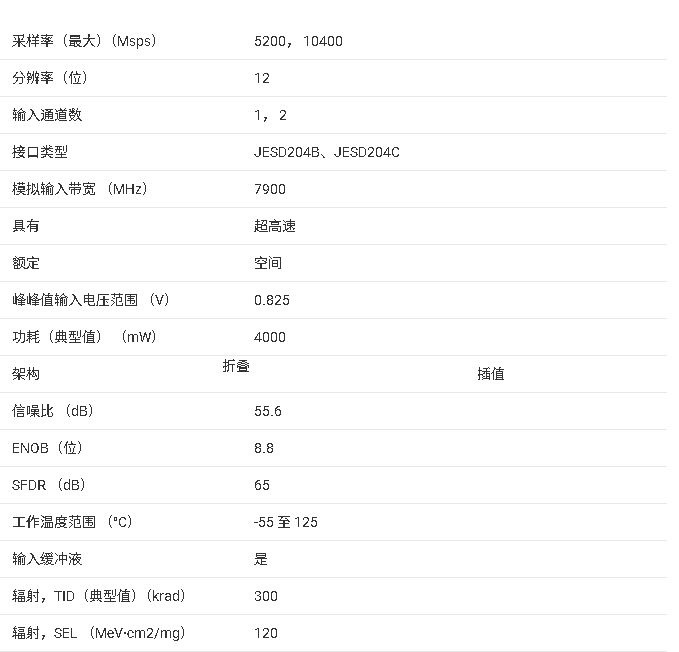

參數

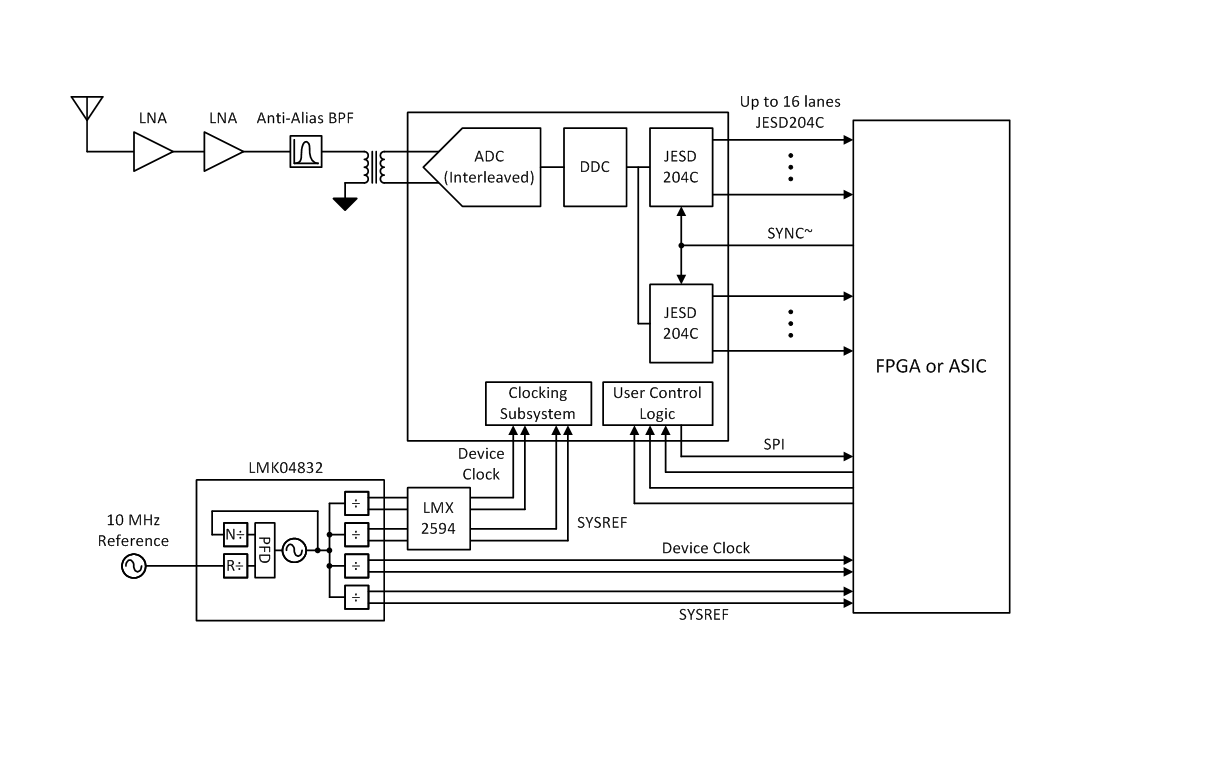

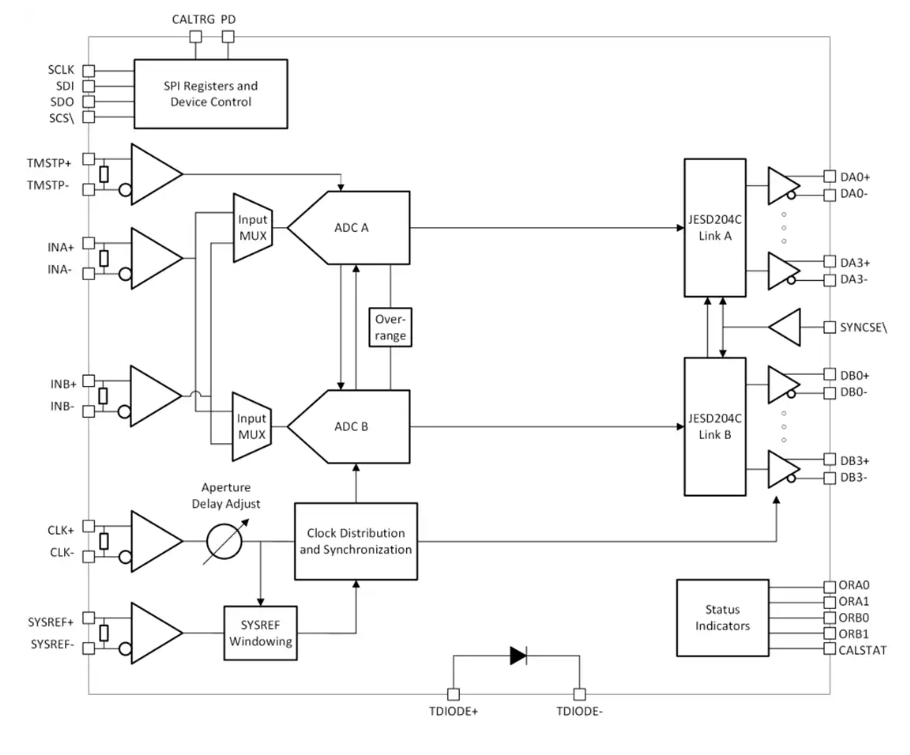

方框圖

一、產品核心定位與基礎參數

ADC12DJ5200-EP 以 “高速采樣 + 寬頻覆蓋 + 多模式適配” 為核心優勢,通過射頻直接采樣架構、靈活通道配置與高穩定性校準設計,滿足高頻信號采集場景的性能需求,適配單 / 雙電源供電與寬溫環境。

1. 核心基礎參數總覽

| 類別 | 關鍵指標 | 說明 |

|---|---|---|

| 核心規格 | 分辨率 / 通道數 / 采樣率 | 12 位;雙差分輸入通道(INA±/INB±);單通道模式最高 10.4 GSPS,雙通道模式最高 5.2 GSPS |

| 可靠性特性 | 工作溫域 / 封裝 / ESD 防護 | -40℃~+125℃寬溫;144 引腳 FCBGA(10mm×10mm);HBM 2000V/CDM 500V ESD 防護 |

| 供電與功耗 | 供電范圍 / 功耗(典型值) | 模擬供電(VA19=1.9V、VA11=1.1V),數字供電(VD11=1.1V);單通道模式約 4.0~5.3W,雙通道模式約 4.9~5.03W,低功耗模式(PD 引腳高)僅 0.18W |

| 核心集成模塊 | 關鍵功能集成 | 4 路數控振蕩器(NCO)、數字下變頻器(DDC,支持 4x/8x/16x/32x 抽取)、可編程 FIR 濾波器、JESD204C 接口(支持 8B/10B/64B/66B 編碼)、溫度二極管、多模式校準 |

| 輸入與帶寬 | 輸入范圍 / 全功率帶寬 | 差分輸入全量程電壓 500~1000 mVPP(默認 800 mVPP);全功率輸入帶寬(FPBW)8GHz,支持 DC 至 10GHz 以上信號直接采樣 |

二、核心性能參數

1. 靜態性能(TA=-40~+125℃,VA19=1.9V,VA11=VD11=1.1V)

(1)線性度與精度

- 積分非線性(INL) :最大 - 2.4 LSB,無失碼,保障全量程信號轉換線性,避免臺階失真;

- 微分非線性(DNL) :典型值 ±0.2 LSB,優化弱信號采集時的精度穩定性;

- 偏移誤差 :CAL_OS=0 時 ±0.50 mV(典型值),CAL_OS=1 時 ±0.15 mV(典型值),支持 ±50 mV 偏移調整,溫度系數 ±1 μV/℃;

- 增益誤差 :默認配置下 ±0.05%(典型值),溫度系數 ±2 ppm/℃,全溫域增益穩定性高;

- 通道一致性 :雙通道全量程匹配誤差 < 0.625%(典型值),適配多通道同步采集場景。

(2)輸入與噪聲特性

- 輸入阻抗與 termination :單端輸入阻抗 50Ω(典型值),溫度系數 14.7 mΩ/℃,支持 AC/DC 耦合;輸入電容單端 0.4 pF,差分 0.04 pF,減少高頻信號損耗;

- 輸入噪聲 :噪聲譜密度(NSD)典型值 - 152 dBFS/Hz(單通道模式,AIN=-20 dBFS),0.1Hz~10Hz 低頻噪聲無顯著漂移,保障微弱射頻信號采集純凈度;

- 共模抑制比(CMRR) :60Hz 時典型值 104 dB,電源抑制比(PSRR)DC 模式 80~110 dB、AC 模式 - 72 dB(10kHz),減少共模干擾與供電噪聲影響。

2. 動態性能(關鍵指標適配高頻信號采集)

ADC12DJ5200-EP 的動態性能是射頻信號采集的核心保障,核心指標如下(默認配置:fCLK=5.12GHz,fIN=347MHz,AIN=-1 dBFS):

| 動態特性 | 關鍵指標(單通道模式) | 關鍵指標(雙通道模式) | 說明 |

|---|---|---|---|

| 動態范圍(DR) | 典型值 55.4 dBFS(fIN=347MHz),高至 56.5 dBFS(AIN=-12 dBFS) | 典型值 54.5 dBFS(fIN=347MHz),高至 56.1 dBFS(AIN=-12 dBFS) | 適配寬幅度射頻信號采集,弱信號識別能力強 |

| 無雜散動態范圍(SFDR) | 典型值 67 dBFS(fIN=347MHz),低至 46.2 dBFS(fIN=7997MHz) | 典型值 63 dBFS(fIN=347MHz),低至 46.2 dBFS(fIN=7997MHz) | 減少雜散信號對射頻信號的干擾,保障信號保真度 |

| 總諧波失真(THD) | 典型值 - 74 dBFS(2 次諧波,fIN=347MHz),3 次諧波 - 65 dBFS | 典型值 - 74 dBFS(2 次諧波,fIN=347MHz),3 次諧波 - 65 dBFS | 諧波失真低,適配高精度信號采集 |

| 建立時間 | 至 1/2 LSB 精度 | 至 1/2 LSB 精度 | 1 μs(典型值),快速響應瞬態射頻信號變化 |

| 通道串擾 | 通道間信號耦合 | 通道間信號耦合 | < -80 dB(典型值,fIN=347MHz),雙通道獨立采集無相互干擾 |

| 碼誤差率(CER) | 最大 10?1? Errors/sample | 最大 10?1? Errors/sample | 極低碼誤差,保障高速采樣數據可靠性 |

3. 時鐘與同步特性

內置高精度時鐘管理與多設備同步機制,減少外部時鐘器件依賴,適配復雜系統的時序協同需求:

(1)時鐘輸入與誤差補償

- 時鐘輸入 :采樣時鐘(CLK±)支持 800 MHz~5.2 GHz(雙通道)/10.4 GHz(單通道),建議使用低抖動晶體時鐘源(抖動 < 100 fs rms);支持 LVPECL 模式(DC 耦合)與 AC 耦合,AC 耦合時時鐘自偏置至 0.3V 共模電壓;

- 時鐘誤差補償 :采樣率轉換器(SRC)支持 ±244 ppm 補償范圍,7.45 ppb 分辨率,通過寄存器調整補償外部時鐘漂移;

- 同步功能 :支持 SYSREF 信號同步(差分輸入,內部 100Ω termination)與 SYNC 引腳同步,適配 JESD204C 子類 1 確定性延遲需求,多設備同步誤差 < 50 ns。

三、關鍵功能模塊詳解

1. 模擬前端與通道配置

器件前端集成輸入多路選擇器(MUX)與低噪聲緩沖器,適配不同幅度、不同頻率的射頻信號直接采集,減少外部放大電路需求:

(1)輸入多路選擇器(MUX)

支持雙通道獨立輸入、單通道合并輸入、交叉連接測試等模式,滿足不同場景的信號采集需求,具體模式如下:

| MUX 配置(SINGLE_INPUT/DUAL_INPUT) | 功能描述 | 應用場景 |

|---|---|---|

| SINGLE_INPUT=1(默認) | 單通道模式,僅 INA± 輸入 | 單路高頻信號高速采集(如雷達信號) |

| SINGLE_INPUT=3 | 雙輸入單通道模式(DUAL DES),INA±/INB± 分別采樣 | interleaved 前端的信號采集,采樣率疊加至 10.4 GSPS |

| DUAL_INPUT=0(默認) | 雙通道模式,INA±/INB± 獨立輸入 | 雙路獨立射頻信號同步采集(如多天線通信系統) |

| DUAL_INPUT=1 | 雙通道模式,INA±/INB± 交叉輸入 | 通道串擾測試與信號交叉驗證 |

(2)輸入保護與全量程調整

- 輸入保護 :內部集成鉗位二極管,支持峰值輸入電流 ±50 mA,峰值 RF 輸入功率(差分)26.5 dBm(ZS-DIFF=100Ω),避免過壓 / 過流損壞器件;

- 全量程調整 :通過 FS_RANGE_A/FS_RANGE_B 寄存器(16 位)調整輸入全量程電壓,范圍 500~1000 mVPP(默認 800 mVPP),適配不同幅度的射頻信號,優化信噪比(SNR)與失真性能。

2. 數字信號處理模塊

(1)數字下變頻器(DDC)

DDC 模塊支持頻率轉換與數據抽取,減少高速采樣后的數據流,適配后端信號處理需求,核心特性如下:

- 頻率轉換 :每通道集成 4 路數控振蕩器(NCO),支持快速頻率跳變(FFH),頻率分辨率通過 NCO_RDIV 寄存器調整,基礎頻率計算公式為fNCO ? =FREQx**× 2 ? 32 ×fCLK**?(FREQx 為 32 位頻率控制字);

- 抽取濾波 :支持 4x/8x/16x/32x 抽取,采用線性相位 FIR 濾波器,阻帶衰減 - 135 dB(奈奎斯特頻率),輸出 15 位復數數據(I/Q 通道),抽取后數據率降低,減少接口傳輸壓力;

- 增益控制 :DDC 增益可通過 BOOST 位調整,設置為 1 時增益提升 6.02 dB,需確保輸入信號無鏡像干擾以避免削波。

(2)可編程 FIR 濾波器(PFIR)

支持多模式頻率均衡,優化不同頻率信號的采集精度,具體模式如下:

| PFIR 模式 | 應用場景 | 關鍵參數 |

|---|---|---|

| 雙通道均衡模式 | 雙通道獨立信號頻率補償 | 每通道 9 個系數,中心抽頭 18 位分辨率(LSB=2?1?),非中心抽頭 12 位分辨率(LSB=2?1?~2?1?) |

| 單通道均衡模式 | 單通道信號頻率補償 | 9 個系數,參數同雙通道模式,適配單路高頻信號失真校正 |

| 時變濾波模式 | I/Q 信號校正、交錯前端補償 | 2 組系數交替切換,每組分 9 個系數,支持動態調整濾波特性 |

3. JESD204C 高速接口

采用 JESD204C 高速串行接口實現數據傳輸,支持高帶寬、低延遲與多設備同步,適配后端 FPGA / 處理器的高速數據接收需求:

(1)接口特性

- ** lanes 與速率 **:最多 16 路串行 lane(分 Link A/B,每路 8 lane),單 lane 最高速率 17.16 Gbps;支持 8B/10B(子類 1 兼容 JESD204B)與 64B/66B 編碼,64B/66B 模式支持前向糾錯(FEC)與循環冗余校驗(CRC-12),提升傳輸可靠性;

- 確定性延遲 :通過 SYSREF 信號復位本地多幀時鐘(LMFC/LEMC),實現多設備間確定性延遲,彈性緩沖釋放點可配置,避免數據傳輸時序偏差;

- 測試模式 :支持 PRBS(7/9/15/23/31 位)、時鐘圖案(16 位交替 0/1)、斜坡信號等測試模式,便于系統調試與鏈路驗證。

(2)數據格式

根據 JMODE 配置(共 71 種模式),數據幀結構靈活調整,例如:

- 單通道 10.4 GSPS 模式(JMODE=1):16 lane 傳輸,每 lane 速率 2 Gbps,幀格式含 12 位采樣數據 + 尾位,支持多幀(K=4~256)打包;

- 雙通道 5.2 GSPS+DDC 4x 抽取(JMODE=11):8 lane 傳輸,每 lane 速率 2.5 Gbps,幀格式含 15 位 I/Q 數據 + 2 位過 range 標志。

4. 校準與誤差補償

器件支持多種校準模式,保障全溫域、全采樣率下的精度穩定性,核心校準功能如下:

(1)校準模式

| 校準模式 | 觸發方式 / 功能 | 關鍵特性 |

|---|---|---|

| 前景校準(FG) | CALTRIG 引腳 / 軟件指令(CAL_SOFT_TRIG)觸發;校準增益、偏移、線性度 | 需 ADC 離線(輸出中值),校準時間短(典型值 < 1 ms),適合系統啟動或溫變后校準;支持偏移 ±50 mV、增益 ±0.05% 調整 |

| 背景校準(BG) | 軟件使能(CAL_BG=1);實時校準核心誤差 | ADC 持續工作(通過第三核心輪換校準),無數據中斷,功耗較前景模式高約 10%,適合連續信號采集場景 |

| 低功耗背景校準(LPBG) | 軟件使能(LP_EN=1);間歇校準 | 離線核心斷電,僅校準前喚醒,功耗較背景模式降低 30%,適配低功耗場景 |

(2)精細調整

- 偏移調整 :通過 OADJ 系列寄存器調整各通道輸入偏移,單通道模式需同步調整 ADC A/B 核心偏移,避免 fS/2 雜散;

- 增益匹配 :GAIN 系列寄存器調整各子 ADC 增益,通道間增益匹配誤差 < 0.2%;

- 時序校準 :TADJ 寄存器調整通道間采樣時序,減少交錯采樣導致的 fS/2-fIN 雜散。

四、典型應用場景與設計建議

1. 核心應用場景

ADC12DJ5200-EP 的核心價值在于 “高頻直接采樣 + 多通道同步”,典型應用包括:

- 雷達信號采集 :10.4 GSPS 單通道采樣 + 8GHz 帶寬,直接采集 X 波段(8~12GHz)雷達回波信號,DDC 抽取后降低數據率,適配實時信號處理;

- 通信系統 :雙通道 5.2 GSPS 同步采集,支持多天線 MIMO 架構,JESD204C 接口保障高速數據傳輸,NCO 實現頻率捷變;

- 測試測量設備 :8GHz 全功率帶寬 + 低噪聲特性,用于射頻信號分析儀,直接采集 L/S/C/X 波段信號,PFIR 優化不同頻率信號的失真。

典型應用電路示例(雷達信號采集)

- 電路結構 :雷達天線信號經巴倫轉換為差分信號,通過 100Ω 匹配電阻輸入 INA±,CLK± 采用 5.12 GHz 低抖動晶體時鐘(抖動 < 50 fs rms),JESD204C 接口連接 FPGA(如 Xilinx UltraScale+),SYSREF 信號實現多 ADC 同步;

- 關鍵器件 :參考電壓無需外部配置(內部帶隙基準,BG 引腳輸出 1.1V),模擬電源端并聯 1μF 鉭電容 + 0.1μF 陶瓷電容濾波,時鐘線串聯 50Ω 匹配電阻;

- 性能指標 :采集 1GHz 雷達信號時,SNR 55.8 dBFS,SFDR 67 dBFS,通道間同步誤差 < 50 ns,滿足雷達測距精度需求。

2. 關鍵設計建議

(1)電源與參考電壓設計

- 電源隔離 :模擬電源(VA19/VA11)與數字電源(VD11)獨立布線,單點連接至地平面;VA19/VA11 引腳就近并聯 1μF 鉭電容 + 0.1μF NP0 陶瓷電容,VD11 并聯 0.22μF 電容,減少電源噪聲耦合;

- 參考電壓優化 :內部帶隙基準(BG 引腳)輸出電流≤100μA,如需外部使用需加緩沖電路;避免 BG 引腳懸空, unused 時可接地或懸空(不影響內部參考)。

(2)PCB 布局與信號完整性

- 布局分區 :模擬區(INA±/INB±/CLK±/SYSREF±)與數字區(JESD204C lanes/SPI 接口)嚴格分離,AGND 與 DGND 單點連接;高頻信號(CLK±/JESD204C)采用微帶線布線,特性阻抗控制為 50Ω(單端)/100Ω(差分);

- 信號隔離 :CLK± 與 SYSREF± 布線間距≥3mm,避免平行布線;JESD204C lanes 采用等長布線(誤差 < 5mm),減少 lane 間延遲差;模擬輸入線(INA±/INB±)長度 < 10mm,降低信號損耗。

(3)同步與校準設計

- 多設備同步 :采用 SYSREF 差分輸入(AC 耦合),所有 ADC 的 SYSREF± trace 長度匹配(誤差 < 2mm);通過自動 SYSREF 校準(SRC_EN=1),對齊內部采樣時鐘,同步誤差 < 50 ns;

- 校準周期 :全溫域使用時,建議每 10℃觸發一次前景校準,或使能背景校準;低功耗場景優先選擇 LPBG 模式,平衡精度與功耗;

- 過 range 處理 :配置 OVR_T0(近滿量程,如 0xF2)與 OVR_T1(低幅度,如 0xAB)閾值,通過 ORA0/ORA1/ORB0/ORB1 引腳實時監測過 range 狀態,觸發系統增益調整。

-

adc

+關注

關注

100文章

7932瀏覽量

556747 -

編碼

+關注

關注

6文章

1040瀏覽量

57095 -

模數轉換器

+關注

關注

26文章

4096瀏覽量

130227 -

射頻采樣

+關注

關注

0文章

56瀏覽量

4741

發布評論請先 登錄

ADC12DJ3200AAV 射頻采樣模數轉換器 TI品牌 特性與應用

ADC12DJ4000RF 8GSPS單通道或4GSPS雙通道、12位射頻采樣模數轉換器(ADC)數據表

ADC12DJ5200-EP射頻采樣千兆采樣模數轉換器(ADC)數據表

ADC12DJ5200-SP 10.4GSPS單通道或5.2GSPS雙通道12位射頻采樣模數轉換器(ADC)數據表

ADC12DJ5200RF雙通道、12位射頻采樣模數轉換器(ADC)數據表

ADC12DJ2700 5.4GSPS單通道或2.7GSPS雙通道12位射頻采樣模數轉換器(ADC)數據表

ADC12DJ3200 6.4GSPS單通道或3.2GSPS雙通道12位射頻采樣模數轉換器(ADC)數據表

ADC08DJ5200RF射頻采樣千兆采樣模數轉換器(ADC)數據表

ADC12DJ5200-SEP雙通道12位射頻采樣模數轉換器(ADC)數據表

ADC12DJ5200SE 10.4GSPS單通道或5.2GSPS雙通道12位射頻采樣模數轉換器(ADC)數據表

ADC12DJ5200RF 具有雙通道 5.2 GSPS 或單通道 10.4 GSPS 的射頻采樣 12 位 ADC技術手冊

ADC12DJ5200-EP 12 位射頻采樣模數轉換器技術文檔總結

ADC12DJ5200-EP 12 位射頻采樣模數轉換器技術文檔總結

評論