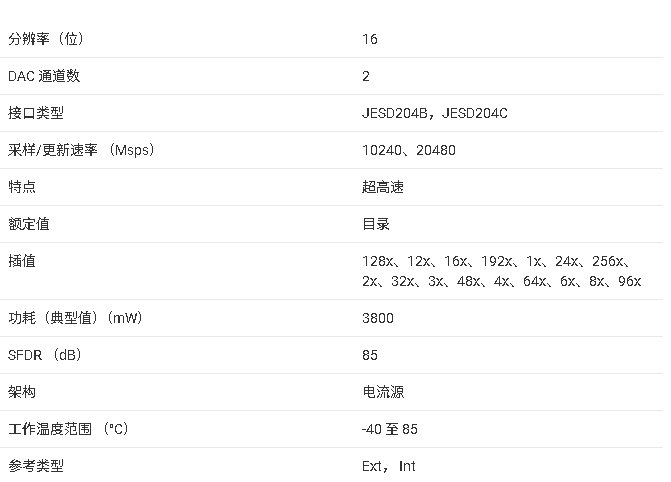

DAC39RF10EF 和 'RFS10EF 是一系列具有 16 位分辨率的雙通道和單通道數模轉換器 (DAC)。這些器件可用作非插值或插值DAC,用于直接RF采樣或復雜基帶信號生成。單通道的最大輸入數據速率為20.48GSPS,兩個通道的最大輸入數據速率為10.24GSPS。該器件可在超過 8GHz 的載波頻率下生成高達 10、2.73 或 1GHz 信號帶寬(8、11 和 16 位輸入分辨率)的信號,從而能夠通過 C 波段直接采樣并進入 X 波段。

*附件:dac39rf10ef.pdf

高采樣率、輸出頻率范圍、64 位 NCO 頻率分辨率和任何具有相位相干性的跳頻也使 DAC39RF10EF 和 'RFS10EF 能夠進行任意波形生成 (AWG) 和直接數字合成 (DDS)。

JESD204B和JESD204C兼容的串行接口具有 16 個接收器對,速度高達 12.8Gbps。該接口JESD204B,JESD204C符合子類 1 標準,可通過使用 SYSREF 實現確定性延遲和多設備同步。

特性

- 10.24/20.48GSPS,多奈奎斯特DAC內芯

- 最大輸入數據速率與DAC分辨率的關系:

- 16 位:1.22GSPS 復合體

- 11 位:3.41GSPS 復合體

- 9 位,單通道,DES 模式:15.12GSPS

- 8 位,單通道,DES 模式:20.48GSPS

- 9 位,雙通道:7.56GSPS/通道

- 8 位,雙通道,10.24GSPS/通道

- 輸出帶寬 (–3dB):12GHz

- fOUT = 2.997 GHz、DES2XL模式、DEM/抖動開啟時的性能

- 本底噪聲(小信號):–150dBFS/Hz

- SFDR (–0.1dBFS):77dBc

- IMD3(每音 –7dBFS):–69dBc

- 四個集成數字上變頻器 (DUC)

- 插值:1x、2x、3x、4x、6x、8x、12x ...256 倍

- 用于 I/Q 輸出的復雜基帶 DUC

- 復雜到實數上轉換,用于雙通道直接射頻采樣

- 64 位頻率分辨率 NCO

- 快速重新配置接口,實現快速跳頻

- 4位數據,200MHz時鐘

- 60 ns 重新配置(32 位頻率)

- 任何具有相位相干性的跳頻

- JESD204C界面

- 用于自動 SYSREF 時序校準的 SYSREF 窗口

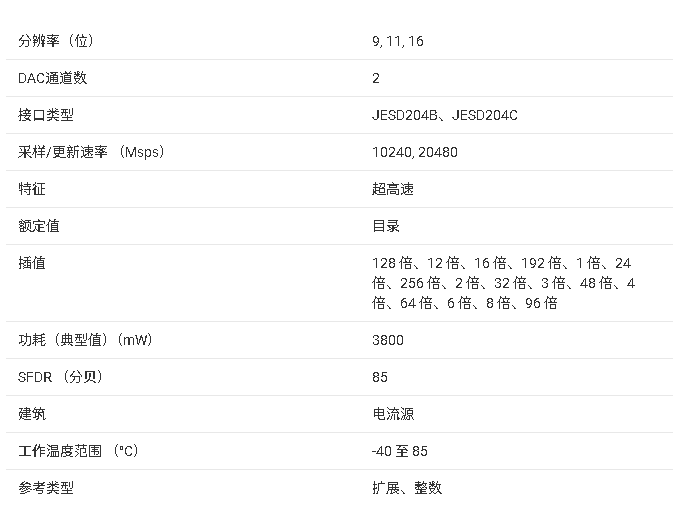

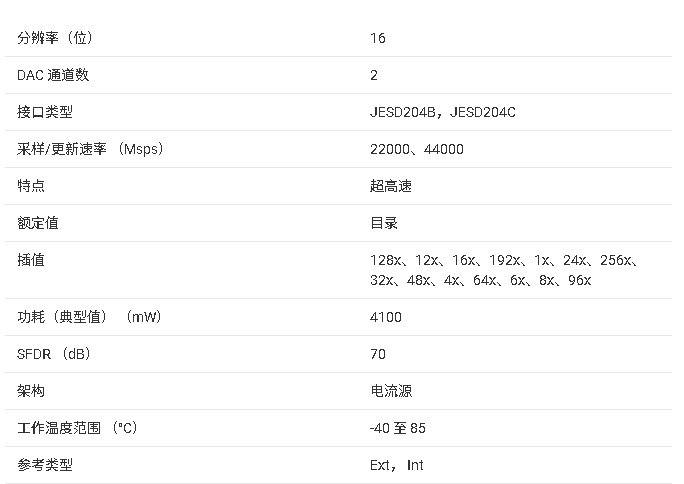

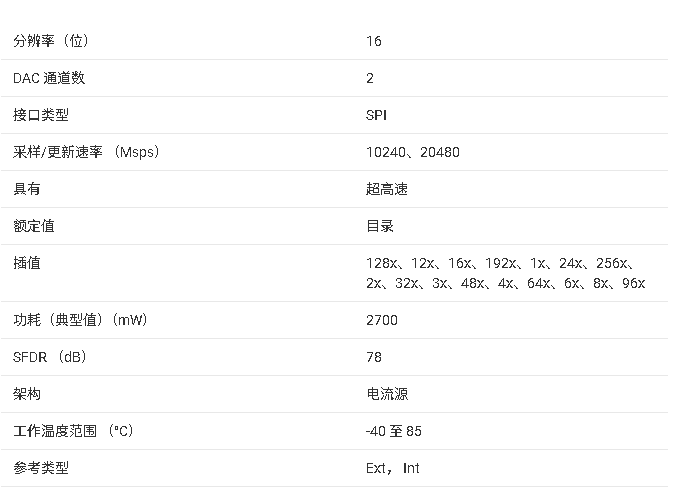

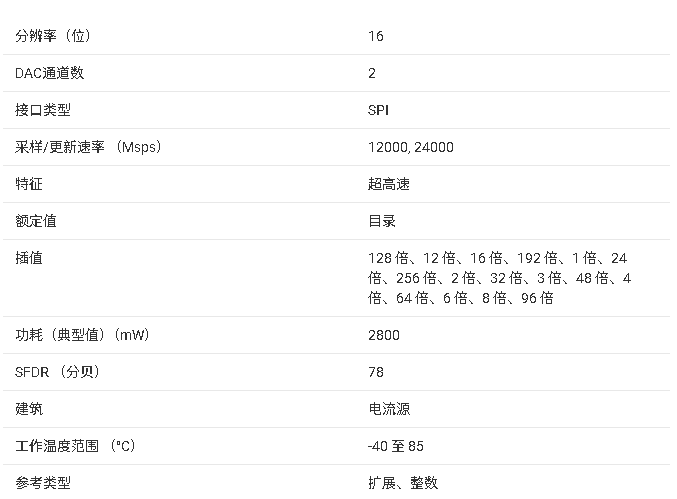

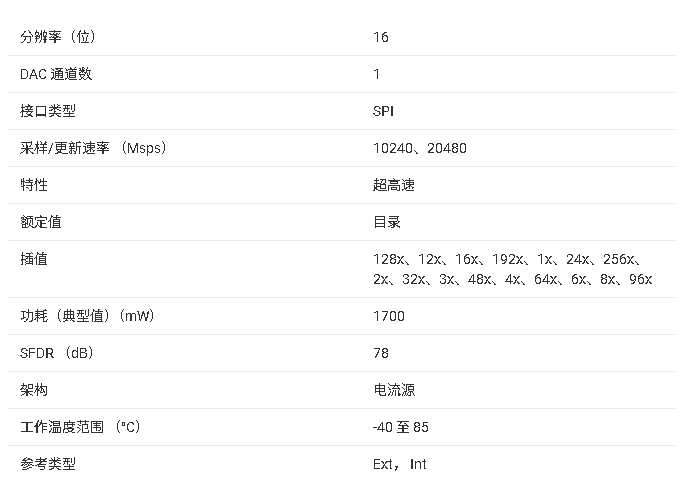

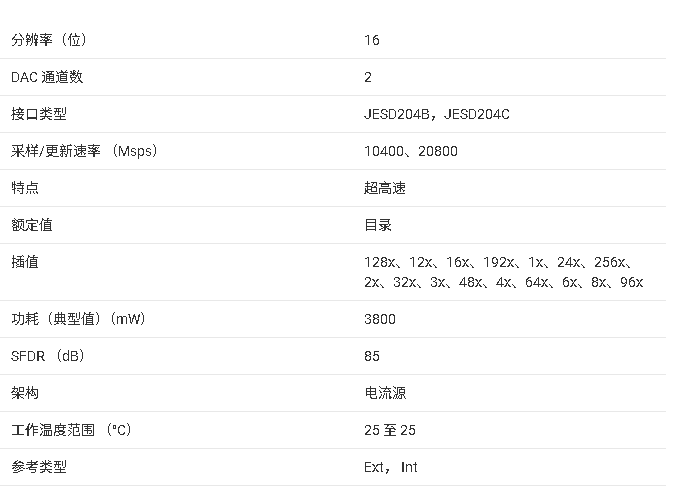

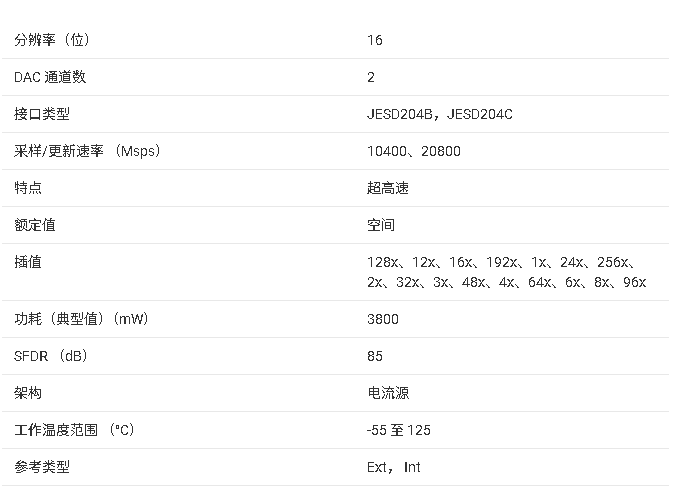

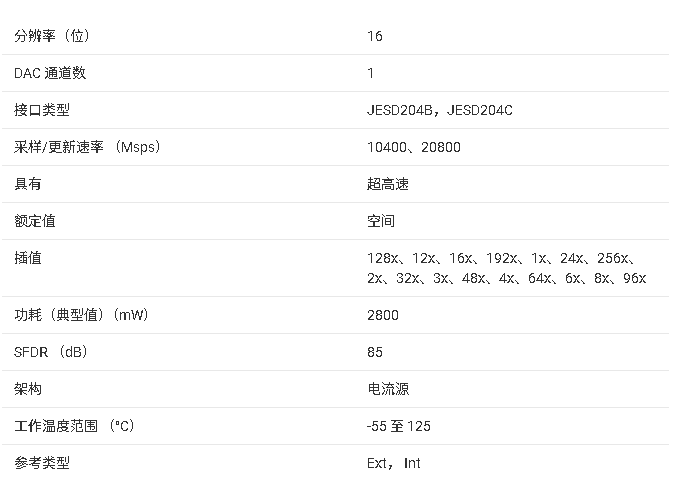

參數

方框圖

一、產品概述

DAC39RF10EF 與 DAC39RFS10EF 是德州儀器推出的16 位高采樣率數模轉換器(DAC) ,核心定位為多奈奎斯特頻段信號生成,適配任意波形發生器(AWG)、無線通信測試儀等高端射頻場景,可直接生成載波頻率超 8GHz 的信號,覆蓋 C 波段至 X 波段。兩款器件均采用 256 引腳 FCBGA 封裝(17mm×17mm,1mm 間距),支持 - 40~85°C 工作溫度,核心差異為通道數量:DAC39RF10EF 為雙通道設計,DAC39RFS10EF 為單通道設計,均具備高帶寬、低噪聲、相位相干跳頻等關鍵特性。

二、核心特性

(一)高采樣率與寬頻帶輸出

- 采樣率與分辨率適配支持動態調整輸入分辨率與采樣率,平衡帶寬與性能,具體參數如下:

- 8 位分辨率:單通道雙沿采樣(DES)模式下最高 20.48GSPS,雙通道 10.24GSPS / 通道;

- 9 位分辨率:單通道 DES 模式下最高 15.12GSPS,雙通道 7.56GSPS / 通道;

- 11 位分辨率:單通道 DES 模式下最高 3.41GSPS(復信號);

- 16 位分辨率:單通道最高 1.22GSPS(復信號),雙通道 6.2GSPS / 通道;

- 模擬輸出帶寬(-3dB):12GHz,8 位分辨率時可生成最高 10GHz 帶寬信號,16 位分辨率時可生成 1GHz 帶寬信號。

- 卓越動態性能在輸出頻率 2.997GHz、DES2XL 模式、DEM/Dither 開啟條件下,關鍵指標如下:

- 噪聲基底(小信號):-150dBFS/Hz;

- 無雜散動態范圍(SFDR,-0.1dBFS 輸入):77dBc;

- 三階互調失真(IMD3,-7dBFS 雙音輸入):-69dBc;

- 附加相位噪聲(10kHz 偏移,DES 模式):-148.1dBc/Hz。

(二)靈活的數字信號處理能力

- 集成數字上變頻器(DUC) 內置 4 個獨立 DUC,支持 1×、2×、3×、4×…256× 插值,可實現:

- 快速重配置與跳頻提供 4 位數據 + 200MHz 時鐘的快速重配置(FR)接口,32 位頻率配置僅需 60ns,支持任意頻率跳頻且保持相位相干,適配雷達、通信系統動態頻率切換需求。

(三)高速 JESD204C 接口

- 接口規格 :支持最多 16 條 SerDes lanes,單 lane 最高速率 12.8Gbps,兼容 8b/10b(≤2Gbps 強制使用)與 64b/66b(強制加擾)編碼,64b/66b 編碼提升帶寬效率;

- 同步特性 :符合 JESD204C Class C-S、Subclass-1 標準,支持確定性延遲與多器件同步,內置 SYSREF 窗口校準功能,自動優化 SYSREF 采樣時序,確保多器件協同;

- 抗干擾設計 :集成片內 AC 耦合電容與 100Ω 差分終端,減少外部電路復雜度,提升信號完整性,支持 SerDes 交叉開關(Crossbar)靈活映射物理 lane 與邏輯 lane,簡化 PCB 布線。

三、器件信息與電氣規格

(一)型號差異與擴展系列

| 型號 | 通道數 | 最高采樣率(單 / 雙沿) | 抗輻射特性 | JESD 接口 |

|---|---|---|---|---|

| DAC39RF10EF | 2 | 10.24/20.48 GSPS | 無 | 支持(輸入速率受限) |

| DAC39RFS10EF | 1 | 10.24/20.48 GSPS | 無 | 支持(輸入速率受限) |

| DAC39RF10 | 2 | 10.24/20.48 GSPS | 無 | 支持 |

| DAC39RFS10 | 1 | 10.24/20.48 GSPS | 無 | 支持 |

| DAC39RF10-SP | 2 | 10.4/20.8 GSPS | 120MeV SEL/SEFI,300krad TID | 支持 |

| DAC39RFS10-SP | 1 | 10.4/20.8 GSPS | 120MeV SEL/SEFI,300krad TID | 支持 |

| DAC39RF10-SEP | 2 | 10.4/20.8 GSPS | 43MeV SEL/SEFI,30krad TID | 支持 |

| DAC39RFS10-SEP | 1 | 10.4/20.8 GSPS | 43MeV SEL/SEFI,30krad TID | 支持 |

(二)核心電氣參數(TA=25°C,VDD 標稱值)

| 參數 | 條件 | DAC39RF10EF(雙通道) | DAC39RFS10EF(單通道) | 單位 |

|---|---|---|---|---|

| 微分非線性(DNL) | 全溫度范圍 | ±2.2 | ±2.2 | LSB |

| 積分非線性(INL) | 全溫度范圍 | ±9 | ±9 | LSB |

| 滿量程輸出電流(IFS_SWITCH) | RBIAS=3.6kΩ,CUR_2X_EN=1 | 20.5(典型) | 20.5(典型) | mA |

| 靜態輸出電流(ISTATIC) | RBIAS=3.6kΩ | 4.8(典型) | 4.8(典型) | mA |

| 輸出電容(COUT) | 單端對地 | 0.25 | 0.25 | pF |

| JESD lane 速率 | 8b/10b 編碼 | 0.78125~12.8 | 0.78125~12.8 | Gbps |

| 總功耗(PDIS) | 10.24GSPS,NRZ 模式 | 3500(典型) | 2160(典型) | mW |

(三)熱學特性(256 引腳 FCBGA)

| 熱參數 | 值 | 單位 |

|---|---|---|

| 結到環境熱阻(RθJA) | 15.8 | °C/W |

| 結到頂部外殼熱阻(RθJC (top)) | 0.9 | °C/W |

| 結到板熱阻(RθJB) | 4.2 | °C/W |

| 結到頂部特征參數(ΨJT) | 0.4 | °C/W |

| 結到板特征參數(ΨJB) | 4.2 | °C/W |

四、功能模塊詳解

(一)DAC 核心與輸出模式

多奈奎斯特輸出模式支持 4 種輸出模式,適配不同頻段需求,核心特性如下表:

模式 是否通直流 最優頻率范圍 峰值輸出功率 備注 非歸零(NRZ) 是 0~FCLK/2 0dBFS 標準零階保持模式,適用于 1st 奈奎斯特區 歸零(RTZ) 是 0~FCLK -6dBFS 采樣周期后半段歸零,改善 2nd 奈奎斯特區性能 射頻(RF) 否 FCLK/2~FCLK -2.8dBFS 樣本中途反轉,2nd 奈奎斯特區平坦度最優 雙沿采樣(DES) 是 0~FCLK 0dBFS CLK 升降沿均輸出樣本,采樣率翻倍,存在占空比鏡像(FCLK-FOUT) 電流調整與非線性優化

(二)數字上變頻(DUC)與 NCO

- DUC 功能每通道 DUC 支持多速率插值與復信號混頻,具體特性:

- 插值范圍:2×~256×,支持多級濾波(如 2× 用 fir1、4× 用 fir1+fir2),通帶紋波 <0.01dB,阻帶衰減> 90dB;

- 信號合成:4 個 DUC 輸出可通過通道綁定器(Channel Bonder)按 1×、0.5×、0.25× 比例縮放后求和,避免飽和,支持實信號(最多 4 個 DUC)或復信號(最多 2 個 DUC)輸出。

- NCO 特性

- 頻率分辨率:64 位,支持相位連續(NCO_CONT=1)、相位相干(NCO_CONT=0)、相位同步(NCO_AR=1)三種更新模式;

- 同步觸發:可通過 JESD204C 數據 LSB、SYSREF 或 SPI 寄存器觸發同步, latency 可通過 Excel 工具計算,多器件同步時需確保 SYSREF 周期為 CLK 周期 16 倍以上且匹配 LMFC 周期。

(三)JESD204C 接口與同步

- 接口配置

- 編碼支持:8b/10b(兼容 JESD204B)與 64b/66b(強制加擾),后者需配置 ES=1(加擾使能);

- lane 映射:16 條物理 lane 可通過 LANE_SEL 寄存器靈活映射到邏輯 lane,簡化 PCB 布線;

- 多器件同步:Subclass-1 模式下通過 SYSREF 校準 LMFC(多幀時鐘),彈性緩沖區(EB)釋放點通過 RBD 參數調節,需確保數據 arrival 時間在有效窗口內,避免溢出 / 下溢。

- 關鍵時序

- SYSREF 采樣:通過 SYSREF_POS 寄存器檢測 SYSREF 與 CLK 的相對位置,SYSREF_ZOOM=1 時步長 9ps,建議選擇有效窗口中間位置作為采樣點(如 SYSREF_SEL=8~9);

- SerDes 時鐘:VCO 頻率需在 1.5625~3.2GHz 范圍內,通過 REFDIV/MPY/RATE 寄存器配置 PLL,例如 8b/10b 編碼、FCLK=10.24GHz 時,REFDIV=0x10、MPY=0x10、RATE=0x0,lane 速率 6.25~12.8Gbps。

(四)電源與功耗管理

- 供電配置 :需多組獨立電源,包括模擬 1.8V(VDDA18A/B)、負模擬 1.8V(VEEAM18/BM18)、數字 1.0V(VDDDIG/VDDE/A/B)、時鐘 1.0V(VDDCLK10)等,各組電源需單獨去耦(0.1μF 陶瓷電容 + 1μF 鉭電容);

- 功耗優化 :支持 14 種功耗模式,睡眠模式(MODE [1:0]=11b)功耗僅 171mW,雙通道 10.24GSPS NRZ 模式功耗約 3500mW,單通道可低至 2160mW,可通過關閉閑置通道、降低采樣率進一步優化。

五、典型應用場景

(一)任意波形發生器(AWG)

- 應用架構 :采用 DAC39RFS10EF 單通道,DES2XL 模式(20.48GSPS)、8 位分辨率,生成 10GHz 帶寬復雜波形;通過 FR 接口實現 60ns 快速頻率跳變,滿足動態波形生成需求;

- 關鍵配置 :DUC 插值設為 2×,NCO 啟用相位相干模式(NCO_CONT=0),輸出模式設為 NRZ,啟用相位相干更新;JESD204C 用 16 條 lane、64b/66b 編碼,RBD=46(確保確定性延遲);

- 性能優化 :電源端串聯 10μH 共模電感,模擬地與數字地單點連接,啟用 DEM/Dither(DEM_ADJ=0),噪聲基底控制在 - 150dBFS/Hz 以下。

(二)無線通信測試儀

- 應用架構 :DAC39RF10EF 雙通道,每通道通過 DUC 將基帶 I/Q 信號上變頻至 5~8GHz,NCO 頻率分辨率確保多通道相位同步;JESD204C 用 8 條 lane、64b/66b 編碼,單 lane 速率 10.56Gbps,滿足 16 位 10.24GSPS 采樣需求;

- 關鍵配置 :輸出模式設為 RF 模式(優化 2nd 奈奎斯特區),DUC_GAIN=0(0dB 縮放),滿量程電流 41mA(CUR_2X_EN=1);通過 SYSREF 同步多片 DAC,SYSREF_SEL=6~7,確保陣元間相位差 < 1ns;

- 可靠性設計 :輸入串聯 1kΩ 電阻限制過流,EXTREF 引腳使用內置基準(EXTREF_EN=0)并并聯 10μF 電容,VDDCLK10 采用 1.0V 線性穩壓器,減少時鐘噪聲對相位噪聲的影響。

六、設計指南

(一)PCB 布局與防護

- 分區設計

- 模擬區域(DACOUTA/B±、REFIO)與數字區域(JESD lane、SPI)分開布局,間距≥1mm;

- 高頻信號(CLK±、SYSREF±)采用差分走線,長度差 < 1mm,阻抗匹配 100Ω,遠離電源走線;

- 熱焊盤(Thermal Pad)需連接≥20mm2 銅皮,打 4 個 0.3mm 過孔(間距 1mm)至內層地平面,滿負荷工作時結溫≤105°C(環境溫度 50°C)。

- ESD 與 EMC 防護

- ESD 防護:器件 HBM ESD±1000V、CDM±250V,調試時需佩戴防靜電手環,PCB 預留 TVS 管位置(如 SMBJ18CA)用于輸入過壓保護;

- EMC 優化:電源端并聯 10μF 鉭電容 + 0.1μF 陶瓷電容,JESD204C 線使用屏蔽雙絞線,滿足 EN 61326-1 工業 EMC 標準。

(二)初始化與配置流程

- 上電序列

- 先加模擬電源(VDDA18A/B、VEEAM18/BM18),后加數字電源(VDDDIG、VDDIO),最后加時鐘電源(VDDCLK10/18);

- 復位(RESETB)拉低≥100ns,釋放后等待 5ms(電源穩定);

- 配置 JESD204C:設置 JMODE(如 JMODE4 對應 16 位、1 lane / 流)、JESD_M(流數量)、JCTRL(編碼方式,JENC=1 為 64b/66b),啟用 JESD_EN=1。

- 核心配置

- 輸出模式:通過 MXMODE 寄存器設置,如 MXMODE0=3(DES2X 模式)、MXMODE1=6(禁用 DACB);

- DUC 與 NCO:DUC_L=7(16× 插值)、NCO_EN=1(啟用 NCO 混頻)、FR_EN=0(使用 SPI 配置 NCO);

- 同步校準:SYSREF_CTRL 寄存器設置 SYSREF_ZOOM=1、SYSREF_PS_EN=1,讀取 SYSREF_POS 確定 SYSREF_SEL,配置 RBD=46(彈性緩沖區釋放點)。

七、器件與文檔支持

(一)訂購信息

| 訂購型號 | 狀態 | 封裝 | 數量 / 載體 | 工作溫度 | 關鍵參數 |

|---|---|---|---|---|---|

| DAC39RF10EFYBGA | 量產 | 256 引腳 FCBGA(YBH) | 3000 片 / 大卷帶 | -40~85°C | 雙通道,10.24/20.48GSPS |

| DAC39RFS10EFYBGA | 量產 | 256 引腳 FCBGA(YBH) | 3000 片 / 大卷帶 | -40~85°C |

-

dac

+關注

關注

44文章

2713瀏覽量

197066 -

數模轉換器

+關注

關注

14文章

1296瀏覽量

85733 -

基帶信號

+關注

關注

0文章

38瀏覽量

11489 -

載波頻率

+關注

關注

1文章

21瀏覽量

10562

發布評論請先 登錄

請問DAC39RF10B的新版說明書里面INL的單位Codes是怎么定義的?

請問DAC39J84EVM板怎么多路輸出?

DAC39J84 四通道 16 位 2.8 GSPS 數模轉換器

DAC39RF10、DAC39RFS10 10.24、20.48GSPS 16位雙通道和單通道多奈奎斯特數模轉換器(DAC)數據表

DAC39RF10EF DAC39RFS10EF雙通道和單通道數模轉換器(DAC)數據表

DAC39RF12、DAC39RFS12雙通道和單通道數模轉換器(DAC)數據表

DAC39RF20核心信息總結

DDS39RF10產品技術文檔總結

DDS39RF12 與 DDS39RFS12 產品技術文檔總結

DDS39RFS10 產品技術文檔總結

DAC39RFx10-SP/SEP 系列數模轉換器技術文檔總結

DAC39RFx10 系列產品技術文檔總結

DAC39RFS10-SEP產品技術文檔總結

DAC39RF10EF/DAC39RFS10EF 技術文檔總結

DAC39RF10EF/DAC39RFS10EF 技術文檔總結

評論