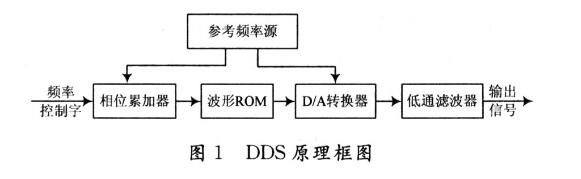

DDS39RF12 和 'RFS12 是一系列雙通道和單通道直接數字合成器,具有 16 位分辨率的數模轉換器 (DAC)。高采樣率、輸出頻率范圍、64 位 NCO 頻率分辨率和任何具有相位相干性的跳頻使該器件能夠進行任意波形生成 (AWG) 和直接數字合成 (DDS)。

*附件:dds39rf12.pdf

這些器件還可用作插值DAC,用于窄帶直接RF采樣或復雜基帶信號生成。單通道的最大輸入數據速率為775MSPS,雙通道的最大輸入數據速率為388MSPS。這些器件可以在超過 10GHz 的載波頻率下生成高達 620MHz 信號帶寬(16 位輸入分辨率)的信號,從而能夠通過 C 波段和 X 波段直接采樣。

JESD204B和JESD204C兼容的串行接口有 2 個接收器對,每個接收器對的速率高達 12.8Gbps。該接口JESD204B,JESD204C符合子類 1 標準,可通過使用 SYSREF 實現確定性延遲和多設備同步。

特性

- 16位、12至24GSPS、多奈奎斯特DAC內核

- 最大輸入數據速率:

- 16 位、單通道復數 I/Q:775MSPS

- 16 位、雙通道復數 I/Q:388MSPS

- 輸出帶寬 (-3dB):12GHz

- fOUT = 2.997GHz、DES2XL模式、DEM和抖動關閉時的性能

- 本底噪聲(小信號):-154dBFS/Hz

- SFDR (-0.1dBFS):68dBc

- IMD3(每音-7dBFS):-74dBc

- 加相位噪聲,10kHz 偏移:-138dBc/Hz

- 四個集成數字上變頻器 (DUC)

- 插值:4x、6x、8x、12x ...256 倍

- 用于 I/Q 輸出的復雜基帶 DUC

- 復雜到實數上轉換,用于雙通道直接射頻采樣

- 64 位頻率分辨率 NCO

- 快速重新配置接口,實現快速跳頻

- 4位數據,200MHz時鐘

- 60ns 重新配置(32 位頻率)

- 任何具有相位相干性的跳頻

- JESD204C界面

- 用于自動 SYSREF 時序校準的 SYSREF 窗口

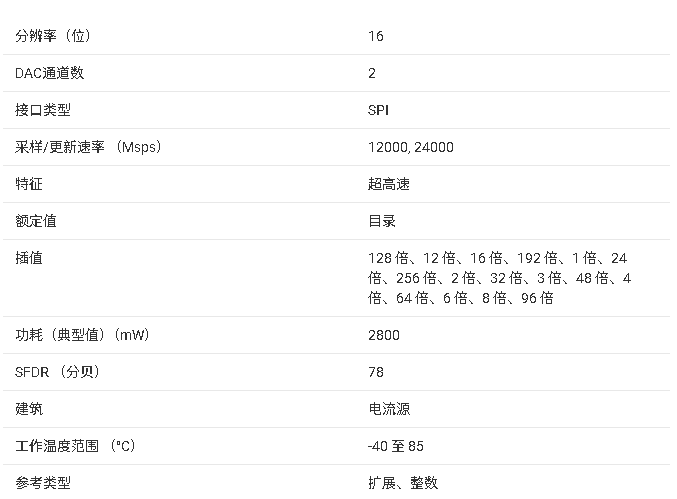

參數

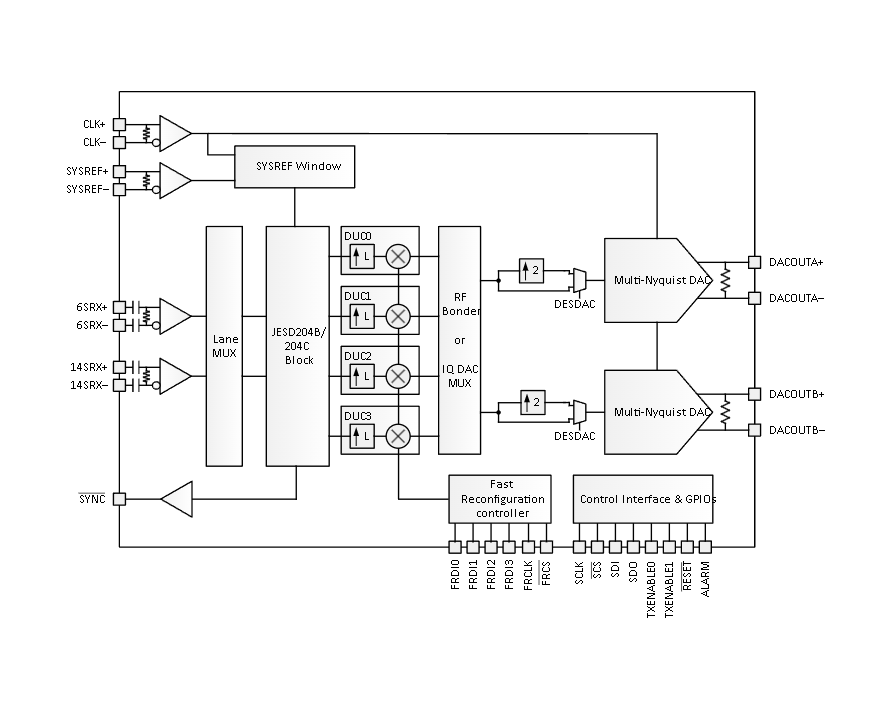

方框圖

DDS39RF12 與 DDS39RFS12 是德州儀器(TI)推出的高采樣率直接數字合成器(DDS)系列產品,搭載 16 位多奈奎斯特 DAC 內核,具備靈活的數字上變頻器(DUC)、高速 JESD204C 接口及精準數控振蕩器(NCO),可生成超寬頻帶信號,適用于衛星通信(SATCOM)、相控陣天線、合成孔徑雷達(SAR)激勵器、無線通信測試儀等對頻率精度與信號帶寬要求嚴苛的場景。兩款器件核心架構一致,僅通道數量存在差異,可根據應用對信號輸出通道的需求靈活選型。

一、核心特性與器件差異

1. 共性核心特性

- 高采樣與帶寬能力 :16 位多奈奎斯特 DAC 內核,采樣率覆蓋 12~24GSPS(雙沿采樣模式下);模擬輸出帶寬(-3dB)達 12GHz,支持 C 波段至 X 波段直接信號生成,可處理最高 600MHz 帶寬的 16 位分辨率輸入信號。

- 卓越信號性能 :在輸出頻率 2.997GHz、DES2XL 模式(禁用 DEM/Dither)下,小信號噪聲底低至 - 154dBFS/Hz,無雜散動態范圍(SFDR,-0.1dBFS)達 68dBc,三階互調失真(IMD3,-7dBFS 雙音)為 - 74dBc;10kHz 偏移處附加相位噪聲低至 - 138dBc/Hz,確保信號純凈度。

- 靈活數字上變頻(DUC) :集成 4 個獨立 DUC,插值倍數可配置為 4x、6x、8x…256x,支持復數基帶至實信號上變頻,適配雙通道直接射頻采樣;支持復數 / 實數輸出格式切換,復數輸出時最多啟用 2 個 DUC,實數輸出時最多啟用 4 個 DUC,可通過通道綁定器(Channel Bonder)將多 DUC 輸出求和后送入 DAC。

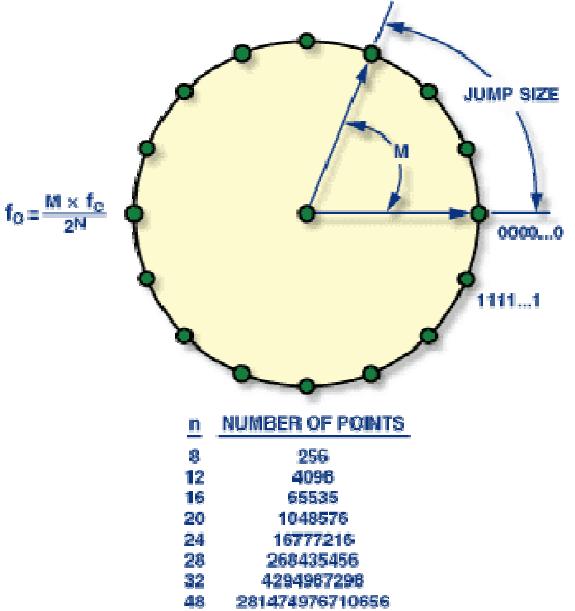

- 高精度 NCO 功能 :64 位 NCO 支持頻率范圍 - FCLK/2~+FCLK/2,相位分辨率 16 位,支持三種跳頻模式:

- 相位連續模式 :頻率漸變無相位突變,避免信號失真;

- 相位相干模式 :基于 SYSREF 同步,多次跳頻后相位可恢復初始狀態;

- 相位同步模式 :更新頻率時復位累加器,適用于多器件 NCO 同步。

- 高速 JESD204C 接口 :支持 2 條 SerDes 通道,單通道速率最高 12.8Gbps,兼容 8b/10b(可選加擾)與 64b/66b(強制加擾)編碼;符合 Class C-S subclass-1 標準,支持確定性延遲與多器件同步,內置 SYSREF 窗口功能,可自動校準 SYSREF 時序,補償溫度與電壓導致的時序偏移。

- 快速重配置與低功耗優化 :提供快速重配置接口(FR),支持 200MHz 時鐘下 4 位數據傳輸,32 位頻率配置僅需 60ns,且跳頻保持相位相干;支持睡眠模式,總功耗低至 171mW,適配低功耗場景。

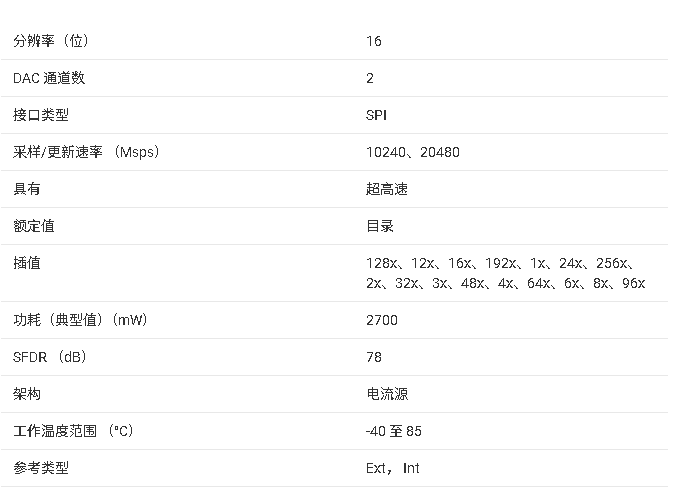

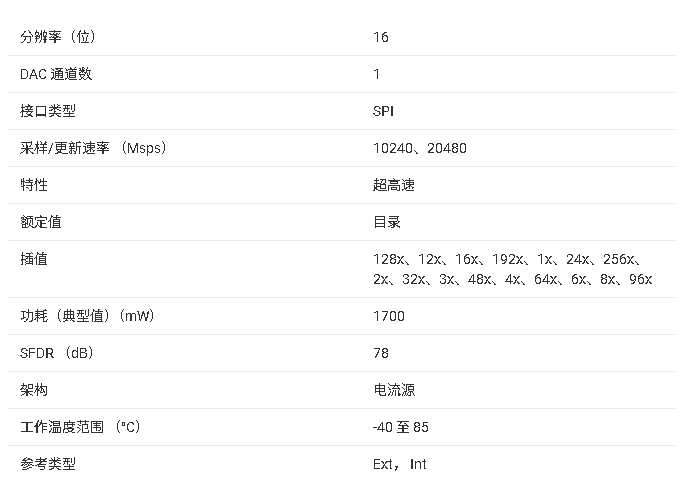

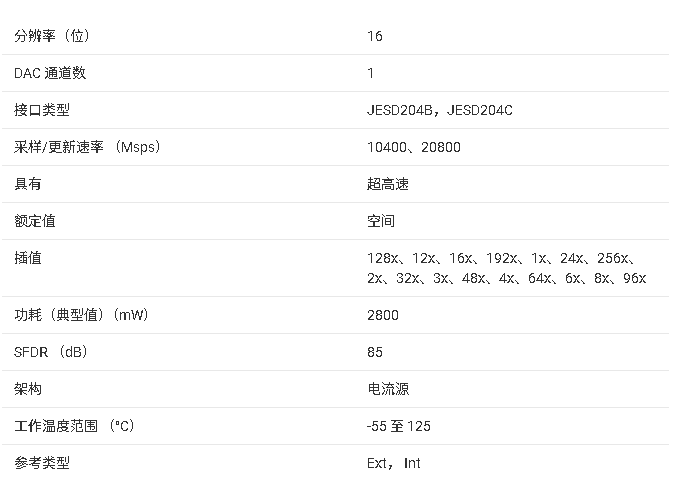

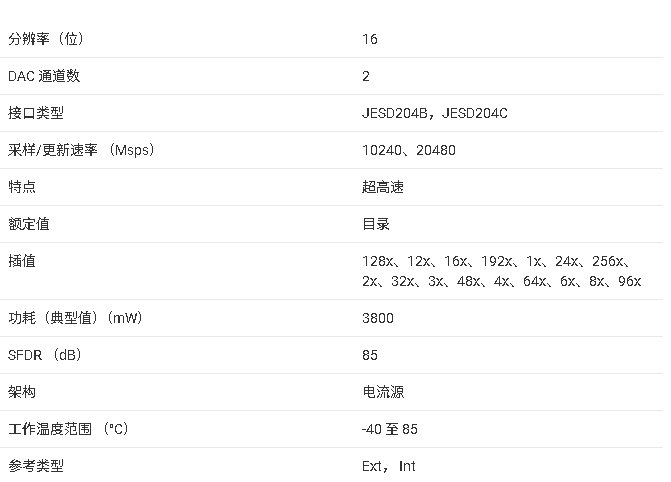

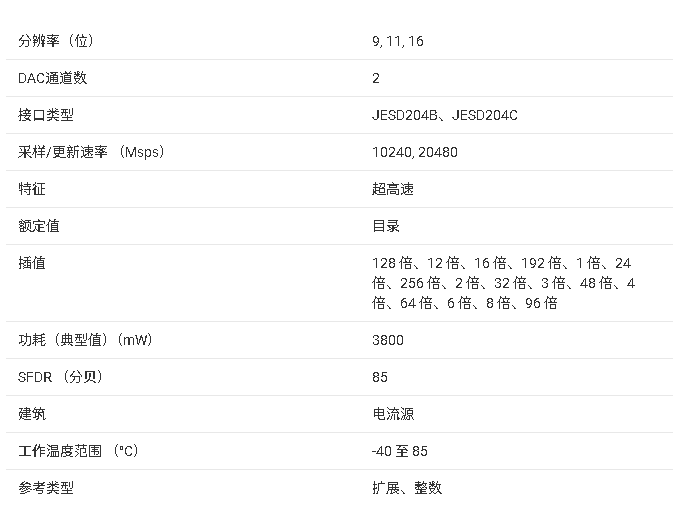

2. 器件差異(DDS39RF12 vs DDS39RFS12)

| 參數 | DDS39RF12 | DDS39RFS12 |

|---|---|---|

| 通道數量 | 2 個(雙通道) | 1 個(單通道) |

| 最大輸入數據率(16 位復數 I/Q) | 388MSPS(雙路并行) | 775MSPS(單路) |

| 典型功耗(12GSPS,DDS 模式) | 2831mW(雙 DAC 工作) | 1837mW(單 DAC 工作) |

| 適用場景 | 需雙路獨立信號輸出場景,如相控陣天線雙極化控制 | 單路高帶寬信號生成場景,如單通道雷達激勵 |

二、封裝與引腳功能

1. 封裝規格

兩款器件均采用 17mm×17mm 256 引腳 FCBGA 封裝(1mm 引腳間距),內置裸露熱焊盤(需接地優化散熱),熱阻參數為:結到環境(RθJA)15.8°C/W、結到板(RθJB)4.2°C/W、結到殼頂(RθJC (top))0.9°C/W;工作溫度范圍 - 40°C~105°C(環境溫度),結溫最高 115°C,MSL 等級 3(260°C 峰值回流焊,168 小時濕度敏感等級)。

2. 關鍵引腳分類與功能

| 引腳類別 | 關鍵引腳示例 | 類型 | 核心功能 |

|---|---|---|---|

| 模擬輸出 | DACOUTA±、DACOUTB± | 模擬輸出 | DAC 通道 A/B 差分模擬輸出,需符合輸出合規電壓以保證性能;B 通道引腳僅 DDS39RF10 具備 |

| 時鐘與同步輸入 | CLK±、SYSREF± | 數字輸入 | CLK± 為差分采樣時鐘(內置 100Ω 差分端接,自偏置,需 AC 耦合);SYSREF± 為 JESD204C 同步信號(內置 100Ω 端接) |

| SerDes 接口 | 6SRX±、14SRX± | 數字輸入 | JESD204C 串行數據接收通道,內置 AC 耦合電容與 100Ω 差分端接 |

| 控制與配置接口 | SCLK、SCS、SDI/SDO | 數字 I/O | SPI 配置接口(SCS 低有效,SCLK 時鐘,SDI 數據輸入,SDO 數據輸出);FRDI0~3、FRCLK/FRCS 為快速重配置接口 |

| 電源與地 | VDDA18A/B、VEEAM18/B18 | 電源輸入 | VDDA18A/B 為 1.8V 模擬電源(通道 A/B),VEEAM18/B18 為 - 1.8V DAC 電流源偏置電源;AGND(模擬地)、DGND(數字地)、VSSCLK(時鐘地)需獨立布線 |

三、電氣規格與工作條件

1. 電源要求

| 電源類型 | 電壓范圍 | 典型值 | 備注 |

|---|---|---|---|

| VDDA18A/VDDA18B | 1.71V~1.89V | 1.8V | 模擬電源(通道 A/B),可合并供電但可能增加通道串擾(XTALK) |

| VEEAM18/VEEBM18 | -1.89V~-1.71V | -1.8V | 通道 A/B DAC 電流源偏置電源,獨立供電可優化串擾性能 |

| VDDCLK10 | 0.95V~1.05V | 1.0V | 時鐘分配路徑電源,需與數字電源隔離,避免噪聲影響相位噪聲性能 |

| VDDDIG | 0.95V~1.05V | 1.0V | 數字模塊電源,需獨立去耦,與模擬電源分開布線 |

| VDDIO/VDDR18 | 1.71V~1.89V | 1.8V | VDDIO 為 CMOS I/O 電源,VDDR18 為 SerDes 接收器電源 |

2. 關鍵電氣參數(典型值,TA=25°C,FCLK=12GHz,IFS_SWITCH=20.5mA)

- DAC 核心性能 :16 位分辨率(無失碼),差分非線性(DNL)±2.2LSB,積分非線性(INL)±9LSB;滿量程輸出電流(IFS_SWITCH)可通過 RBIAS 電阻與寄存器配置,典型值 20.5mA(3.6kΩ 電阻),溫度漂移 - 8.6μA/°C。

- 輸入輸出特性 :模擬輸入電容 0.5pF(時鐘 / SYSREF 引腳),過壓防護峰值功率 10dBm(100Ω 端接);DAC 輸出差分端接電阻 102Ω,溫度系數 - 9.6mΩ/°C;參考電壓(VREF)典型值 0.9V,溫漂 45ppm/°C。

- 功耗 :DDS39RF12 在 12GSPS、雙 DAC 工作(Power Mode 1)時,總功耗典型值 2831mW;DDS39RFS12 單 DAC 工作(Power Mode 5)時,總功耗典型值 1837mW;睡眠模式功耗低至 171mW。

四、核心功能與工作模式

1. DAC 輸出模式

器件支持多種 DAC 輸出模式,適配不同頻率范圍與信號特性需求,模式差異如下表:

| DAC 輸出模式 | 是否支持 DC | 最優頻率范圍 | 峰值輸出功率 | 核心特點 |

|---|---|---|---|---|

| NRZ(非歸零) | 是 | 0~FCLK/2 | 0dBFS | 標準零階保持模式,適用于第一奈奎斯特區,頻率響應在高奈奎斯特區衰減明顯 |

| RTZ(歸零) | 是 | 0~FCLK | -6dBFS | 采樣周期后半段歸零,頻率響應展寬,支持第一、二奈奎斯特區,峰值功率降低 6dB |

| RF 模式 | 否 | FCLK/2~FCLK | -2.8dBFS | 采樣中期反轉信號,第二奈奎斯特區響應平坦,適用于射頻頻段直接輸出 |

| DES2XL(雙沿采樣低通) | 是 | 0~0.4FCLK | 0dBFS | 上升 / 下降沿均輸出采樣值,采樣率翻倍,內置低通 2x 插值濾波器,抑制低頻鏡像 |

| DES2XH(雙沿采樣高通) | 是 | 0.6~1.0FCLK | 0dBFS | 內置高通 2x 插值濾波器,抑制高頻鏡像,適用于高奈奎斯特區信號輸出 |

2. 數字上變頻(DUC)與 NCO

- DUC 配置 :4 個 DUC 可獨立或統一配置插值倍數(2x

256x),插值濾波器采用多級設計(如 fir1fir5、fir_3x), passband 帶寬 80%, stopband 衰減>90dB;支持通道綁定功能,可將多個 DUC 輸出按 1(0dB)、0.5(-6dB)、0.25(-12dB)增益縮放后求和,避免信號飽和。 - NCO 同步與重配置 :NCO 可通過 JESD204C 接口 LSB、SYSREF 信號或 SPI_SYNC 寄存器觸發同步,確保多通道 / 多器件相位一致性;快速重配置接口(FR)支持 60ns 內更新 32 位頻率字,且跳頻保持相位相干,適配動態頻率調整場景。

3. JESD204C 接口與同步

- 接口特性 :支持 2 條 SerDes 通道,速率最高 12.8Gbps,8b/10b 編碼可選加擾,64b/66b 編碼強制加擾;支持 subclass 0(非確定性延遲)與 subclass 1(確定性延遲),subclass 1 需通過 SYSREF 校準 LMFC/LEMC 計數器,確保多器件同步精度。

- 時序校準 :內置 SYSREF 窗口功能,可檢測 SYSREF 相對于 CLK 的位置(SYSREF_POS 寄存器),自動選擇最優采樣時刻(SYSREF_SEL 配置),補償溫度(-0.05ps/°C)與電壓(0.19ps/mV)導致的時序偏移,優化同步 margin;支持 LANE_ARR 寄存器測量 lane arrival 時間,輔助設置彈性緩沖區釋放延遲(RBD),確保 deterministic latency。

4. 特殊工作模式

- DDS 模式 :通過 DDS_EN 寄存器使能,禁用 JESD204C 接口與 DUC 插值濾波器,直接通過 NCO 生成 tones,支持 4 個獨立 DDS 通道;AMP 寄存器可配置各通道幅度,用于抵消 DAC 輸出諧波(如 HD2、HD3),提升信號動態范圍;此模式下 SYSREF 周期約束簡化,無需適配 JESD204C 時序要求。

- 睡眠與掉電模式 :支持睡眠模式(MODE [1:0]=0b11)與全掉電模式(MODE [1:0]=0b11),睡眠模式下寄存器配置保留,總功耗 171mW;全掉電模式需遵循特定電源時序,避免器件損傷,喚醒后需等待內部參考穩定(約 100μs)。

五、寄存器配置

1. 寄存器 bank 核心功能

- 全局控制 bank(0x0000~0x00FF) :包含芯片復位(SOFT_RESET)、設備配置(DEVICE_CONFIG)、SYSREF 控制(SYSREF_CTRL)、溫度傳感器控制(TS_SLEEP)等,用于器件基礎初始化與全局參數配置。

- JESD204C 配置 bank(0x0100~0x02FF) :配置 JESD 模式(JMODE)、通道數(JESD_M)、PLL 參數(REFDIV、MPY、RATE)、SerDes 均衡器(EQ_CTRL、LANE_EQ)、彈性緩沖區釋放延遲(RBD),確保高速接口穩定工作。

- DAC 與 DUC 配置 bank(0x02E0~0x03FF) :配置 DAC 輸出模式(MXMODE)、DUC 插值倍數(DUC_L)、NCO 頻率與相位(FREQ [n]、PHASE [n])、DEM/Dither 功能(DEM_DITH),控制信號生成鏈路參數。

- 狀態與告警 bank(0x0400~0x04FF) :包含溫度傳感器讀數(TS_TEMP)、系統告警(SYS_ALM)、同步狀態(SYNC_STATUS)、DAC 靜音控制(MUTE_MASK/MUTE_REC),用于監測器件工作狀態與故障排查。

2. 關鍵寄存器示例

| 寄存器地址 | 功能 | 關鍵配置示例 |

|---|---|---|

| 0x02E8(MXMODE) | DAC 輸出模式選擇 | MXMODE0=3(DACA 為 DES2XL 模式),MXMODE1=4(DACB 為 DES2XH 模式,僅 DDS39RF12) |

| 0x02E1(DUC_L) | DUC 插值倍數配置 | DUC_L=5(8x 插值),支持 4 個 DUC 同時工作 |

| 0x0320~0x0327(FREQ[0]) | NCO 頻率配置 | FREQ [0]=0x3D09000000000000(對應 120MHz,FCLK=12GHz) |

| 0x0300(NCO_CTRL) | NCO 與 DDS 模式控制 | DDS_EN=1(使能 DDS 模式),FR_EN=1(使能快速重配置接口) |

六、應用與設計建議

1. 典型應用場景

- 衛星通信(SATCOM) :利用 12GHz 寬輸出帶寬與低相位噪聲,生成 C/X 波段上行 / 下行信號,支持多載波同時輸出;DUC 插值功能可降低基帶數據率,適配 FPGA 數據處理能力。

- 合成孔徑雷達(SAR)激勵器 :通過 DDS 模式生成高線性度 Chirp 信號,NCO 相位相干跳頻確保雷達距離分辨率;DES2XL/H 模式抑制鏡像信號,減少后端濾波復雜度。

- 相控陣天線系統 :DDS39RF12 雙 DAC 支持雙極化信號輸出,多器件通過 SYSREF 同步,確保多通道相位一致性,提升天線波束成形精度。

2. 設計建議

- 電源設計 :模擬電源(VDDA18A/B、VEEAM18/B18)與數字電源(VDDDIG、VDDCLK10)需獨立供電,推薦 “開關電源 + 低噪聲 LDO” 架構(如 LMS3635+TPS7A8400),每路電源引腳就近并聯 0.1μF 陶瓷電容 + 10μF 鉭電容去耦;模擬地、數字地、時鐘地在熱焊盤處單點連接,避免地彈噪聲。

- PCB 布局 :

- 時鐘與同步 :采樣時鐘(CLK±)推薦使用低噪聲時鐘源(如 LMK04828),AC 耦合至引腳;多器件同步時,SYSREF 與 CLK 需等長布線(誤差<10ps),通過 SYSREF_POS 寄存器校準時序,確保同步精度。

- 信號完整性 :DAC 輸出端建議串聯 1kΩ 限流電阻(防止過流),驅動長距離信號時添加差分緩沖器(如 THS4551);JESD204C 鏈路使用阻抗匹配連接器(如 Samtec QSE 系列),減少信號反射。

-

dac

+關注

關注

44文章

2734瀏覽量

197340 -

分辨率

+關注

關注

2文章

1128瀏覽量

43382 -

DDS

+關注

關注

22文章

686瀏覽量

156760 -

數模轉換器

+關注

關注

14文章

1310瀏覽量

85863 -

數字合成器

+關注

關注

1文章

11瀏覽量

7673

發布評論請先 登錄

DDS,什么是DDS,DDS的結構

DDS是什么意思,DDS結構,DDS原理是什么

STM32的AD9854 DDS模塊調試總結

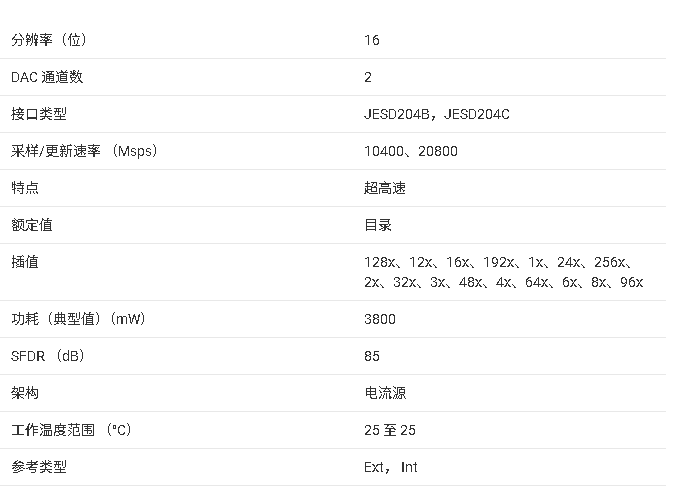

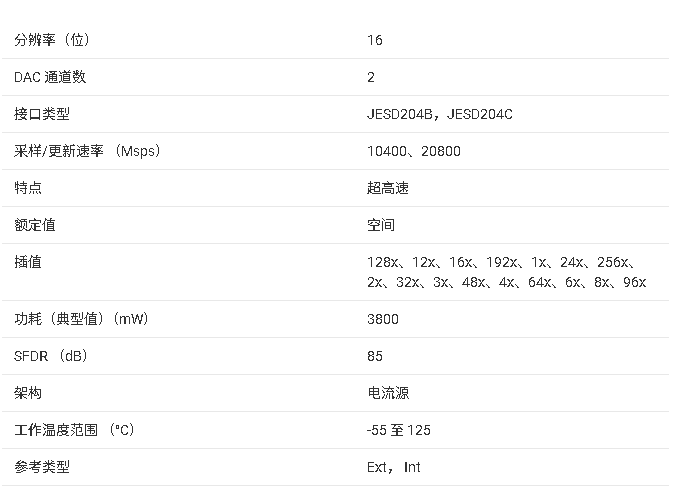

DAC39RF10、DAC39RFS10 10.24、20.48GSPS 16位雙通道和單通道多奈奎斯特數模轉換器(DAC)數據表

DAC39RF10EF DAC39RFS10EF雙通道和單通道數模轉換器(DAC)數據表

DAC39RF12、DAC39RFS12雙通道和單通道數模轉換器(DAC)數據表

DDS39RF10產品技術文檔總結

DDS39RFS10 產品技術文檔總結

DAC39RFx10-SP/SEP 系列數模轉換器技術文檔總結

DAC39RFx10 系列產品技術文檔總結

DAC39RFS10-SEP產品技術文檔總結

DAC39RF10技術文檔總結

DAC39RF10EF/DAC39RFS10EF 技術文檔總結

DDS39RF12 與 DDS39RFS12 產品技術文檔總結

DDS39RF12 與 DDS39RFS12 產品技術文檔總結

評論