設計背景:

First Input First Output的縮寫,先入先出隊列,這是一種傳統的按序執行方法,先進入的指令先完成并引退,跟著才執行第二條指令。FIFO是隊列機制中最簡單的,每個接口上都存在FIFO隊列,表面上看FIFO隊列并沒有提供什么QoS(Quality of Service,服務質量)保證,甚至很多人認為FIFO嚴格意義上不算做一種隊列技術,實則不然,FIFO是其它隊列的基礎,FIFO也會影響到衡量QoS的關鍵指標:報文的丟棄、延時、抖動。既然只有一個隊列,自然不需要考慮如何對報文進行復雜的流量分類,也不用考慮下一個報文怎么拿、拿多少的問題,而且因為按順序取報文,FIFO無需對報文重新排序。簡化了這些實現其實也就提高了對報文時延的保證。

設計原理:

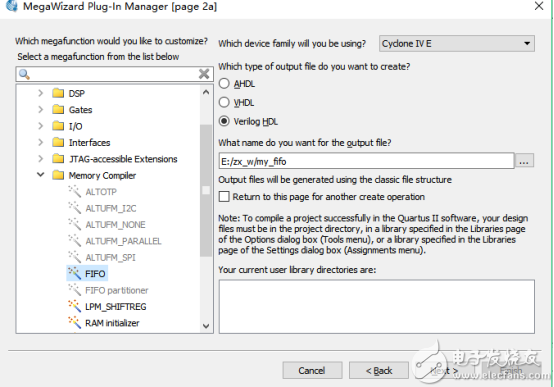

本次的設計主要通過調用FIFO的IP核來設置一個簡單的單口FIFO,也就是說讀寫時鐘為相同的時鐘。其設置流程如下所示也如rom,ram,設置一樣的打開步驟

如下如選擇FIFO,然后寫入生成的FIFO文件名,my_fifo,下一步

設置合適的數據位寬和深度,之后下一步

出現了空滿標志位,full,emty,我們去掉數據個數標志usedw.下一步

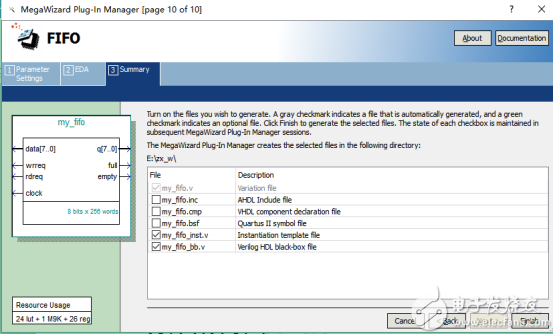

之后不停的下一步,出現下面的界面選擇生成的文件,然后就完成簡單的FIFO設計

設計架構圖:

設計代碼:

頂層模塊:

0moduletop (clk,rst_n,q);//輸入輸出端口

1 inputclk;

2 inputrst_n;

3 output[7:0]q;

4 wirewrreq; //寫使能信號

5 wirerdreq; //讀使能信號

6 wireempty; //空標志位

7 wirefull; //滿標志位

8 wire[7:0]data;

9

10fifo_control fifo_control (//FIFO控制器的例化

11 .clk(clk),

12 .rst_n(rst_n),

13 .full(full),

14 .empty(empty),

15 .wrreg(wrreq),

16 .rdreg(rdreq),

17 .data(data)

18 );

19my_fifo my_fifo ( //生成IP核的例化

20 .clock (clk ),

21 .data (data ),

22 .rdreq (rdreq ),

23 .wrreq (wrreq ),

24 .empty (empty ),

25 .full (full),

26 .q (q )

27 );

28

29endmodule

設計模塊

0modulefifo_control ( //端口列表

1 inputclk,

2 inputrst_n,

3 inputfull, //滿標志

4 inputempty, //空標志

5 outputregwrreg, //寫使能

6 outputregrdreg, //讀使能

7 outputreg[7:0]data

8 );

9 regstate;

10always@(posedgeclk ornegedgerst_n)

11 if(!rst_n)

12 begin

13 data<=0;

14 wrreg<=0; //寫使能關閉

15 rdreg<=0; //讀使能關閉

16 state <=0;

17 end

18 else

19 begin

20 case(state)

21 0:if(empty) //判斷是否為空,為空寫

22 begin

23 wrreg<=1;

24 data <=data +1;

25 end

26 elseif(full) //判斷否寫滿,為滿不寫

27 begin

28 state <=1;

29 wrreg<=0;

30 rdreg<=1;

31 data<=0;

32 end

33 else

34 begin

35 wrreg<=1;

36 data <=data +1;

37 end

38

39 1:begin

40 if(empty) //判斷是否讀空,讀空關閉讀使能

41 begin

42 rdreg<=0;

43 state <=0;

44 end

45 end

46 endcase

47 end

48

49endmodule

測試模塊

0`timescale1ns/1ps

1modulefifo_tb;

2

3 regclk;

4 regrst_n;

5 wire[7:0]q;

6initialbegin

7 clk =0;

8 rst_n =0;

9

10 #200rst_n=1;

11

12 end

13always#10clk=~clk;

14top top(

15 .clk(clk),

16 .rst_n(rst_n),

17 .q(q)

18 );

19

20endmodule

仿真圖:

從仿真空可以看到。我們寫入的數據是1--255--0,讀出的數據也是從1開始讀再到0。

這樣就完成了一個簡單的FIFO,如果要生成雙口的結局跨時鐘問題可以在設置時,下面頁面選擇

來進行設置

來進行設置

-

FPGA

+關注

關注

1662文章

22480瀏覽量

638501

發布評論請先 登錄

xilinx7系列FPGA新設計的IO專用FIFO解析

【FPGA干貨分享三】基于FPGA的LBS控制器設計

FPGA零基礎學習之Vivado-FIFO使用教程

基于Altera FPGA的彩屏控制器的設計和實現

基于FPGA的FIFO設計和應用

基于XILINX的XC3系列FPGA的VGA控制器的VHDL源程

Virtex-7 FPGA系列的內存控制器介紹

學習SDRAM控制器設計 能讓你掌握很多FPGA知識

Verilog數字系統設計——復雜數字電路設計2(FIFO控制器設計)

FPGA學習系列:24. FIFO控制器的設計

FPGA學習系列:24. FIFO控制器的設計

評論