關鍵要點

OTP非易失性存儲器在安全存儲數據、加密密鑰和程序代碼方面至關重要。

先進技術節點由于氧化層更薄、器件漏電流更高,對OTP的可靠性構成挑戰。

新思科技提供經過優化的OTP NVM IP,包含穩健的位單元設計與必要的模擬組件,可保障運行的可靠性。

一次性可編程(OTP)非易失性存儲器問世已久。與其他非易失性存儲技術相比,OTP的占用面積更小,且無需額外的制造工序,因此成為存儲啟動代碼、加密密鑰等內容的熱門選擇。盡管聽起來簡單,但隨著人工智能(AI)的大規模部署和對更先進技術的需求日益增長,平衡OTP的各項需求變得極具挑戰性。

這類器件在安全存儲數據、敏感程序代碼、產品信息和身份驗證加密密鑰方面發揮著關鍵作用,必須可靠運行才能保證芯片的成功量產,尤其是考慮到新技術成本的飆升,器件的可靠運行至關重要。然而,先進技術節點對于OTP存儲器的可靠運行帶來了諸多挑戰。為此,需要在多方面進行精細的平衡。值得慶幸的是,借助新思科技IP,我們能夠找到在先進技術節點中平衡OTP需求的解決方案。

有何風險?

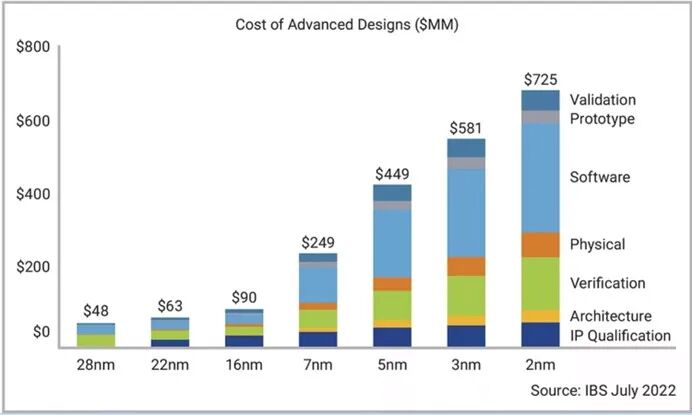

在先進的FinFET(鰭式場效應晶體管)技術節點中,設計、掩模和晶圓成本急劇攀升,使得一次性流片成功變得空前重要。而IP的可靠運行,尤其是OTP IP所支持的關鍵功能,正是通往成功的直接保障。下圖展示了先進技術的成本增長速度。

▲設計成本不斷攀升

OTP IP傳輸的數據很關鍵,能夠激活先進AI設計的各項功能。由于這類數據高度敏感,因此必須確保信息的準確傳輸,且絕不容許加密密鑰等信息出現泄露。在這些嚴苛要求之下,有諸多因素需要考量。我們來看看其中的一些因素。

成功路上的障礙

就從最基礎的知識說起。對于典型的反熔絲型OTP存儲器而言,未編程的單元代表邏輯值0,已編程的單元代表邏輯值1。這類器件在剛制造出來時,所有單元均處于未編程狀態,因此都為邏輯0。對單元進行編程時,需要向其施加高壓,高壓會導致氧化層擊穿,形成導電溝道或細絲,從而產生可測量的電流通路。

因此,讀取OTP需要測量柵極漏電流,以判斷存儲單元是已編程(邏輯1)還是未編程(邏輯0)。該過程需要使用高于核心供電電壓的穩定電壓,以便在位線上獲得足夠的電流,從而可靠地讀取數據。

到目前為止,這聽起來頗為簡單。但技術的進步使這一過程變得極具挑戰性。

先進技術節點的氧化層更薄,因此在高于核心供電電壓的穩壓下進行讀取時,OTP更容易出現位泄漏問題,甚至會將未編程的位誤讀為邏輯1。同時,氧化層變薄還會給正在讀取的字線中未編程的單元帶來更大的器件應力。

此外,先進技術節點的器件漏電流更高。這意味著需要使用更高的電壓才能驅動足夠的電流對OTP進行編程。而這些高電壓可能會導致器件損壞,進而造成編程失敗。并且,由于氧化層較薄,先進技術節點的OTP更易受高電壓影響,可能出現過度編程。OTP過度編程會導致編程質量不佳,還會使存儲單元不必要地過度暴露于高電壓。更糟糕的是,高電壓可能會引發編程干擾,即相鄰的非目標單元可能被意外編程,從而導致其他錯誤。

此外,還有一系列功耗、性能和面積(PPA)方面的挑戰需要應對。更高的漏電流會使OTP的面積競爭力難以維持,還可能限制可靠運行時的最大位容量。同時,編程時間也會影響整體制造成本。對OTP編程需要大幅提升電壓,而先進技術節點的供電電壓更低,因此可能需要更長時間才能將電壓提升至足以驅動編程電流的水平,以實現OTP的成功編程,這會導致時間和成本的增加。

平衡需求以實現成功的技巧

以下列出了一部分要求。

可靠的解決方案始于位單元的設計。編程時形成的細絲質量取決于氧化層的擊穿程度,而這又與位單元面積相關。如果面積過小,擊穿氧化層、形成細絲就會變得困難,進而導致編程失敗。如果面積過大,編程時氧化層可能會出現多處斷裂。

所有這些都可能導致關鍵數據讀取錯誤。因此,必須謹慎選擇位單元面積,以便優化編程時細絲的形成,避免錯誤發生,確保編程的可靠性。

OTP的讀取和編程均依賴高壓,這些電壓由模擬集成電源(IPS)產生和調節。IPS的設計對OTP的正常工作至關重要,電壓的波動會導致數據保持問題或錯誤。

此外,在讀取時,OTP輸出的數據必須始終可靠,確保所讀取的數據的完整性至關重要。用于標識OTP輸出“可用”的信號必不可少,這類信號能排除讀取過程中因電壓不穩定導致的非預期數據損壞。

再者,先進技術節點的器件漏電流較高,需要采取干預措施,不僅要保證OTP的可靠性,還要確保性能和功耗達到目標。需要精心設計位線長度和存儲陣列寬度,避免存儲器工作時出現過大的IR壓降。

最后,模擬設計的優化是關鍵。例如,感測放大器必須對先進技術節點特有的低電壓具有極高敏感性,以保證編程速度,編程速度會影響制造成本,需要通過高壓電路的專業設計進行優化。但由于要同時滿足以下兩個相互沖突的要求,實現起來頗具挑戰性:既要盡量減小OTP的整體面積,又要確保IPS中的電荷泵能提供足夠電流以成功完成存儲器編程。

新思科技提供解決方案

為滿足先進節點的需求,新思科技OTP NVM IP基于一個穩健且經過優化的反熔絲位單元。它已通過高溫工作壽命(HTOL)測試驗證,能夠平衡前文所述的各項需求。

此解決方案包含由平鋪位單元組成的存儲陣列、解碼器、模擬元件(如感測放大器),以及生成讀取和編程所需電壓的IPS。其選定的讀取電壓既能確保位單元讀取可靠,又能保證數據至少保存10年。

該IP通過增加額外的位來增強性能,以應對隨機制造缺陷和現場故障。在初始測試期間,每個字都能糾正漏電位和/或編程失敗錯誤。如果一個字內出現多個故障,可使用額外的修復資源,必要時可替換整個字。此外,OTP存儲陣列還包含用于存儲糾錯碼(ECC)的額外位。

該IP提供多種配置選項,可針對不同應用場景選擇合適方案。整體解決方案還包含一個控制器,負責管理讀寫操作、測試與修復功能以及ECC編碼和解碼過程。該控制器以RTL形式作為軟IP交付,OTP存儲陣列和IPS集成在單個硬宏中。

此外,該方案還具備強大的安全功能。

了解更多

關于新思科技在OTP存儲器優化實現方面的能力,剛才所說的不過是冰山一角。如今,幾乎所有設計都需要某種形式的OTP來確保正常運行。抽些時間了解新思科技如何助力開發者應對這種平衡挑戰,從而在先進技術節點上實現可靠運行,無疑是極具價值的。

有一篇內容詳實的文章《利用先進OTP IP打造安全可靠的SoC設計》可供參考。這些資料將提供所需信息,助力開發者理解如何借助新思科技的IP,在先進技術節點中平衡OTP的各項需求。

-

芯片

+關注

關注

463文章

54104瀏覽量

467308 -

存儲器

+關注

關注

39文章

7744瀏覽量

171901 -

新思科技

+關注

關注

5文章

965瀏覽量

52945

原文標題:芯片安全的核心:OTP在AI時代的關鍵作用

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

【案例5.1】存儲器選型的考慮要點

打通“神經”與“肌肉”:疆鴻智能EtherCAT轉DeviceNet在精密制造中的關鍵作用

ReRAM:AI時代的潛力存儲技術

VTI低功耗SRAM存儲器VTI508HB08

ISSI 64Mb同步動態隨機存取存儲器深度解析

解析液晶模塊的技術架構和關鍵作用

晶體晶振在機器人五大核心模塊的關鍵作用

信號發生器在5G通信測試中的關鍵作用與應用案例

簡單認識高帶寬存儲器

揭秘高效接地電阻柜的關鍵作用

辰達MOSFET在DC-DC變換器中的關鍵作用與優化策略

工業相機在焊縫跟蹤中的關鍵作用有哪些

OTP存儲器在AI時代的關鍵作用

OTP存儲器在AI時代的關鍵作用

評論