汽車芯片作為現(xiàn)代汽車電子系統(tǒng)的核心,涵蓋微控制器、功率半導(dǎo)體、傳感器、座艙芯片以及智能駕駛芯片等豐富品類。這些芯片相互協(xié)作,共同支撐著汽車的電動(dòng)化、智能化發(fā)展,同時(shí)也隨著這種發(fā)展被賦予更強(qiáng)大的處理能力。然而,要設(shè)計(jì)出這類大型、復(fù)雜且采用先進(jìn)工藝的汽車芯片并非易事,尤其面臨著高可靠性要求、超大規(guī)模電路驗(yàn)證,以及日益嚴(yán)苛的功能安全標(biāo)準(zhǔn)等多重挑戰(zhàn)。

汽車芯片的質(zhì)量、安全性、可靠性挑戰(zhàn)

質(zhì)量、安全性和可靠性一直是汽車芯片在設(shè)計(jì)時(shí)需要重點(diǎn)考慮的因素。汽車芯片需要滿足高質(zhì)量測(cè)試和零缺陷(即0 DPPM)要求,篩除生產(chǎn)制造過程中引入的各種缺陷。同時(shí),芯片在生命周期內(nèi)必須可靠運(yùn)行,避免器件本身和外部攻擊帶來的任何危害。

相比于消費(fèi)級(jí)芯片,車規(guī)級(jí)芯片驗(yàn)證周期較長,進(jìn)入Tier1或車廠需要通過諸如AEC-Q100這樣的嚴(yán)苛測(cè)試認(rèn)證。而認(rèn)證過程通常需要耗費(fèi)大量的時(shí)間和資源,這對(duì)芯片的設(shè)計(jì)周期和成本提出了挑戰(zhàn)。

與此同時(shí),隨著車用大規(guī)模集成電路的發(fā)展,在測(cè)試過程中碰到的故障類型越來越復(fù)雜,測(cè)試規(guī)模也不斷地加大,這些都導(dǎo)致了汽車芯片測(cè)試難度、測(cè)試時(shí)間、以及測(cè)試成本的增加。

西門子EDA的Tessent解決方案可以幫助汽車芯片設(shè)計(jì)者確保SoC達(dá)到高質(zhì)量,增強(qiáng)安全性、提高可靠性,從而更快地將產(chǎn)品推向市場(chǎng)。

Tessent DFT技術(shù)可以為汽車芯片提供高質(zhì)量測(cè)試以保證零缺陷。在傳統(tǒng)的故障模型之外,Tessent可以基于工藝和設(shè)計(jì)特征生成面向缺陷的故障模型,包括標(biāo)準(zhǔn)單元內(nèi)、標(biāo)準(zhǔn)單元間、互連開路、互連短路、時(shí)序感知和DFM感知等。用這些故障模型生成的ATPG pattern可以對(duì)制造缺陷達(dá)到更完整的測(cè)試覆蓋。

Tessent LogicBIST是業(yè)界知名的邏輯內(nèi)建自測(cè)試解決方案,可以復(fù)用掃描測(cè)試壓縮邏輯,在有限面積開銷條件下實(shí)現(xiàn)片內(nèi)掃描自測(cè)試能力,其專有的OST技術(shù)大大縮短測(cè)試時(shí)間、提高測(cè)試覆蓋率;Tessent MemoryBIST作為業(yè)界廣泛使用的存儲(chǔ)器測(cè)試生成工具,可以支持上下電和系統(tǒng)運(yùn)行中的測(cè)試和修復(fù),通過小范圍遞進(jìn)式方法在系統(tǒng)運(yùn)行過程中對(duì)內(nèi)存進(jìn)行非破壞性測(cè)試。此外,通過Tessent提供的參考流程和任務(wù)模式控制器,汽車芯片設(shè)計(jì)者能夠很容易地實(shí)現(xiàn)完整的功能安全島架構(gòu)。

超大規(guī)模電路的驗(yàn)證難題

在芯片流片前,確保其功能驗(yàn)證的準(zhǔn)確性至關(guān)重要。例如,必須驗(yàn)證DDR控制器能否正常執(zhí)行讀寫操作,以及PCIe是否能夠順利建立鏈路(Link up)并成功完成枚舉(Enumeration)。這些功能驗(yàn)證是芯片可靠性的基礎(chǔ)保障。

隨著芯片制程技術(shù)的不斷演進(jìn),以座艙、智駕芯片為代表的汽車芯片的集成度和復(fù)雜度日益提升,功能驗(yàn)證的難度和重要性也愈發(fā)凸顯。與此同時(shí),晶體管密度的大幅提高卻使芯片單位面積功耗不降反升,功耗控制面臨巨大挑戰(zhàn),如何將芯片功耗精準(zhǔn)控制在預(yù)算范圍,以及高效調(diào)度軟件任務(wù)實(shí)現(xiàn)功耗削峰填谷,也是一項(xiàng)棘手的任務(wù)。

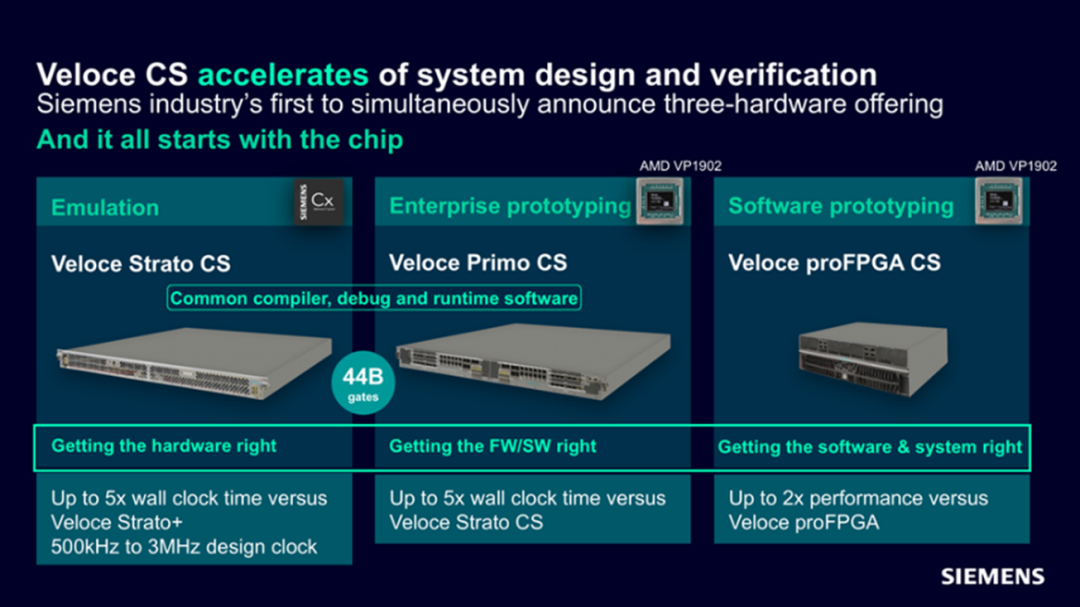

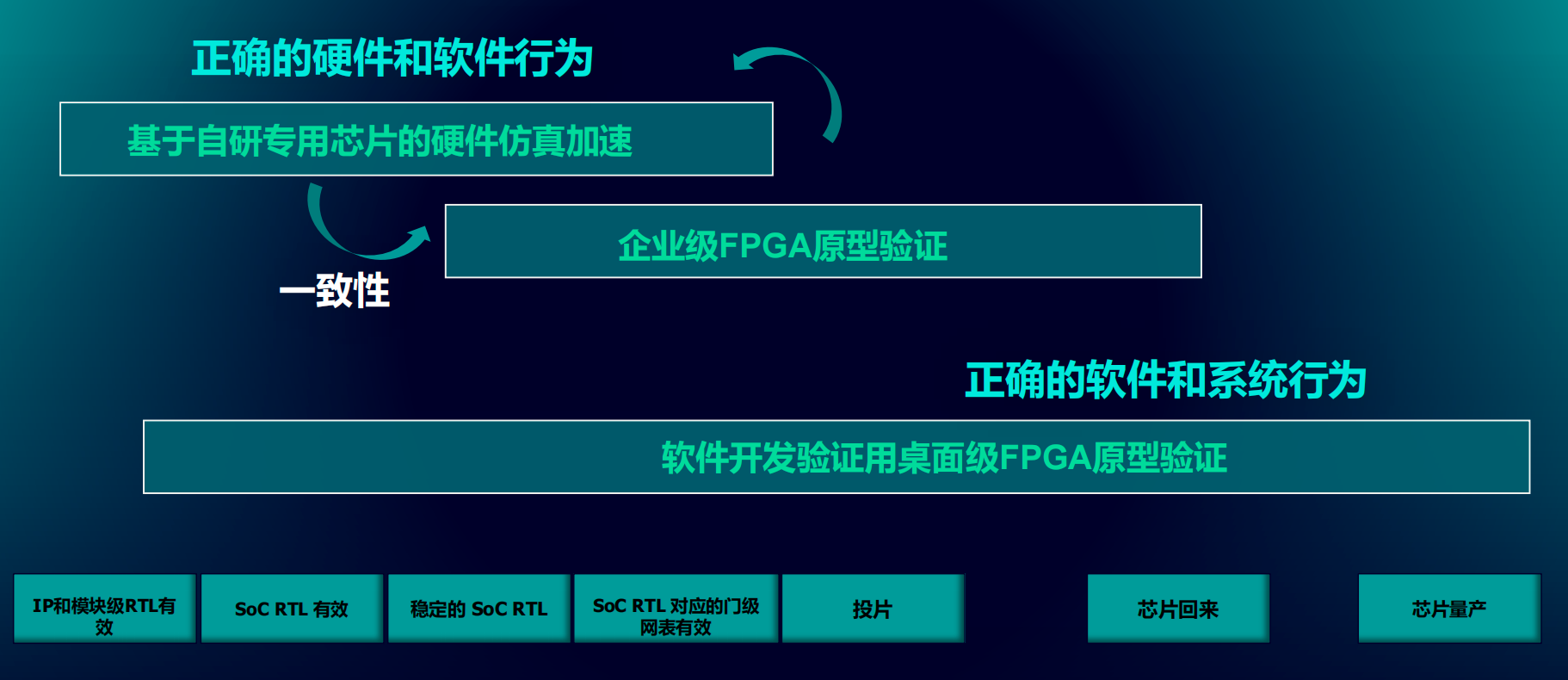

西門子EDA在2024年發(fā)布了全新一代的Veloce CS硬件輔助驗(yàn)證和確認(rèn)系統(tǒng),該系統(tǒng)融合了用于硬件加速仿真的Veloce Strato CS、用于企業(yè)原型驗(yàn)證的Veloce Primo CS和用于軟件原型驗(yàn)證Veloce proFPGA CS平臺(tái)。

與上一代Veloce Strato相比,Veloce Strato CS的硬件加速仿真性能顯著提高,同時(shí)還可保持完全的可觀測(cè)性,支持能力從4000萬門電路擴(kuò)展到超過400億門電路,有效滿足汽車芯片日益增長的容量和運(yùn)行速度需求。同時(shí),已有客戶通過Veloce Strato CS 上的Veloce Power APP,能夠在78分鐘內(nèi)完成整個(gè)500μs運(yùn)行時(shí)間的功耗變化包絡(luò)圖,大幅提升了系統(tǒng)功耗預(yù)估和優(yōu)化的效率, 相比傳統(tǒng)基于波形計(jì)算的方式提升了100倍。

Veloce Primo CS基于AMD先進(jìn)的Versal Premium VP1902 FPGA,提供企業(yè)原型驗(yàn)證系統(tǒng)的高度一致性,同樣可從4000萬門電路擴(kuò)展到超過400億門電路。而且,Veloce Strato CS和Veloce Primo CS可在相同的操作系統(tǒng)上運(yùn)行,并能在不同平臺(tái)之間無縫移動(dòng),顯著加快啟動(dòng)、設(shè)置、調(diào)試和工作負(fù)載執(zhí)行的速度。

此外,隨著“軟件定義汽車”(Software-Defined Vehicle)概念的興起,軟件的差異化已成為品牌價(jià)值的關(guān)鍵體現(xiàn)。所以需要盡可能左移軟件開發(fā)工作,運(yùn)行真實(shí)的負(fù)載,包括操作系統(tǒng)和應(yīng)用程序等,對(duì)系統(tǒng)的綜合性能進(jìn)行評(píng)估。

Veloce proFPGA CS能夠用于快速執(zhí)行集成電路和軟件的硅前驗(yàn)證,可從一個(gè)FPGA擴(kuò)展到數(shù)百個(gè)。這種性能加上高度靈活的模塊化設(shè)計(jì),可以幫助客戶顯著加快固件、操作系統(tǒng)和應(yīng)用程序的開發(fā)以及系統(tǒng)集成任務(wù)的執(zhí)行,為客戶提供驅(qū)動(dòng)開發(fā)和系統(tǒng)測(cè)試的高效平臺(tái)。

功能安全需求日益提升

從簡單的動(dòng)力控制到復(fù)雜的自動(dòng)駕駛決策,芯片的性能與安全性直接影響行車安全。涉及汽車安全功能的芯片必須嚴(yán)格遵守汽車行業(yè)的功能安全標(biāo)準(zhǔn),諸如ISO 26262等,以確保汽車電子電氣系統(tǒng)在運(yùn)行過程中不會(huì)因故障導(dǎo)致不合理的安全風(fēng)險(xiǎn)。

汽車芯片功能安全性要求正快速提升。過去,行業(yè)內(nèi)設(shè)計(jì)符合ASIL-B級(jí)別的IVI(車載信息娛樂系統(tǒng))、座艙等所用的車規(guī)芯片較為普遍。然而,自動(dòng)駕駛技術(shù)快速發(fā)展,對(duì)芯片功能安全性的要求越來越高。近年來,針對(duì)更高要求的ASIL-D級(jí)別設(shè)計(jì)的芯片逐漸增多,尤其是在和ADAS相關(guān)的芯片領(lǐng)域。

車規(guī)芯片設(shè)計(jì)流程中的安全分析與安全驗(yàn)證在各項(xiàng)安全相關(guān)的工作中占據(jù)了項(xiàng)目團(tuán)隊(duì)的主要精力,項(xiàng)目團(tuán)隊(duì)普遍希望能有更高效的方法論及工具,加速這兩項(xiàng)關(guān)鍵工作的進(jìn)程。

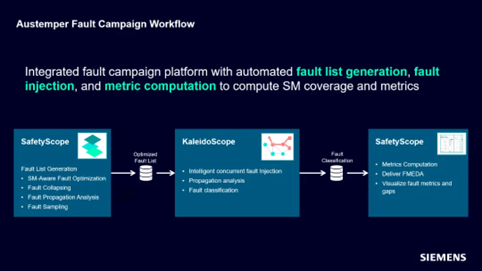

西門子EDA的Austemper功能安全平臺(tái),可以顯著提升用戶在芯片設(shè)計(jì)的安全分析與安全驗(yàn)證方面的效率,為完成項(xiàng)目贏得寶貴的時(shí)間。其卓越的安全分析工具SafetyScope,具有快速的安全機(jī)制探索功能。先進(jìn)的故障仿真工具KaleidoScope,具有分布式和并行處理機(jī)制,以及Stimulus Grading等功能,有效提升了故障仿真的效率。2025年5月,西門子EDA正式發(fā)布新一代Questa One Sim FX故障仿真平臺(tái),該產(chǎn)品由原KaleidoScope全面升級(jí)而來,在性能、效率和功能完整性方面實(shí)現(xiàn)顯著提升。

同時(shí),西門子EDA還擁有一支實(shí)力雄厚的功能安全FuSa Service服務(wù)團(tuán)隊(duì),匯聚眾多擁有十多年功能安全實(shí)踐經(jīng)驗(yàn)的資深專家,包含ISO 26262標(biāo)準(zhǔn)委員會(huì)的成員。FuSa Service服務(wù)從深入分析并分解車規(guī)芯片的安全需求,到提出針對(duì)性的安全機(jī)制建議,再到通過FMEA/FMEDA的迭代實(shí)施,以及執(zhí)行故障注入仿真以準(zhǔn)確獲取SPFM、LFM等關(guān)鍵指標(biāo),團(tuán)隊(duì)能夠全方位支持客戶,確保車規(guī)芯片滿足ASIL-B或D的嚴(yán)格要求。

目前,Austemper平臺(tái)和FuSa Service團(tuán)隊(duì)已贏得了客戶的廣泛贊譽(yù),成功助力多家國內(nèi)頂尖汽車芯片企業(yè)達(dá)成ASIL-B和ASIL-D車規(guī)芯片的安全目標(biāo),業(yè)務(wù)范圍廣泛覆蓋智能座艙、激光雷達(dá)、ADAS、高性能MCU等車規(guī)芯片的核心領(lǐng)域。

汽車芯片在現(xiàn)代汽車的智能化、電動(dòng)化進(jìn)程中扮演著不可或缺的角色。面對(duì)高可靠性要求、超大規(guī)模電路驗(yàn)證以及功能安全等多方面的挑戰(zhàn),西門子EDA憑借優(yōu)越的技術(shù)實(shí)力和創(chuàng)新能力為汽車芯片設(shè)計(jì)者帶來全面且精準(zhǔn)適配的先進(jìn)解決方案,助力企業(yè)確保汽車芯片的高質(zhì)量與高可靠性,加速產(chǎn)品上市,推動(dòng)行業(yè)快速平穩(wěn)地駛向發(fā)展快車道。

-

微控制器

+關(guān)注

關(guān)注

48文章

8416瀏覽量

164823 -

西門子

+關(guān)注

關(guān)注

98文章

3326瀏覽量

120472 -

eda

+關(guān)注

關(guān)注

72文章

3116瀏覽量

183203 -

汽車芯片

+關(guān)注

關(guān)注

10文章

1033瀏覽量

44973

原文標(biāo)題:克服汽車芯片設(shè)計(jì)面臨的三重挑戰(zhàn),快速平穩(wěn)地駛向未來!

文章出處:【微信號(hào):Mentor明導(dǎo),微信公眾號(hào):西門子EDA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

EDA三巨頭之一的Mentro被西門子收購 這個(gè)市場(chǎng)怎么了?

看EDA領(lǐng)域市場(chǎng)格局,西門子收購Mentor劍指何方

西門子收購Mentor會(huì)對(duì)EDA工具用戶帶來哪些改變?

加速創(chuàng)“芯” 西門子EDA技術(shù)峰會(huì)在滬舉辦

助推半導(dǎo)體創(chuàng)新需求,西門子EDA峰會(huì)揭秘AI工具鏈和創(chuàng)新平臺(tái)

基于自研芯片+頂級(jí)AMD FPGA,西門子EDA發(fā)布“快而全”的Veloce CS

西門子收購Solido強(qiáng)勢(shì)進(jìn)軍EDA領(lǐng)域

加速創(chuàng)“芯” 西門子EDA技術(shù)峰會(huì)在滬舉辦

nepes采用西門子EDA先進(jìn)設(shè)計(jì)流程,擴(kuò)展3D封裝能力

西門子EDA工具如何助力行業(yè)克服技術(shù)挑戰(zhàn)

西門子再收購EDA公司 西門子宣布收購Excellicon公司 時(shí)序約束工具開發(fā)商

新思科技(Synopsys)、西門子、楷登電子(Cadence)三大巨頭恢復(fù)對(duì)華EDA銷售

西門子EDA與北京開源芯片研究院達(dá)成戰(zhàn)略合作

西門子EDA如何應(yīng)對(duì)汽車芯片設(shè)計(jì)的三重挑戰(zhàn)

西門子EDA如何應(yīng)對(duì)汽車芯片設(shè)計(jì)的三重挑戰(zhàn)

評(píng)論