(3) 邊界測試結果

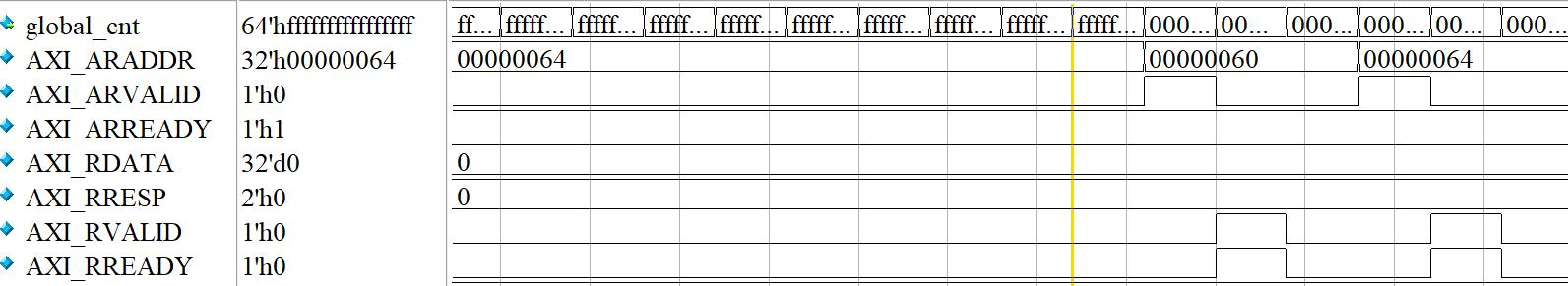

測試步驟 4 對應波形如圖 1所示, 寄存器最大值為 64’hFFFFFFFFFFFFFFFF,到達最大值后一個時鐘周期后翻轉回 0, 在隨機時刻使用 force 將寄存器賦值臨近最大值, 當寄存器達到最大值后, 翻轉回到 0, 讀取數(shù)值為 0, 仿真行為符合設計預期。

圖1 寄存器邊界測試仿真波形圖

(4) 功能測試結果

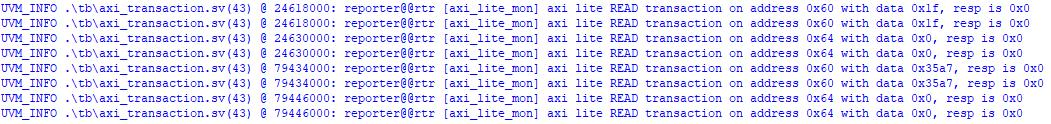

測試步驟 5 對應打印信息如圖 2 所示, 由于此步驟波形跨度較大因此使用打

印信息展示。 在 24618ns 時刻讀取寄存器值為 64’h1F, 在 79434ns 時刻讀取寄存器值

為 64’h35A7, 計算時間差值除以 4 等于寄存器兩次讀取差值, 仿真行為符合設計預

期, 測試通過。

圖2 寄存器功能測試打印信息圖

版權聲明:本文為博主原創(chuàng)文章,遵循 CC 4.0 BY-SA 版權協(xié)議,轉載請附上原文出處鏈接和本聲明。

原文鏈接:https://blog.csdn.net/tiantianuser/article/details/151548984

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內(nèi)容侵權或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

寄存器

+關注

關注

31文章

5615瀏覽量

130329 -

nvme

+關注

關注

0文章

300瀏覽量

23889

發(fā)布評論請先 登錄

相關推薦

熱點推薦

NVMe高速傳輸之擺脫XDMA設計42:DMA 讀寫功能驗證與分析

讀

寫功能的測試點與測試步驟如表 1 所示。

表 1 DMA 讀寫功能驗證步驟

1) DMA 讀功能

測試步驟 1 關鍵信號波形如圖1 所示, 首先配置 DMA

發(fā)表于 10-27 09:10

NVMe高速傳輸之擺脫XDMA設計37:隊列管理功能驗證與分析1

。 測試點與對應測試步驟如表 1所示。

表 1 隊列管理功能驗證步驟

(1) 創(chuàng)建隊列功能測試結果

測試步驟 1、 2 關鍵信號波形如圖1 所示。 在配置隊列控制

發(fā)表于 10-13 11:17

NVMe高速傳輸之擺脫XDMA設計35:初始化功能驗證與分析3

。 配置橋設備下游的 NVMe 設備模型波形如圖 1 所示。 待測設計首先獲取設備與供應商 ID, 然后獲取配置空間類型為 TYPE0, 再向 BAR0~5 寄存器分配地址, 由于只啟用了 64KB

發(fā)表于 10-10 18:21

NVMe高速傳輸之擺脫XDMA設計34:初始化功能驗證與分析2

模型, 配置過程波形如圖2所示, 圖中bus_no表示當前配置總線號, dev_no表示設備號, reg_no表示寄存器號, 也對應雙字對齊的寄存器地址。 待測設計首先讀取了配置空間 00h

發(fā)表于 10-09 11:31

NVMe高速傳輸之擺脫XDMA設計33:初始化功能驗證與分析

3, 表示 PCIe 初始化正常完成, 此時配置 init_ctrl 寄存器值為 2 啟動 NVMe 初始化,初始化狀態(tài)機跳轉到 NVMe 初始化狀態(tài), 初始化狀態(tài)

發(fā)表于 10-08 08:02

NVMe高速傳輸之擺脫XDMA設計32:寄存器功能驗證與分析2

臨近最大值, 當寄存器達到最大值后, 翻轉回到 0, 讀取數(shù)值為 0, 仿真行為符合設計預期.圖1 寄存器邊界測試仿真波形圖

(4) 功能測試結果測試步驟 5 對應打印信息如圖 2 所

發(fā)表于 10-02 11:47

NVMe高速傳輸之擺脫XDMA設計31: 寄存器功能驗證與分析1

寄存器的初始值、 讀寫操作測試、 邊界值測試、 功能測試等。(1) 初始值測試結果全局計數(shù)器寄存器(global_cnt) 測試步驟 1、 2

發(fā)表于 09-30 10:01

NVMe高速傳輸之擺脫XDMA設計30: NVMe 設備模型設計

設備則需要開啟至少 8KB 的 BAR0 空間, BAR0 地址空間中存放 NVMe 設備寄存器組, 其中包含了初始化過程中需要使用的控制器功能寄

發(fā)表于 09-29 09:31

NVMe高速傳輸之擺脫XDMA設計24: UVM 驗證包設計

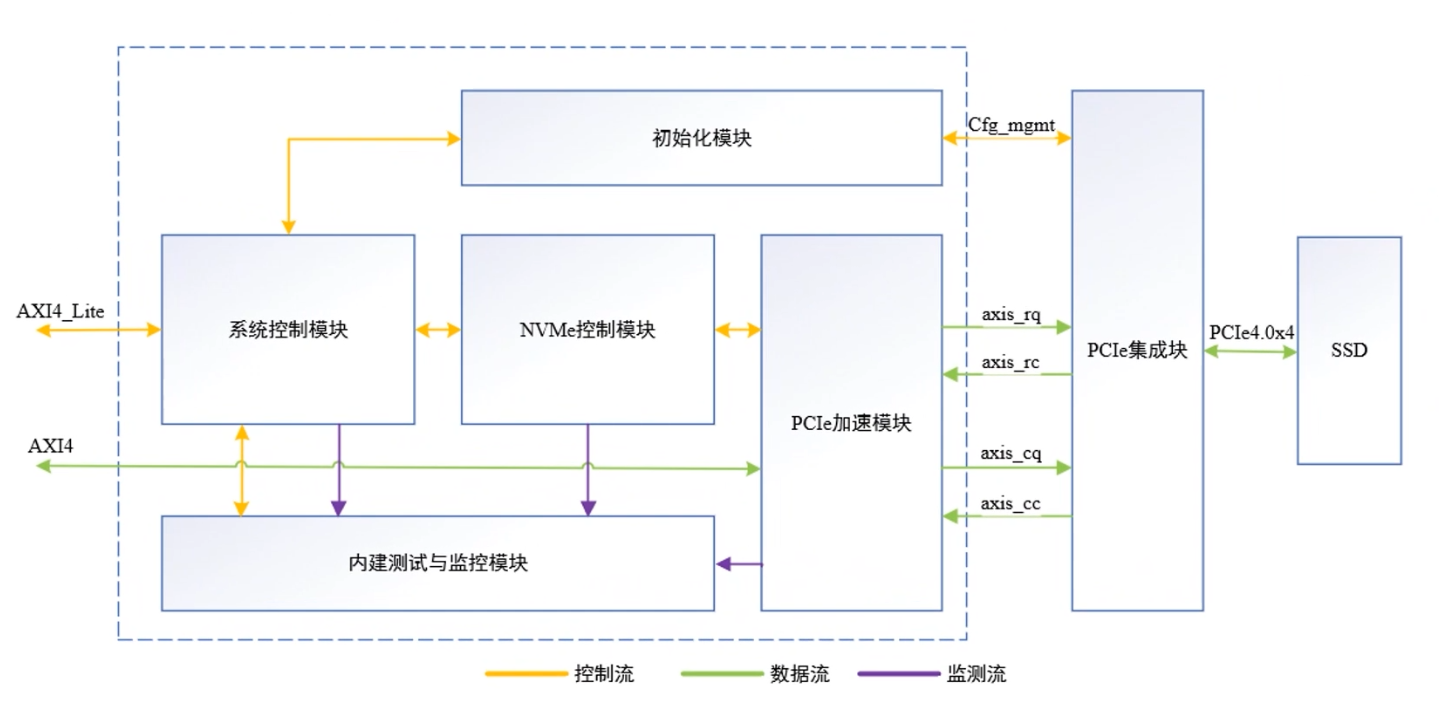

, 將監(jiān)測到的 PCIe TLP 事務發(fā)送到計分板。

NoPHAE_ref_model 是模擬 DUT 設計功能的參考模型, 該模型從 axi4_lite_agent的監(jiān)測器獲取寄存器配置信息, 根據(jù)

發(fā)表于 08-29 14:33

NVMe高速傳輸之擺脫XDMA設計23:UVM驗證平臺

抽象為 PCIeTLP 事務,因此為了方便的在事務層構建復雜的測試用例,項目基于 UVM 搭建驗證平臺進行功能驗證。圖1 驗證平臺架構圖在驗證

發(fā)表于 08-26 09:49

NVMe高速傳輸之擺脫XDMA設計18:UVM驗證平臺

抽象為 PCIeTLP 事務,因此為了方便的在事務層構建復雜的測試用例,項目基于 UVM 搭建驗證平臺進行功能驗證。圖1 驗證平臺架構圖在驗證

發(fā)表于 07-31 16:39

NVMe IP高速傳輸卻不依賴XDMA設計之八:系統(tǒng)初始化

采用XDMA是許多人常用xilinx庫實現(xiàn)NVMe或其他傳輸的方法。但是,XDMA介紹較少,在高速存儲設計時,尤其是PCIe4.0模式下,較

NVMe高速傳輸之擺脫XDMA設計之十:NVMe初始化狀態(tài)機設計

DISABLE_CC狀態(tài)。

RD_CAP:讀控制器功能寄存器狀態(tài)。該狀態(tài)下讀取NVMe設備的控制器功能

發(fā)表于 07-05 22:03

NVMe IP over PCIe 4.0:擺脫XDMA,實現(xiàn)超高速!

基于NVMe加速引擎,它直接放棄XDMA,改為深度結合PCIe,通過高速傳輸機制開發(fā)。同時利用UVM驗證平臺

NVMe高速傳輸之擺脫XDMA設計32:寄存器功能驗證與分析2

NVMe高速傳輸之擺脫XDMA設計32:寄存器功能驗證與分析2

評論