代碼解析

LTC2308通過一個(gè)標(biāo)準(zhǔn)4線SPI數(shù)字接口進(jìn)行通信。LTC2308模數(shù)轉(zhuǎn)換芯片有8個(gè)ADC通道和12位的分辨率,輸入信號(hào)時(shí)鐘頻率范圍不超過500KHz,按照Nyquist采樣定理則建議輸入信號(hào)在250KHz以下。

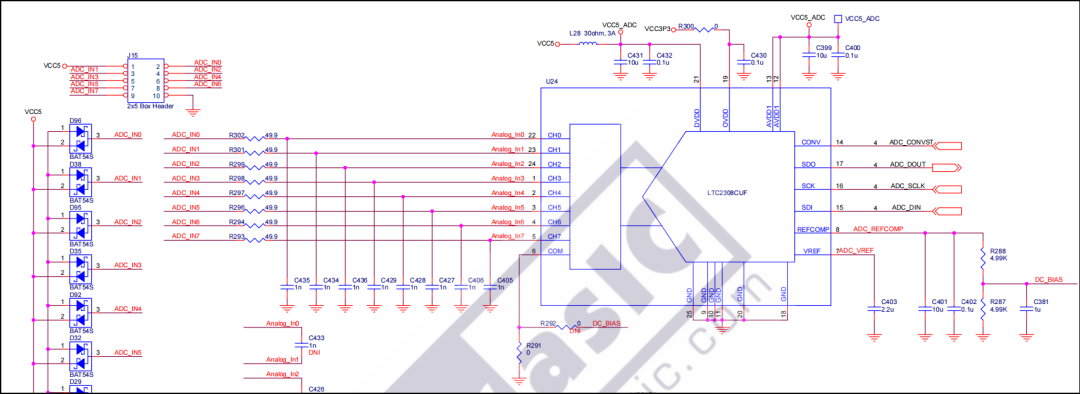

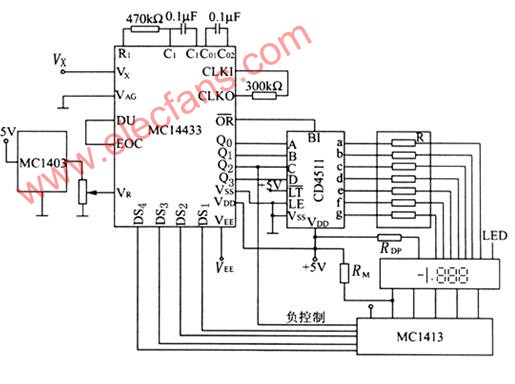

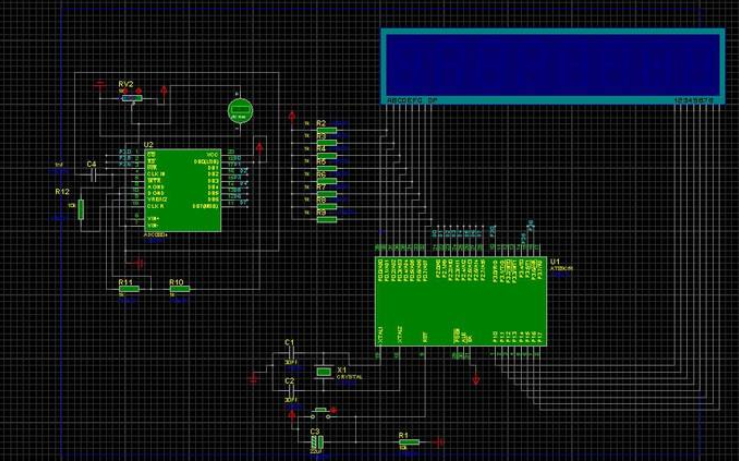

以下是DE10-Standard開發(fā)板上的LTC2308電路:

從電路圖可知,LTC2308的COM引腳接GND,代表當(dāng)前DE10-Standard開發(fā)板上的LTC2308被固定為單極性輸入。

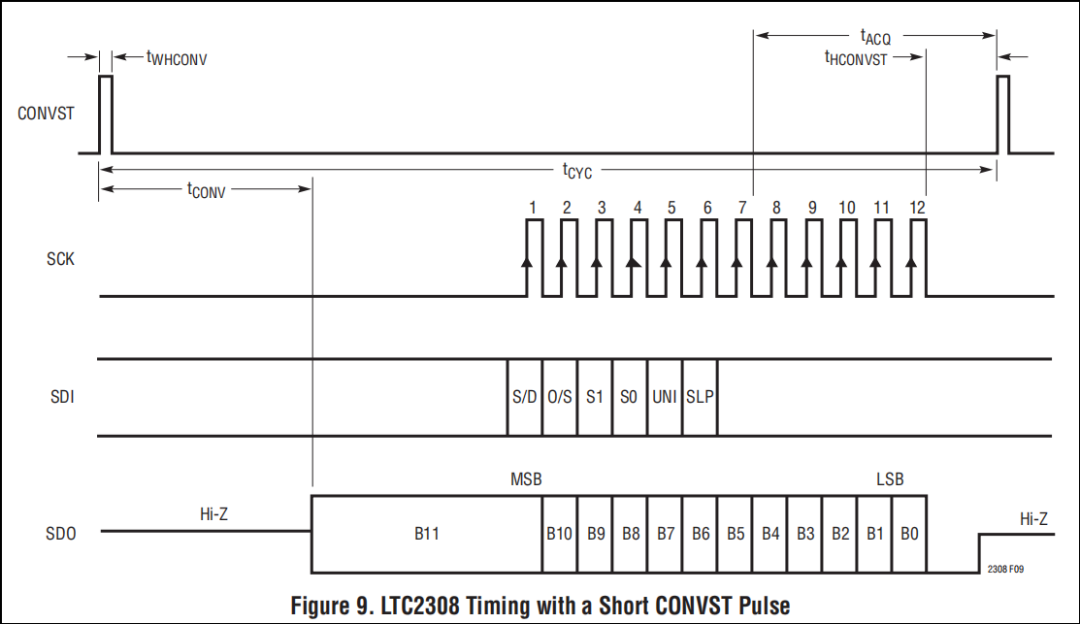

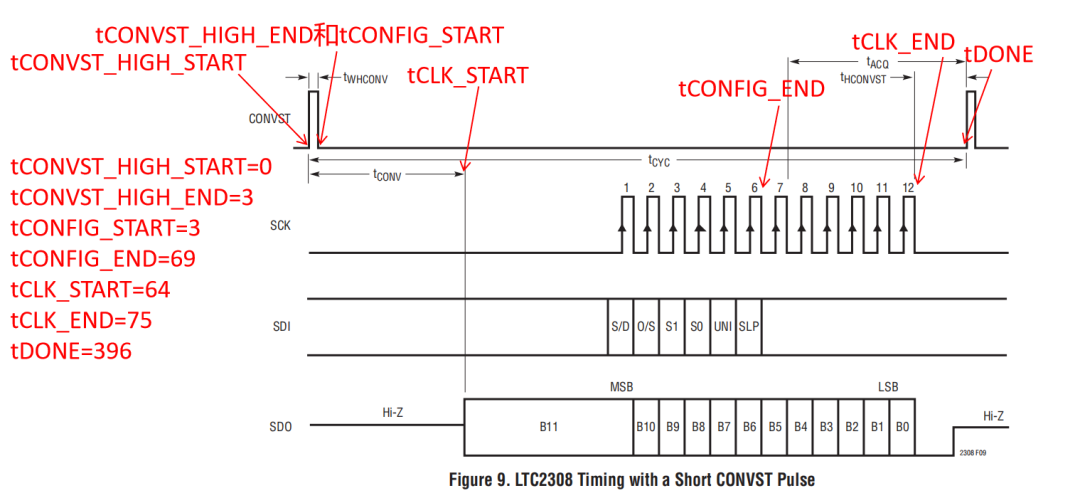

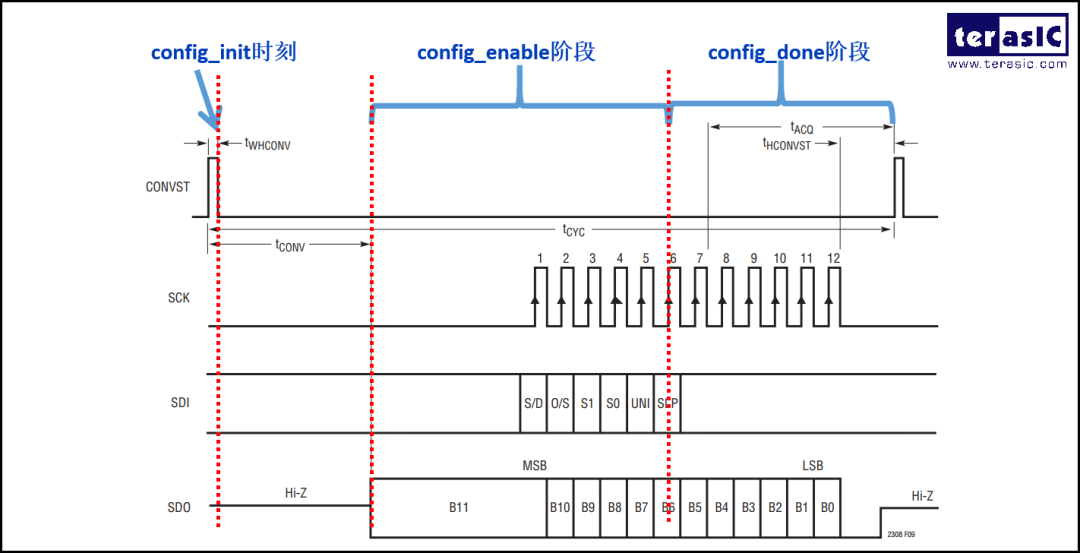

LTC2308的SPI協(xié)議時(shí)序圖如下:

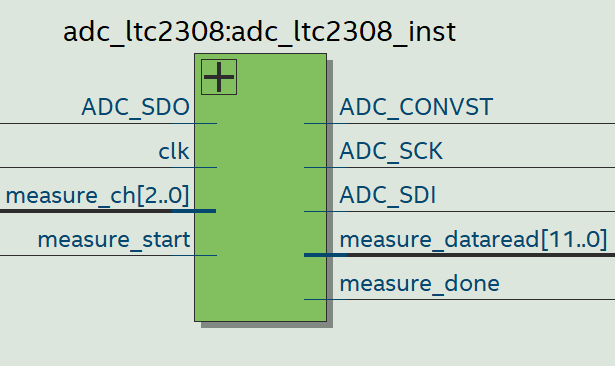

LTC2308控制模塊(adc_ltc2308.v)框圖如下:

信號(hào)列表如下:

模塊參數(shù)設(shè)計(jì):

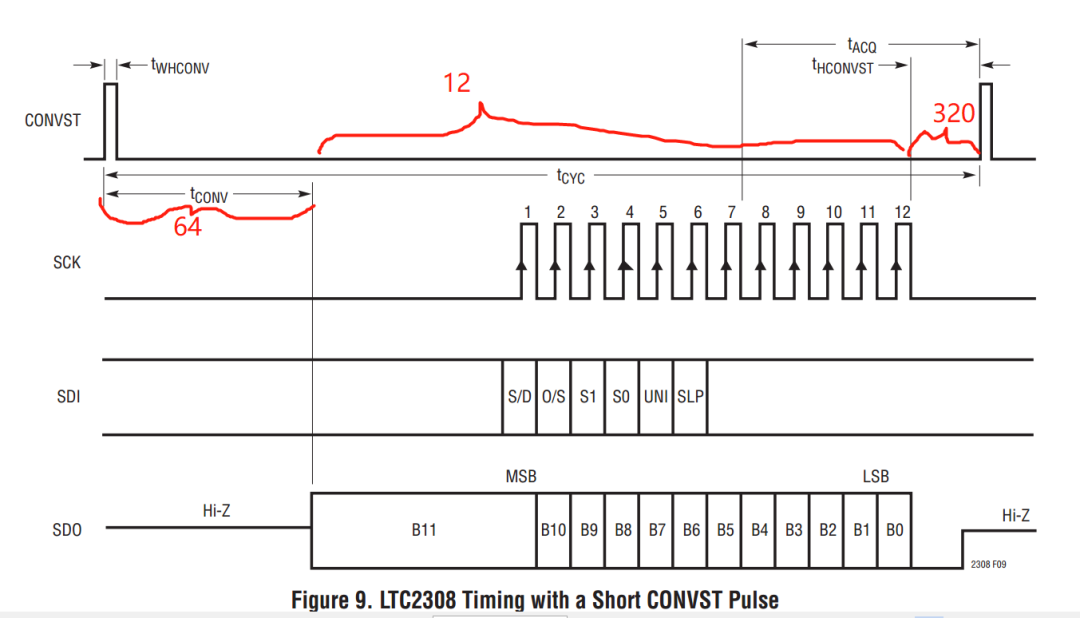

DE10-Standard開發(fā)板手冊(cè)(DE10-Standard_User_manual.pdf)提到如果想設(shè)置采樣率100Ksps,只需設(shè)置tHCONVST 為 320即可。接下來看看320這個(gè)數(shù)值是如何計(jì)算出來的。

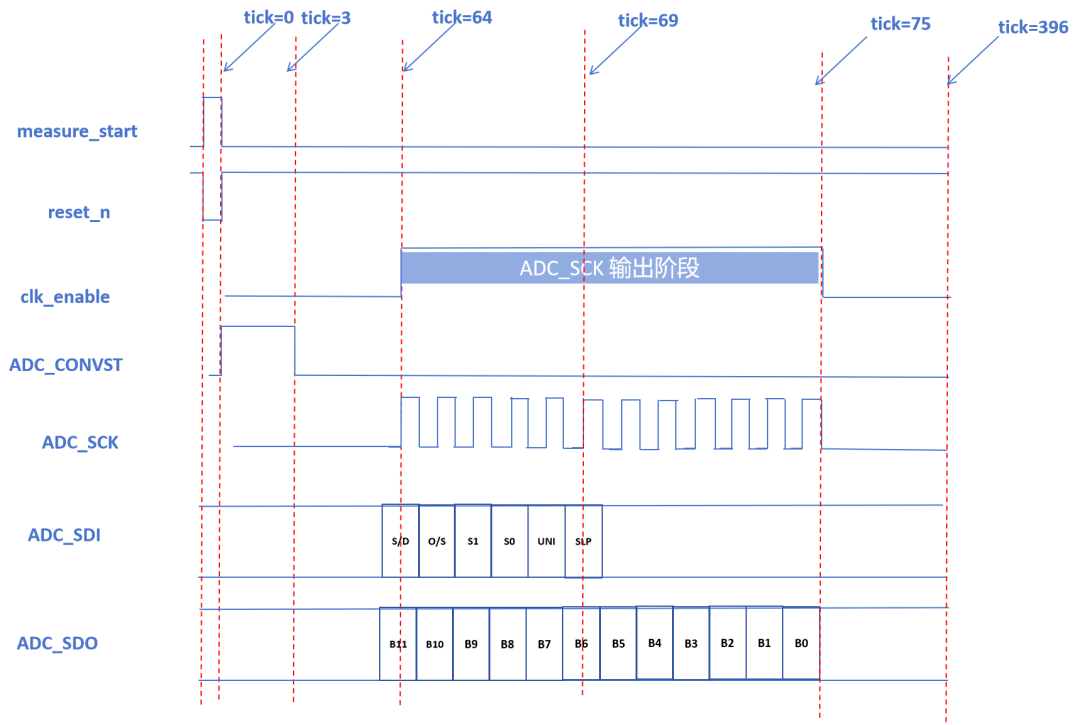

根據(jù)LTC2308數(shù)據(jù)手冊(cè)我們知道其最高采樣率是500ksps, SCK最高能達(dá)到40MHz, tCONV 的典型值是1.3 us,最大值是 1.6 us。100Ksps的時(shí)間周期是10us,40MHz的時(shí)間周期是25ns。一次整個(gè)過程(包括轉(zhuǎn)換和采樣)要占用10us/25ns=400 個(gè)周期。1.6us/25ns= 64, 那么tCONV 最多占用64個(gè)時(shí)鐘周期。

根據(jù)時(shí)序圖和代碼來看,64+12+320=396大約是400 。

adc_ltc2308.v代碼里面參數(shù)設(shè)定如下:

代碼詳解:

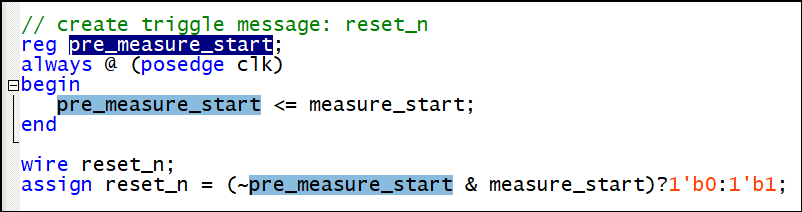

一旦檢測(cè)到觸發(fā)信號(hào)measure_start的上升沿,adc_ltc2308 模塊的系統(tǒng)復(fù)位信號(hào)就置0:

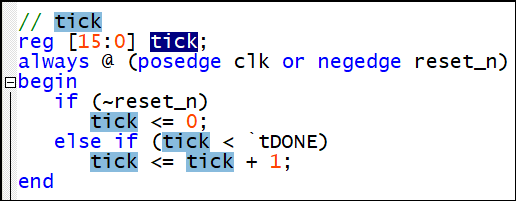

設(shè)計(jì)一個(gè)計(jì)數(shù)器,對(duì)LTC2308的一次完整轉(zhuǎn)換和采集過程所需的時(shí)鐘周期數(shù)進(jìn)行數(shù)節(jié)拍:

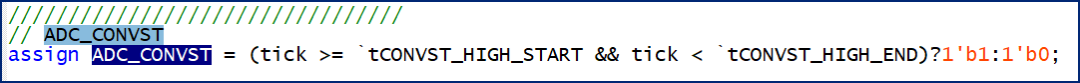

輸出ADC_CONVST信號(hào)(也就是標(biāo)記出tWHCONV時(shí)間段):

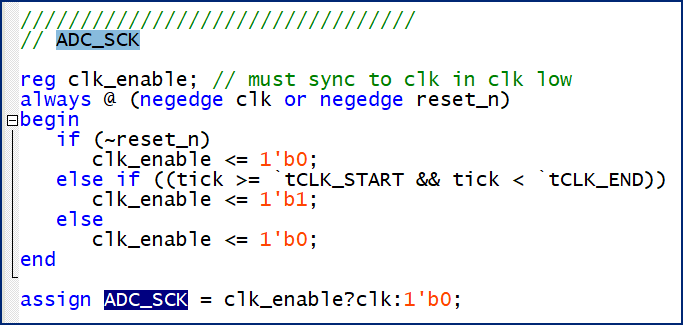

輸出SCK時(shí)鐘,ADC_SCK周期為40MHz,但每一次只有12個(gè)周期輸出,其他時(shí)間輸出低電平0 :

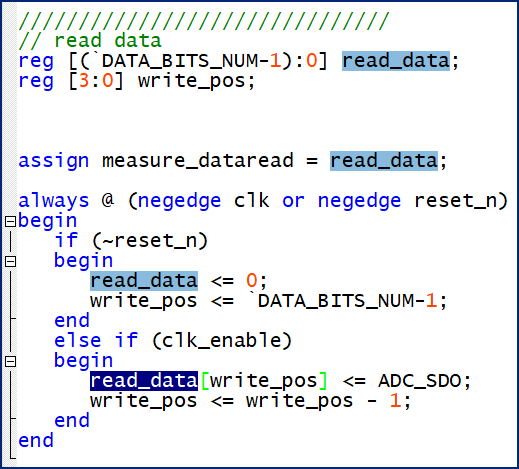

在clk下降沿時(shí)刻,將轉(zhuǎn)換完成的數(shù)據(jù)寫入到到寄存器中:

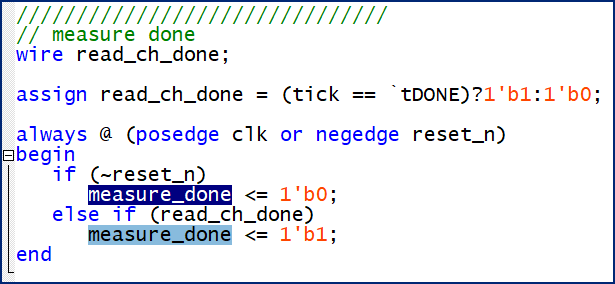

measure_done是一次采集完成標(biāo)志,每次檢測(cè)到LTC2308的觸發(fā)信號(hào)上升沿時(shí)measure_done信號(hào)歸0,當(dāng)一次采集完成后置1:

measure_done是一次轉(zhuǎn)換+傳輸+采樣完成的標(biāo)志,measure_done信號(hào)在開始新一輪采樣后清0,當(dāng)傳輸完成后置1:

reset_n、clk_enable、measure_done、ADC_CONVST和ADC_SCK信號(hào)波形標(biāo)出如下:

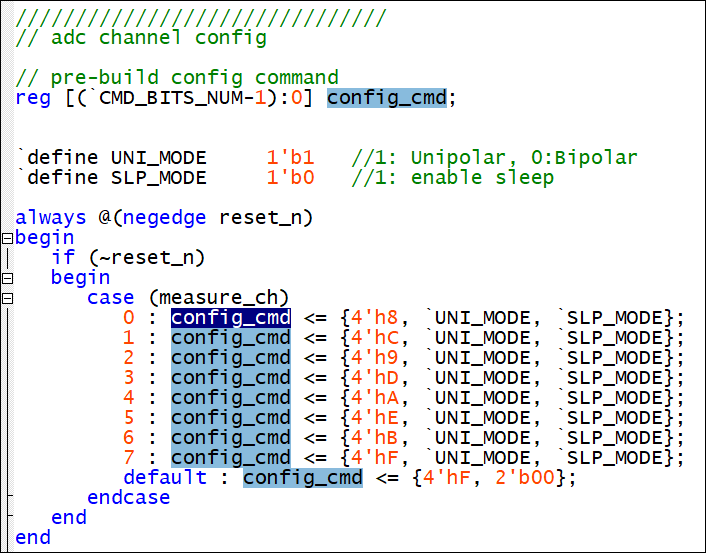

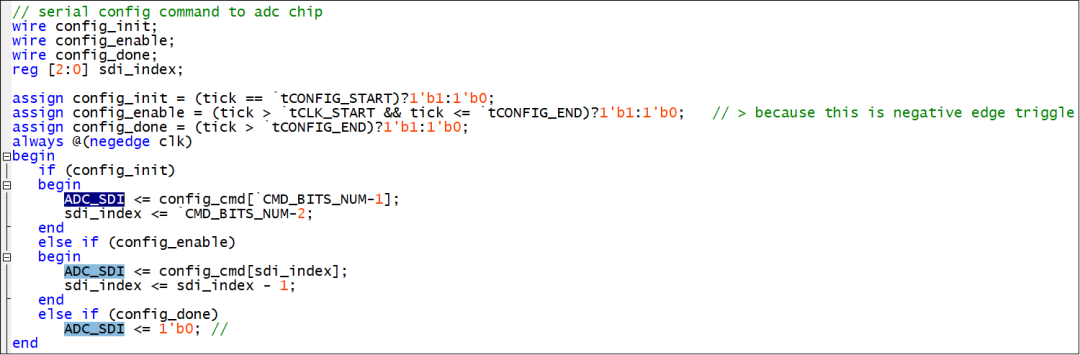

根據(jù)輸入(measure_ch)的通道選擇不同的配置字存儲(chǔ)到寄存器config_cmd:

然后根據(jù)LTC2308的時(shí)序圖標(biāo)記出配置字的三個(gè)階段(三個(gè)狀態(tài)):config_init(配置初始化時(shí)間段) 、config_enable(可配置時(shí)間段) 和 config_done(配置完成時(shí)間段)。

config_init(配置初始化時(shí)間段):初始狀態(tài)下,將配置字的高字節(jié)賦給ADC_SDI

config_enable(可配置時(shí)間段):將配置字剩余的5個(gè)bit逐個(gè)賦給ADC_SDI

config_done(配置完成時(shí)間段):配置完成階段將0賦給ADC_SDI

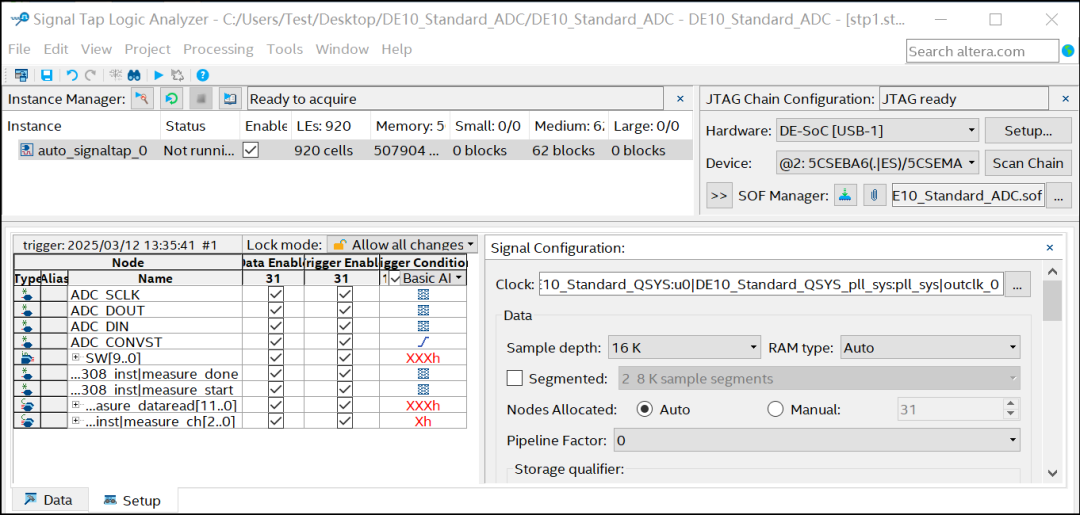

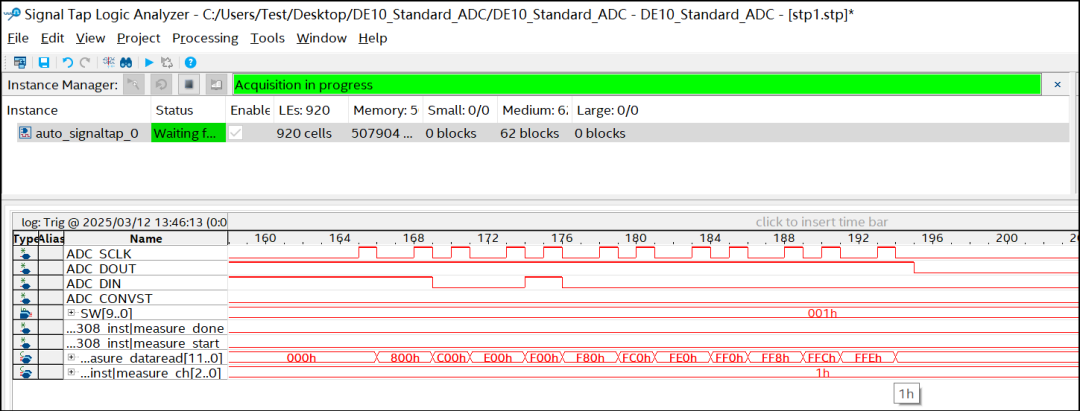

打開~DE10_Standard_ADCstp1.stp 文件(關(guān)于Signaltap調(diào)試工具的使用請(qǐng)參考之前的推文:SDRAM讀寫),采樣時(shí)鐘設(shè)置的是PLL outclk_0輸出的100M,ADC_CONVST作為觸發(fā)信號(hào):

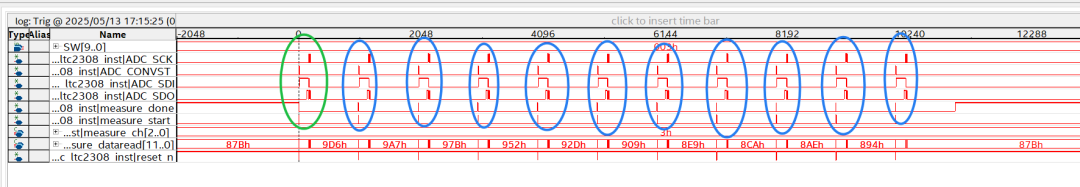

可得到 LTC2308控制模塊(adc_ltc2308.v)內(nèi)部信號(hào)的波形如下。

測(cè)量11次,第一次的數(shù)據(jù)忽略, 取后面10次的數(shù)據(jù):

ADC_CLK 輸出12個(gè)時(shí)鐘周期:

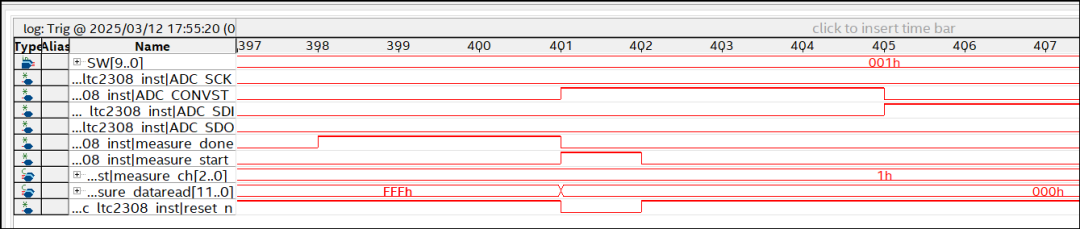

若 stp1.stp 文件采樣時(shí)鐘設(shè)置為PLL outclk_1輸出的40M,則波形細(xì)節(jié)如下:

ADC_CONVST占用4個(gè)時(shí)鐘周期(tick=0、1、2、3):

-

FPGA

+關(guān)注

關(guān)注

1662文章

22450瀏覽量

637712 -

接口

+關(guān)注

關(guān)注

33文章

9553瀏覽量

157339 -

adc

+關(guān)注

關(guān)注

100文章

7565瀏覽量

556490 -

引腳

+關(guān)注

關(guān)注

16文章

2112瀏覽量

55858 -

SPI協(xié)議

+關(guān)注

關(guān)注

0文章

24瀏覽量

8848

原文標(biāo)題:05-基于FPGA和LTC2308的數(shù)字電壓表設(shè)計(jì)-用FPGA實(shí)現(xiàn)SPI協(xié)議通訊

文章出處:【微信號(hào):友晶FPGA,微信公眾號(hào):友晶FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

基于FPGA和LTC2308模數(shù)轉(zhuǎn)換芯片的數(shù)字電壓表設(shè)計(jì)

源碼系列:基于FPGA的數(shù)字電壓表(AD)設(shè)計(jì)

版主 你好,我在論壇查到FPGA的數(shù)字電壓表的設(shè)計(jì)已經(jīng)過期了。

請(qǐng)問如何利用CPLD實(shí)現(xiàn)智能數(shù)字電壓表的設(shè)計(jì)?

怎么利用FPGA實(shí)現(xiàn)數(shù)字電壓表的設(shè)計(jì)

數(shù)字電壓表的VHDL設(shè)計(jì)與實(shí)現(xiàn)

數(shù)字電壓表的設(shè)計(jì)

電壓表protues仿真 基于51數(shù)字電壓表仿真設(shè)計(jì) 電壓表程序

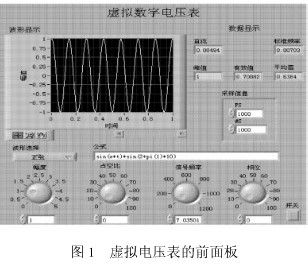

基于LabVIEW8.2的虛擬數(shù)字電壓表的設(shè)計(jì)和實(shí)現(xiàn)

FPGA數(shù)字電壓表的程序資料免費(fèi)下載

如何使用FPGA實(shí)現(xiàn)數(shù)字電壓表的設(shè)計(jì)

基于FPGA的SPI協(xié)議及設(shè)計(jì)實(shí)現(xiàn)

數(shù)字電壓表設(shè)計(jì)教程之使用FPGA實(shí)現(xiàn)SPI協(xié)議通訊

數(shù)字電壓表設(shè)計(jì)教程之使用FPGA實(shí)現(xiàn)SPI協(xié)議通訊

評(píng)論