時鐘門控效率是低功耗設計早期階段極具價值的可量化指標,使用英諾達的EDA工具進行功耗優化并獲取RTL修改建議,讓功耗優化不再是“玄學”。

對芯片工程師來說,在RTL階段進行功耗估算是一項艱巨的工作,如同盲人摸象一般,只能基于有限的信息和不完整的模型去感知功耗的“全貌”,而功耗優化就更難了,面對龐大的設計,應該從何下手?如何才能找到一個清晰、可量化的指標呢?

本文將介紹在低功耗設計早期階段極具價值的可量化指標——時鐘門控效率(Clock Gating Efficiency)。它不僅是評估RTL代碼質量的關鍵指標,更是指導工程師進行功耗優化的重要方法。

時鐘門控效率:早期功耗優化的可靠抓手

在芯片設計的RTL階段,許多功耗相關的指標(如線網電容等)都難以精確量化。然而,時鐘門控效率卻是一個可量化、可追蹤、且與最終功耗高度相關的少數指標之一。

芯片中連接觸發器的時鐘網絡會持續翻轉,產生大量動態功耗。時鐘門控技術在時鐘路徑上添加一個“開關”(時鐘門控單元)。當觸發器的數據輸入端沒有變化時,這個開關會切斷時鐘信號,阻止其無謂翻轉。而時鐘網絡是功耗大戶,因此這也是降低功耗最有效的手段之一。

在修改RTL代碼或使用優化工具后,只要時鐘門控效率得到提升,那么最終測得的動態功耗值幾乎必然呈現下降趨勢,為工程師提供了一條明確的優化路徑。

三大核心指標:直觀、簡單、高效

業內雖然存在多種評估方法,但以下三個指標因其直觀、簡單、有效而被廣泛采用:

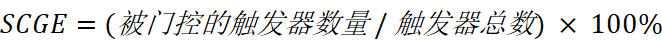

1.靜態時鐘門控效率(Static Clock Gating Efficiency, SCGE)

該指標計算了設計中觸發器被門控的比例,當觸發器被門控的比例越高,設計中時鐘翻轉浪費的功耗越少,因此該指標越高越好。同時,此數據不依賴于波形或信號活動率,能夠很好地反映RTL設計中觸發器的門控情況。

2.動態時鐘門控效率(Dynamic Clock Gating Efficiency, DCGE)

該指標計算了時鐘信號被門控的周期個數占比,當被門控的時鐘周期越多,那么無效的翻轉就越少,從而達到節約功耗值的目的。DCGE越高,說明在當前工作場景下,時鐘門控的收益越大。

3.數據感知時鐘門控效率(Data-aware Clock Gating Efficiency, DACGE)

數據感知時鐘門控效率在動態時鐘門控效率的基礎上,考慮了觸發器D引腳的翻轉周期,從而更綜合的考慮了觸發器輸入的影響。

這三個指標并非全部,但它們是最直觀、簡單、有效的優化手段。每一個被門控的觸發器都有各自的DCGE和DACGE,同時整個設計也有平均的SCGE、DCGE和DACGE,以供設計者更好了解每一個觸發器的門控效率。DCGE和DACGE依賴于信號活動率,在不同的信號活動率具有不同的門控效率。

如何優化三大指標?

理解了指標,下一步是如何提升它們。這需要區分兩種不同的工具流程:

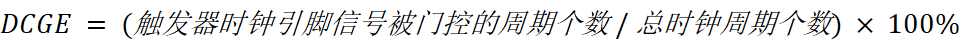

1.邏輯綜合

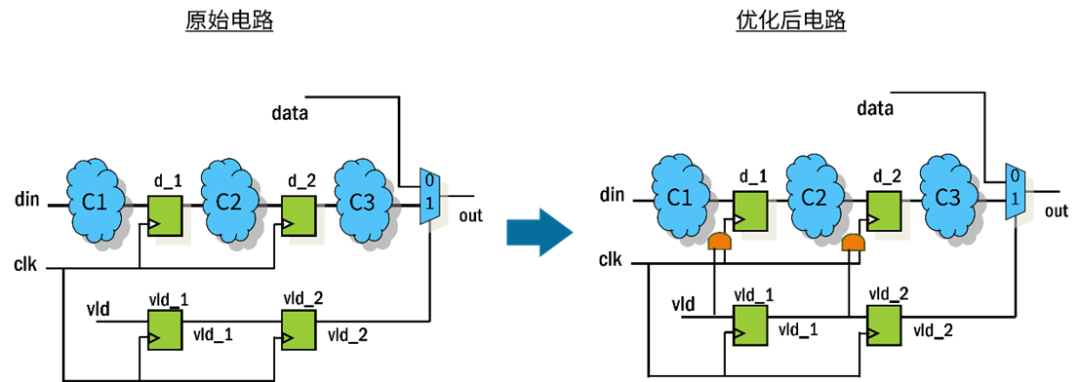

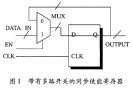

EDA綜合工具一般可以完成基礎優化,其目的是為保證優化后的電路與原始設計在邏輯上等價(LEC),在綜合階段通過解開電路中帶MUX的邏輯環路,并插入門控時鐘單元而達到門控的目標。

2.進階優化

專門的功耗優化工具可以處理綜合工具不會察覺的功耗優化機會。如上圖,專門的功耗優化工具通過分析電路拓撲結構,識別出當數據路徑被多路選擇(MUX)信號旁路時,該路徑上的信號翻轉是無效的,會造成功耗浪費。工具利用MUX的控制信號狀態,判斷并生成門控邏輯,以關閉相關路徑上觸發器的時鐘信號,從而發現傳統綜合工具無法捕捉的門控機會,進一步提升時鐘門控效率,實現更深層次的功耗優化。

當然,這只是眾多優化方式中的一種,電路中還存在著其他豐富的優化機會等待探索。

從分析到優化: 英諾達ERPA與ERPE的協同作戰

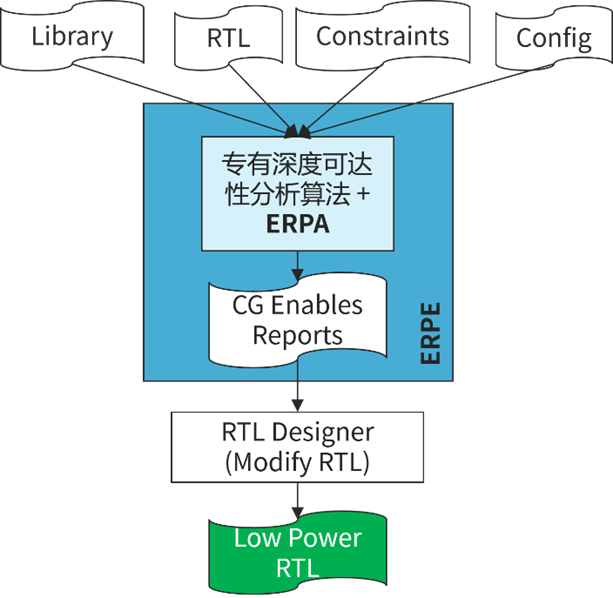

時鐘門控效率不是一個新概念,但它在設計早期階段的指導價值常常被低估。通過英諾達的ERPA(RTL級功耗分析工具)和ERPE(低功耗設計優化工具),工程師可以將這一優化流程融入到設計里:

英諾達ERPA與ERPE在RTL階段的功耗探索流程

功耗診斷

英諾達的ERPA是用于早期功耗水平評估的EDA工具,通過自研的綜合引擎,在讀入RTL代碼后,會自動處理時鐘門控電路插入流程,提高時鐘門控效率的各個指標,工程師可以查看每個觸發器以及整個設計層面的指標結果,從而分析RTL代碼中可以優化的點。

功耗調優

ERPE工具是功耗優化的引擎,通過更復雜的邏輯去探索電路結構,從而找到綜合工具無法發現的,更深層次的門控機會。這款工具不僅可以列出所有門控的觸發器信息,更會提供RTL代碼修改建議,預測修改后的時鐘門控效率變化,以及預測功耗的節約值。

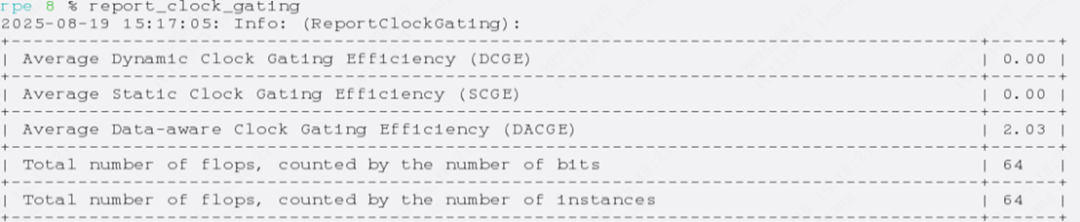

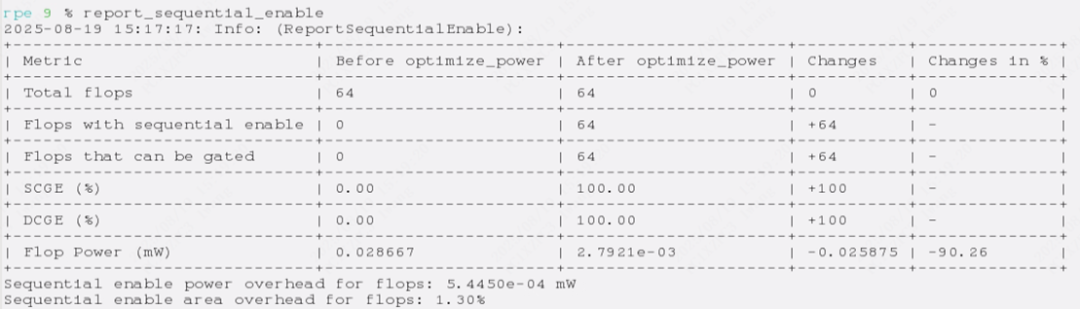

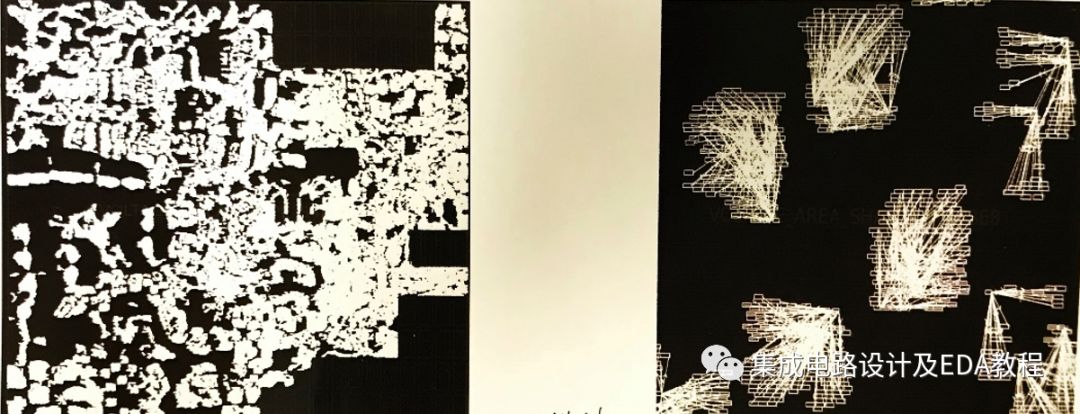

如下圖,為ERPE工具優化RTL代碼后的結果,綜合后的觸發器個數為64,且DCGE以及SCGE的值為0,表示綜合過程找不到任何時鐘門控的可能。但通過ERPE工具對代碼優化后,將SCGE以及DCGE的結果提升到了100%,同時整體功耗下降了90.26%。

report_clock_gating打印結果

report_sequential_enable打印結果

時鐘門控效率是低功耗設計早期階段極具價值的可量化指標,掌握時鐘門控效率,可以高效地降低功耗。從使用ERPA測量初始的SCGE、DCGE,到利用ERPE進行深度優化并獲取具體的RTL修改建議,整個流程環環相扣,讓功耗優化不再是“玄學”,而是由數據驅動的精準工程實踐。

關于英諾達

英諾達(成都)電子科技有限公司是一家由行業頂尖資深人士創立的本土EDA企業,公司堅持以客戶需求為導向,幫助客戶實現價值最大化,為中國半導體產業提供卓越的EDA解決方案。公司的長期目標是通過EDA工具的研發和上云實踐,參與國產EDA完整工具鏈布局并探索適合中國國情的工業軟件上云的路徑與模式,賦能半導體產業高質量發展。公司的主營業務包括:EDA軟件研發、IC設計云解決方案以及IC設計服務。

-

eda

+關注

關注

72文章

3119瀏覽量

183357 -

低功耗

+關注

關注

12文章

3621瀏覽量

106795 -

時鐘門控

+關注

關注

0文章

8瀏覽量

7075 -

英諾達

+關注

關注

1文章

57瀏覽量

2772

原文標題:為什么時鐘門控效率是早期功耗優化最可靠的抓手?

文章出處:【微信號:gh_387c27f737c1,微信公眾號:英諾達EnnoCAD】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

低功耗設計核心指標之時鐘門控效率

低功耗設計核心指標之時鐘門控效率

評論