這款 28 位 1:2 可配置寄存器緩沖器設計用于 1.7V 至 1.9V VCC操作。每個 DIMM 需要一個設備來驅動多達 18 個堆疊的 SDRAM 負載,或者每個 DIMM 需要兩個設備來驅動多達 36 個堆疊的 SDRAM 負載。

除芯片選擇柵極使能 (CSGEN)、控制 (C) 和復位 (RESET) 輸入外,所有輸入均SSTL_18。 它們是 LVCMOS。所有輸出都是邊沿控制電路,針對未端接的DIMM負載進行了優化,符合SSTL_18規格,但漏極開路誤差(QERR)輸出除外。

*附件:74sstub32868a.pdf

74SSTUB32868A 采用差分時鐘(CLK 和 CLK)工作。數據在 CLK 走高和 CLK 走低的交叉點上記錄。

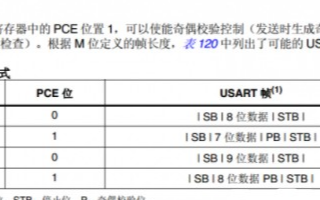

74SSTUB32868A 在奇偶校驗位 (PAR_IN) 輸入端接受來自存儲器控制器的奇偶校驗位,將其與獨立于 DIMM 的 D 輸入(C = 0 時為 D1-D5、D7、D9-D12、D17-D28;C = 1 時為 D1-D12、D17-D20、D22、D24-D28)上接收到的數據進行比較,并指示在 漏極開路 QERR 引腳(低電平有效)。公約是平等的;也就是說,有效奇偶校驗定義為 與 DIMM 無關的數據輸入與奇偶校驗輸入位相結合的 1 個數。要計算奇偶校驗,所有與 DIMM 無關的 D 輸入都必須連接到已知的邏輯狀態。

74SSTUB32868A 包括奇偶校驗功能。奇偶校驗在應用到的數據輸入后一個周期到達,在設備的PAR_IN輸入上進行檢查。數據注冊后兩個時鐘周期,生成相應的 QERR 信號。

如果發生錯誤并且 QERR 輸出被驅動為低電平,則它將保持低電平鎖存至少兩個時鐘周期或 直到RESET被驅動為低電平。如果發生兩個或多個連續奇偶校驗錯誤,則QERR輸出被驅動為低電平并鎖存為低電平,時鐘持續時間等于奇偶校驗錯誤持續時間,或者直到RESET被驅動為低電平。如果在器件進入低功耗模式(LPM)之前,時鐘周期上發生奇偶校驗錯誤,并且QERR輸出被驅動為低電平,則在LPM持續時間加上兩個時鐘周期內或直到RESET被驅動為低電平。與 DIMM 相關的信號(DCKE0、DCKE1、DODT0、DODT1、DCS0 和 DCS1)不包括在奇偶校驗計算中。

C輸入控制從寄存器A配置(低電平時)到寄存器B配置(高電平時)的引腳配置。正常工作期間不應切換 C 輸入。它應該硬連線到有效的低電平或高電平,以將寄存器配置為所需模式。

在DDR2 RDIMM應用中,RESET被指定為相對于CLK和CLK完全異步的 時鐘。因此,無法保證兩者之間的時間關系。進入復位時,寄存器被清除,數據輸出相對于禁用差分輸入接收器的時間快速驅動為低電平。然而,當復位出來時,寄存器相對于時間迅速激活 啟用差分輸入接收器。只要數據輸入為低電平,并且時鐘在從RESET從低到高轉換到輸入接收器完全使能期間保持穩定,74SSTUB32868A的設計就必須確保輸出保持低電平,從而確保輸出上沒有毛刺。

為確保在提供穩定時鐘之前從寄存器獲得定義的輸出,在上電期間必須將RESET保持在低電平狀態。

該器件支持低功耗待機作。當RESET為低電平時,差分輸入接收器為: 禁用和未驅動(浮動)數據、時鐘和基準電壓 (V 裁判 ) 輸入。此外,當RESET為低電平時,所有寄存器都被復位,除QERR外,所有輸出都強制為低電平。LVCMOS RESET和C輸入必須始終保持在有效的邏輯高電平或低電平。

該器件還通過監控系統芯片選擇(DCS0和DCS1)和CSGEN輸入來支持低功耗有源作,并在CSGEN、DCS0和DCS1輸入為高電平時將門控Qn輸出的狀態變化。如果 CSGEN、DCS0 或 DCS1 輸入為低電平,則 Qn 輸出工作正常。此外,如果 DCS0 和 DCS1 輸入均為高電平,則器件將阻止 QERR 輸出發生狀態變化。如果 DCS0 或 DCS1 為低電平,則 QERR 輸出正常工作。RESET輸入優先于DCS0和DCS1控制,當驅動低電平時,Qn輸出為低電平,QERR輸出為高電平。如果芯片選擇控制 不需要功能,則CSGEN輸入可以硬接線到地,在這種情況下,DCS0和DCS1的建立時間要求將與其他D數據輸入相同。控制低功耗 模式,則 CSGEN 輸入應上拉至 VCC通過上拉電阻器。

兩個V裁判引腳(A5 和 AB5)在內部連接在一起大約 150 個。但是,只需連接兩個 V 中的一個裁判引腳連接到外部V裁判電源。未使用的 V裁判引腳應以 V 結尾裁判耦合電容器。

特性

- 德州儀器 (TI) Widebus+ ? 系列成員

- 引腳排列優化了 DDR2 DIMM PCB 布局

- 1 對 2 輸出支持堆疊式 DDR2 DIMM

- 每個 DIMM 需要一個設備

- 芯片選擇輸入可控制數據輸出的狀態變化,并最大限度地降低系統功耗

- 輸出邊沿控制電路可最大限度地降低未端接線路中的開關噪聲

- 支持SSTL_18數據輸入

- 差分時鐘(CLK和CLK)輸入

- 支持芯片選擇柵極使能、控制和RESET輸入上的LVCMOS開關電平

- 檢查與 DIMM 無關的數據輸入上的奇偶校驗

- 支持工業溫度范圍(-40°C 至 85°C)

- 重置輸入禁用差分輸入接收器,復位所有寄存器,并強制所有輸出為低電平,QERR除外

- 應用

- 重載 DDR2 寄存器 DIMM

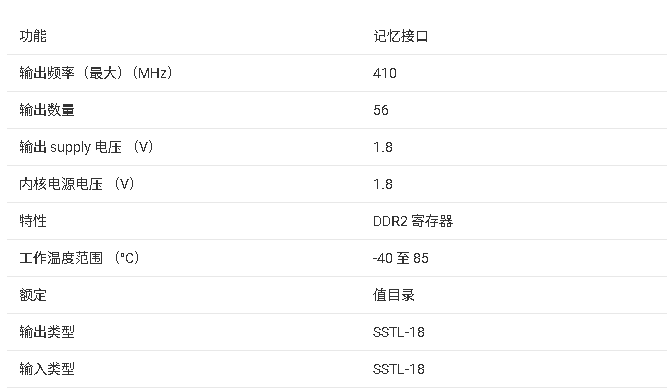

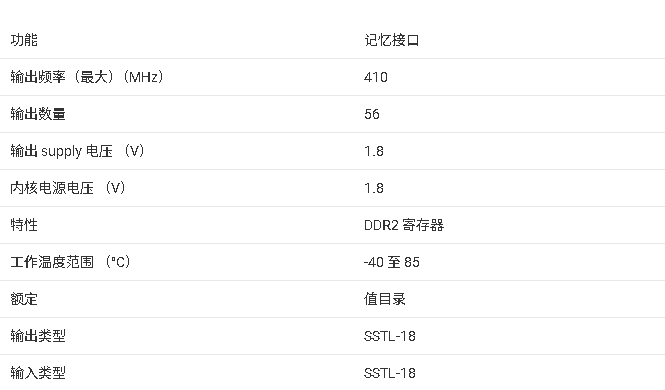

參數

?1. 核心功能特性?

- ?Widebus+?家族成員?:屬于TI高速總線產品線,支持DDR2 DIMM PCB布局優化

- ?配置靈活性?:提供1:2輸出配置,可驅動18個堆疊SDRAM負載(單DIMM)或36個負載(雙DIMM)

- ?低功耗設計?:通過芯片選擇輸入門控數據輸出狀態,降低系統功耗

- ?噪聲控制?:輸出邊緣控制電路減少未端接線路的開關噪聲

- ?工業級溫度支持?:工作溫度范圍-40°C至85°C

?2. 關鍵應用場景?

- 高負載DDR2寄存型DIMM

- 需要地址奇偶校驗的服務器內存模塊

?3. 技術細節?

- ?電壓支持?:1.7V至1.9V VCC操作電壓

- ?輸入/輸出標準?:

- 數據輸入:SSTL_18電平

- 控制輸入(RESET/CSGEN/C):LVCMOS電平

- ?奇偶校驗機制?:

- 支持DIMM獨立數據輸入的奇偶校驗(偶校驗規則)

- 錯誤信號(QERR)在數據注冊后2個時鐘周期生成

- 可檢測連續錯誤并保持鎖定狀態直至復位

?4. 封裝與訂購信息?

?5. 時序特性?

- 最大時鐘頻率:410MHz

- 建立/保持時間:數據輸入相對CLK需滿足500ps時序要求

- 傳播延遲:CLK到Q輸出典型值1.1ns(最大1.6ns)

?6. 特殊功能模式?

- ?低功耗模式?:通過RESET控制可禁用差分接收器

- ?配置選擇?:C引腳硬連線選擇Register-A/B配置模式

- ?芯片選擇門控?:CSGEN信號動態控制數據鎖存時機

?7. 安全注意事項?

該文檔完整描述了器件功能、電氣特性、時序參數及應用設計要點,適用于高性能內存系統的硬件開發。

-

寄存器

+關注

關注

31文章

5612瀏覽量

130274 -

緩沖器

+關注

關注

6文章

2234瀏覽量

48970 -

控制電路

+關注

關注

83文章

1752瀏覽量

138797 -

DIMM

+關注

關注

0文章

41瀏覽量

10145 -

LVCMOS

+關注

關注

1文章

142瀏覽量

12027

發布評論請先 登錄

DES使用一個56位的密鑰以及附加的8位奇偶校驗位詳細資料說明

單片機串口分析起始位停止位奇偶校驗位

什么是奇偶校驗 奇偶校驗的基本原理 奇偶校驗電路什么意思

什么是奇偶校驗電路?奇偶校驗器是時序邏輯電路嗎?

8位到9位奇偶校驗總線收發器SN74BCT29854數據表

?74SSTUB32868 28位至56位帶地址奇偶校驗的注冊緩沖器技術文檔總結

?74SSTUB32868A 28位至56位帶地址奇偶校驗的注冊緩沖器技術文檔總結

?74SSTUB32868A 28位至56位帶地址奇偶校驗的注冊緩沖器技術文檔總結

評論