?

第一章********核心板簡介

[]()1.1產品簡介

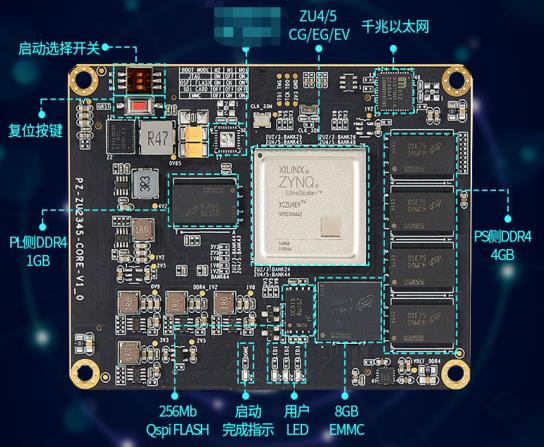

璞致 ZU2/3/4/5 核心板采用 XILINX 公司的 ZynqUltraScale2/3/4/5 芯片作為主控制器, 核心板做了兼容設計,對于 ZU2/3/4/5 芯片細分的CG/EG/EV,我們也都做了兼容設計,對于 底板設計完全兼容。核心板采用 3 個 0.6mm 間距 120P 鍍金連接器與母板連接,核心板四 個腳放置了 4 個3.5mm 固定孔,此孔可以與底板通過螺絲緊固,確保了在強烈震動的環境 下穩定運行。

[]()[]()1.2********產品規格

| 璞致 ZU2/ZU3/ZU4/ZU5 工業級核心板規格 |

|---|

| 主控制器 |

| 主控制器封裝 |

| DDR4/DDR4L |

| QSPI FLASH |

| EMMC |

| 啟動方式 |

| 千兆以太網 |

| 用戶 LED |

| IO 數量 |

| GTX 接口數量 |

| 工作電壓/電流 |

| 工作溫度 |

| 核心板尺寸、工藝 |

| 與底板扣接高度 |

[]()[]()1.3********產品外觀

?編輯

?編輯

[]()[]()1.4********產品尺寸

核心板尺寸為 83.8x64.8mm,核心板通過背面的 3 顆 0.6mm/120P 鍍金高速連接器與底 板連接,合高 3mm。如下圖是核心板的尺寸標注。

?編輯

[]()[]()[]()[]()第二章********核心板使用說明

[]()2.1********核心板供電

核心板供電電壓是 5V,在核心板的四個角都留有電源輸入管腳, 電源管腳在模塊內部 已做了連通,此設計是為了方便底板的電源接入,設計時只需要連接一個角上的電源管腳, 核心板即可工作。電源連接需用銅皮連接且打足夠的過孔保證電源通流能力。核心板上的所 有 GND 信號都需要連接到底板上,每個 GND 通過兩個過孔與底板連接以確保通流能力 。 核心板的極限電流在 5V/3A,所以外部供電需要考慮極限電流情況以保證核心板工作穩定。

給模組供電的電源輸出電壓需要穩定 ,在模組電源輸入加一級 DCDC 電源轉換,從高 電壓轉到 5V,DCDC 電流輸出能力可以選 5A 左右 ,如電源芯片 MP2482/MP2225 可以參 考 。在模組電源輸入處需放置 2 顆 220uF/10V 電容保證電源質量,如果是使用鉭電容,最 好用一個 1 歐姆 0805 電阻與電容串聯,以保證鉭電容的穩定性。

?編輯

[]()[]()2.2********核心板時鐘

核心板為 PS 側提供了 33.333Mhz 的時鐘輸入,輸入的管腳位置為 PS_REF_CLK;為 PL 側提供了 200Mhz 的 差分 時 鐘 輸 入 , PL 側 的 時 鐘 輸 入 管 腳 是 FPGA_12P_GC_65/ FPGA_12N_GC_65,管腳位置是 L3/L2;為 PL 側 GTX 提供了一路 125Mhz 的差分時鐘輸入, 輸入位置是 GTX 的 BANK224 的 CLK1,管腳位號是 V6/V5。另外, 125Mhz 時鐘只在 ZU4/5 上提供,ZU2/3 上沒有 GTX 接口,無法使用 。如下圖列出了連接方式。

[]()[]()2.3********核心板全局復位

核心板提供了 nGST 復位按鍵,為系統復位按鍵,低電平有效。此引腳也引出到了連接 器,信號名稱為 SYS_nRST_I,方便外部加入復位按鍵或者設計看門狗復位電路用。同時為了 系統穩定,我們在核心板上加了復位芯片 MAX811SEUS,復位輸出信號也引出到了連接器 上,信號名稱為 SYS_nRST_O,此信號可以用于單板其他外設的復位用,信號電平是 3.3V。 復位腳為 PS/PL 共用復位,連接到 PS 側的 PS_POR_500(D21)引腳上和 PL 側 BANK34 的 IO_L3N_34(G9)管腳。

如果底板上需要設計復位電路有以下幾種情況需考慮。

1) 復位電路底板內部使用,只需要對地添加復位按鍵和一個 10uF 電容并口即可。

2) 復位電路需要預留在結構上供外部使用,需要添加對地按鍵,同時對地并聯 10uF 電 容和 TVS 防靜電器件。

?編輯

[]()[]()2.4********核心板啟動方式

核心板支持四種啟動模式,分別是 JTAG 、QSPI Flash 、EMMC 、SD 卡。板載了前三種 方式,SD 卡方式用戶可以通過在底板上連接實現。 四種啟動方式可以通過板載的撥碼開關 來選擇。如下圖已列出各個模式撥碼開關所在的位置。因主芯片發熱量較大,所以在核心板 上需要加散熱片,會遮擋 BOOT MODE 選擇表格。

?編輯

[]()[]()2.5********網口連接

核心板上放置了一顆千兆以太網芯片 KSZ9031,以太網芯片與 ZYNQ 芯片之間通過 RGMII 接口互聯,連接對應管腳見下表, 以太網對外連接只需要一個帶變壓器的 RJ45 即可 使用,芯片地址 PHY_AD[2:0]=001,連接原理圖可參考下圖(產品電路需加 ESD 保護電路)。

| RMGII 信號 | 管腳名稱 | 管腳位置 |

|---|---|---|

| GTX_CLK | MIO26_501 | L15 |

| TXD0 | MIO27_501 | J15 |

| TXD1 | MIO28_501 | K15 |

| TXD2 | MIO29_501 | G16 |

| TXD3 | MIO30_501 | F16 |

| TX_EN | MIO31_501 | H16 |

| RX_CLK | MIO32_501 | J16 |

| RXD0 | MIO33_501 | L16 |

| RXD1 | MIO34_501 | L17 |

| RXD2 | MIO35_501 | H17 |

| RXD3 | MIO36_501 | K17 |

| RX_CTL | MIO37_501 | J17 |

| MDC | MIO76_502 | B20 |

| MDIO | MIO77_502 | F20 |

?編輯

[]()[]()2.6EMMC管腳定義

板載 EMMC 容量 8GB,型號為 THGBMFG6C1LBAIL,管腳定義如下表

| EMMC********引腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| EMMC_D0 | MIO13 | AH18 |

| EMMC_D1 | MIO14 | AG18 |

| EMMC_D2 | MIO15 | AE18 |

| EMMC_D3 | MIO16 | AF18 |

| EMMC_D4 | MIO17 | AC18 |

| EMMC_D5 | MIO18 | AC19 |

| EMMC_D6 | MIO19 | AE19 |

| EMMC_D7 | MIO20 | AD19 |

| EMMC_CLK | MIO22 | AB20 |

| EMMC_CMD | MIO21 | AC21 |

| EMMC_nRST | MIO23 | AB18 |

[]()[]()2.7QSPIFLASH

核心板設計了兩路 QSPI FLASH,容量為 32MB 的 QSPI FLASH,QSPI0 為默認貼片的, QSPI1 為預留的,不貼片 。QSPI FLASH 可用于存儲啟動文件和用戶文件。

| QSPI0FLASH引腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| DATA0 | MIO4 | AH16 |

| DATA1 | MIO1 | AG16 |

| DATA2 | MIO2 | AF15 |

| DATA3 | MIO3 | AH15 |

| QSPI_CS | MIO5 | AD16 |

| QSPI_CLK | MIO0 | AG15 |

| []()QSPI1FLASH引腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| DATA0 | MIO8 | AF17 |

| DATA1 | MIO9 | AC16 |

| DATA2 | MIO10 | AD17 |

| DATA3 | MIO11 | AE17 |

| QSPI_CS | MIO7 | AH17 |

| QSPI_CLK | MIO12 | AC17 |

[]()2.8板載LED

為方便調試,核心板上放置了三顆 LED,LED 連接到 PL 側,LED 的管腳位置如下表, 當管腳輸出高電平時 LED 點亮,低電平 LED 滅。

| 序號 | 管腳名稱 | 管腳位置 |

|---|---|---|

| LED1 | IO-T1U-64 | AH6 |

| LED2 | IO-T2U-64 | AB5 |

| LED3 | IO-T3U-64 | AE4 |

[]()[]()2.9BANK接口電平選擇

單板上 BANK64/66 為 HP-BANK,接口電平配置為 1.2/1.8V, 可以通過單板上 提供的指示進行 0 歐姆電阻選焊來調節電壓,默認電平為 1.8V。另外對于 ZU2/3 和 ZU4/5,HR-BANK 的命名有所差異,對于 ZU2/3 有 BANK24/25/26/44,對于 ZU4/5 有 BANK44/45/46/43,兩者 BANK 分別對應, 管腳兼容,BANK 電平可以實現 1.8V/2.5V/3.3V 三種電平轉換,更換電阻位置即可,默認電平為 3.3V。

?編輯

[]()[]()2.10PS側********DDR

PS 側配置了四顆工業級 DDR4 芯片,單顆容量 1GB, 四顆共計容量為 4GB,型號為 MT40A512M16LY-062E,DDR4 管腳分配直接調用系統分配即可。也可以參考我司提供的例 程。

[]()[]()2.11PL側********DDR

PL 側配置了一顆工業級 DDR4 芯片,單顆容量 1GB,型號為 MT40A512M16LY-062E, DDR4L 管腳分配參見下表。

| DDR4********引腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| DDR4_D0 | IO-L20P-65 | J6 |

| DDR4_D1 | IO-L24P-65 | H9 |

| DDR4_D2 | IO-L21P-65 | J7 |

| DDR4_D3 | IO-L23P-65 | K9 |

| DDR4_D4 | IO-L21N-65 | H7 |

| DDR4_D5 | IO-L23N-65 | J9 |

| DDR4_D6 | IO-L20N-65 | H6 |

| DDR4_D7 | IO-L24N-65 | H8 |

| DDR4_DM0 | IO-L19P-65 | J5 |

| DDR4_DQS_P0 | IO-L22P-65 | K8 |

| DDR4_DQS_N0 | IO-L22N-65 | K7 |

| DDR4_D8 | IO-L14P-65 | M6 |

| DDR4_D9 | IO-L17N-65 | N8 |

| DDR4_D10 | IO-L15N-65 | N6 |

| DDR4_D11 | IO-L15P-65 | N7 |

| DDR4_D12 | IO-L18N-65 | L8 |

| DDR4_D13 | IO-L17P-65 | N9 |

|---|---|---|

| DDR4_D14 | IO-L14N-65 | L5 |

| DDR4_D15 | IO-L18P-65 | M8 |

| DDR4_DM1 | IO-L13P-65 | L7 |

| DDR4_DQS_P1 | IO-L16P-65 | P7 |

| DDR4_DQS_N1 | IO-L16N-65 | P6 |

| DDR4_A0 | IO-L8N-65 | H1 |

| DDR4_A1 | IO-L3P-65 | U8 |

| DDR4_A2 | IO-L8P-65 | J1 |

| DDR4_A3 | IO-L3N-65 | V8 |

| DDR4_A4 | IO-L11P-65 | K4 |

| DDR4_A5 | IO-L4P-65 | R8 |

| DDR4_A6 | IO-L9N-65 | J2 |

| DDR4_A7 | IO-L2P-65 | U9 |

| DDR4_A8 | IO-L9P-65 | K2 |

| DDR4_A9 | IO-L1P-65 | W8 |

| DDR4_A10 | IO-L4N-65 | T8 |

| DDR4_A11 | IO-L7N-65 | K1 |

| DDR4_A12 | IO-L6N-65 | T6 |

| DDR4_A13 | IO-L1N-65 | Y8 |

| DDR4_A14 | IO-L11N-65 | K3 |

| DDR4_A15 | IO-L5P-65 | R7 |

| DDR4_A16 | IO-T2U-65 | P9 |

| DDR4_BA0 | IO-T1U-65 | H2 |

| DDR4_BA1 | IO-L5N-65 | T7 |

| DDR4_BG0 | IO-2N-65 | V9 |

| DDR4_CS | IO-L6P-65 | R6 |

| DDR4_nACT | IO-L13N-65 | L6 |

| DDR4_ODT | IO-L19N-65 | J4 |

| DDR4_RESET | IO-L7P-65 | L1 |

| DDR4_CLK_P | IO-L10P-65 | H4 |

| DDR4_CLK_N | IO-L10N-65 | H3 |

| DDR4_CKE | IO-T3U-65 | K5 |

[]()[]()[]()[]()第三章********底板設計注意事項

[]()3.1電源部分PCB********設計

電源輸入需要鋪銅皮連接,打足夠的過孔保證通電流能力,但電源電壓較高,干擾較大, 在保證通流的條件下不要讓這個銅皮更大,以免干擾其他信號。地管腳需要連接到地平面上, 且一個地管腳需要打兩個過孔,保證通流和充分連接。

?編輯

[]()[]()3.2********高速接口布局走線

1)USB 口:

USB PHY 芯片的并口速率在 60Mhz,并口走線需要保證等長,且長度不大于 1000mil (25.4mm), 所以 PHY 盡量靠近模組放置,USB 差分線 DP/DM 可以拉的長一些。

2)千兆以太網:

與 RJ45 端連接的信號需要保持等長,RGMII 接口的 TX 部分與 RX 部分需要單獨保持等 長。

3)HDMI 接口

HDMI 接口信號需要走差分,且差分之間需保持等長控制。

[]()[]()3.3LVDS信號

模組的 BANK 電平可以在 1.2/1.8V/2.5V/3.3V 三種電平之間選擇,默認為 3.3V 電平,如 果需要工作在 LVDS 模式下,需要把接口電平調整為 1.8V 或者 2.5V。同時底板的 LVDS 信 號走線需做差分/阻抗控制處理,并且差分之間保持等長。

[]()[]()3.4GTX信號走線

GTX 走線需要考慮的問題比較多,對于有疑問的用戶可以聯系客服接入技術支持。

[]()[]()3.5********產品防護

對于產品設計,需要在各類接口加上防護電路。需按防護等級需求進行設計。

[]()[]()[]()[]()第四章********核心板管腳與信號等長

[]()4.1********核心板管腳定義

PZ-ZU2/3/4/5 核心板共引出 PS 側 38 個管腳,PL 側 192 根管腳,PL 管腳其中有 96 根信號電平 1.2/1.8V,96 根信號可以 1.8/2.5/3.3V 三種電平調節。詳細的管腳定義參見文件 夾《PZ-ZU23CGEG 核心板管腳與等長》《PZ-ZU45CGEGEV 核心板管腳與等長》。

[]()[]()4.2********信號等長

為方便用戶設計底板以及信號走高速,我們提供了 J1-J3 連接器上的走線長度數據, 方便用戶協同底板設計。詳細數據表格參見文件夾《PZ-ZU23CGEG 核心板管腳與等長》《PZ- ZU45CGEGEV 核心板管腳與等長》。

?

審核編輯 黃宇

-

FPGA

+關注

關注

1660文章

22421瀏覽量

636624 -

開發板

+關注

關注

26文章

6297瀏覽量

118305 -

核心板

+關注

關注

6文章

1400瀏覽量

32030

發布評論請先 登錄

如何在Zynq UltraScale+ MPSoC平臺上通過JTAG啟動嵌入式Linux鏡像

新品上市!AMD Zynq UltraScale+MPSoC EG異構多處理開發平臺

fpga開發板 璞致 Kintex UltraScale Plus PZ-KU3P 與 PZ-KU5P核心板與開發板用戶手冊

FPGA開發板—璞致 Kintex-7 系列核心板PZ-K7325T/PZ-K7410T 使用說明 XILINX核心板簡介

fpga開發板 璞致ZYNQ 7000 系列之 PZ7035/PZ7045/PZ7100-FH 核心板與開發板用戶手冊

【PZ7020-StarLite 入門級開發板】——FPGA 開發的理想起點,入門與工業場景的雙重優選

璞致電子 UltraScale+ RFSoC 架構下的軟件無線電旗艦開發平臺

PZ/璞致【PZ-ZU19EG-KFB】—ZYNQ UltraScale + 賦能異構計算與高性能嵌入式系統開發

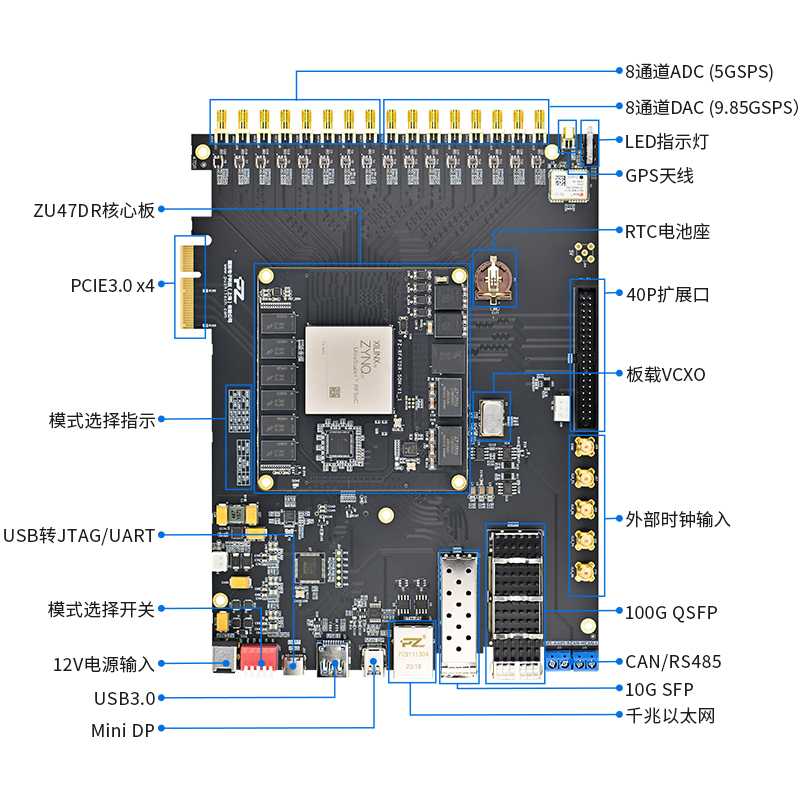

PZSDR/璞致【PZ-ZU47DR-KFB】——RFSoC 架構下的超寬帶軟件無線電開發平臺標桿

【PZ-ZU15EG-KFB】——ZYNQ UltraScale + 異構架構下的智能邊緣計算標桿

FPGA開發板—璞致 ZYNQ UltraScale+ MPSOC PZ-ZU2/3/4/5 核心板簡介

FPGA開發板—璞致 ZYNQ UltraScale+ MPSOC PZ-ZU2/3/4/5 核心板簡介

評論