對于需要實時響應(yīng)的數(shù)據(jù)中心工作負(fù)載,性能不僅是指原始吞吐量或處理能力。挑戰(zhàn)在于:在保持吞吐量和能效的同時,實現(xiàn)確定性時延。

CPU 和 GPU 仍將是基礎(chǔ)架構(gòu)。但正如系統(tǒng)架構(gòu)師和數(shù)據(jù)中心運(yùn)營商所發(fā)現(xiàn)的,在時延控制變得至關(guān)重要時,傳統(tǒng)計算架構(gòu)往往會遇到困難。對于那些尋求對性能、功耗和時延進(jìn)行精細(xì)控制的用戶來說,采用硬件自適應(yīng)加速卡的自適應(yīng)計算正在成為一種戰(zhàn)略選項。

如果您正在探索如何加速實時工作負(fù)載,以下是一些基本考慮因素,有助于指導(dǎo)該過程,并著重介紹自適應(yīng)計算的用武之地。

針對實時(而非只是原始)吞吐量構(gòu)建

對于許多工作負(fù)載而言,可預(yù)測的響應(yīng)時間至關(guān)重要。無論是在高頻交易中,還是在數(shù)據(jù)流傳感器處理中,僅靠快是不夠的。您必須確保可靠情況下的快速性——無論輸入變化或系統(tǒng)負(fù)載如何。CPU 和 GPU 擁有類似的編程模型,但依賴于線程調(diào)度和固定的存儲器緩存層次結(jié)構(gòu),這可能會影響低時延響應(yīng)時間。在這些架構(gòu)上實現(xiàn)確定性性能通常需要過度配置( overprovisioning )資源、微調(diào)( fine-tuning )軟件堆棧或隔離工作負(fù)載——這些都無法保證在不同系統(tǒng)負(fù)載下保持一致的時延。

由現(xiàn)場可編程門陣列( FPGA )或自適應(yīng) SoC(集成處理器子系統(tǒng)和專用 IP 的 FPGA)提供支持的加速卡通過提供硬件并行性和數(shù)據(jù)路徑優(yōu)化來解決這一問題。該架構(gòu)可在電路層面進(jìn)行動態(tài)編程,其中數(shù)據(jù)路徑經(jīng)過定制并“硬連接”至硅片本身,從而避免了不可預(yù)測的軟件指令周期。這種方法能夠?qū)崿F(xiàn)始終如一的低時延性能,并對數(shù)據(jù)的處理及移動方式進(jìn)行精細(xì)控制。

內(nèi)存比您認(rèn)為的更重要

在這些性能敏感型環(huán)境中,內(nèi)存往往是隱藏的瓶頸。這不僅關(guān)乎加速器可用的內(nèi)存大小,還關(guān)乎內(nèi)存與計算的距離有多近,以及運(yùn)行時的訪問速度有多快。這正是自適應(yīng)計算提供架構(gòu)優(yōu)勢的地方,尤其是與片上高帶寬存儲器( HBM )結(jié)合使用時。

HBM 是一種成熟的 3D 封裝 DRAM 技術(shù),具備每秒 TB 級的帶寬,可滿足數(shù)據(jù)密集型加速卡的需求。但 FPGA 和自適應(yīng) SoC 還為它們帶來了靈活應(yīng)變的存儲器層次結(jié)構(gòu),其中包括緊鄰處理邏輯、大小各異的嵌入式片上 SRAM。這可以實現(xiàn)快速、低時延的緩沖和中間存儲,無需往返外部 DRAM。對于流式應(yīng)用或?qū)崟r AI 推理,這種接近性可降低時延并提升吞吐量,而不會阻塞流水線。

將您的加速卡直接連接至網(wǎng)絡(luò)

如果您的加速卡會處理來自網(wǎng)絡(luò)的流式數(shù)據(jù),為何不將其直接連接至網(wǎng)絡(luò)?傳統(tǒng)的加速卡依靠 PCIe接收傳入數(shù)據(jù)——通常經(jīng)過網(wǎng)絡(luò)接口卡( NIC )進(jìn)行路由,然后通過主機(jī) CPU 和系統(tǒng)內(nèi)存,最終到達(dá)加速器。這會帶來時延并消耗資源。

基于 FPGA 的網(wǎng)絡(luò)連接加速卡可直接連接以太網(wǎng),從而實現(xiàn)在數(shù)據(jù)到達(dá)時進(jìn)行實時處理。這也為高性能計算( HPC )環(huán)境提供了經(jīng)由以太網(wǎng)的可擴(kuò)展計算集群。

隨工作負(fù)載演進(jìn)調(diào)整您的加速卡,

而非基礎(chǔ)架構(gòu)

如今推動您的基礎(chǔ)設(shè)施發(fā)展的工作負(fù)載與未來擴(kuò)展基礎(chǔ)架構(gòu)的工作負(fù)載將有所不同,而自適應(yīng)計算能夠隨著應(yīng)用發(fā)展而演進(jìn)。例如,在網(wǎng)絡(luò)防火墻中,加密協(xié)議和威脅檢測模型在不斷演進(jìn)。在同一服務(wù)器節(jié)點(diǎn)上部署壓縮、解壓縮和分析功能的存儲機(jī)架中,靈活的硬件可以隨著數(shù)據(jù)量的增長或壓縮格式的改變而調(diào)整計算管線。

同一加速卡的架構(gòu)靈活性可以帶來長期效益,不僅能實現(xiàn)實時性能,還能在工作負(fù)載需求變化時保持敏捷性——所有這些都在同一張卡、同一臺服務(wù)器和同一個機(jī)架上實現(xiàn)。

借助適合的硬件專業(yè)技術(shù)加速部署

要最大限度提升基于 FPGA 的加速卡性能,需要獲得 FPGA 開發(fā)人員的幫助。無論是通過內(nèi)部團(tuán)隊、設(shè)計合作伙伴,還是預(yù)構(gòu)建 FPGA IP 的提供商,成功都取決于能否構(gòu)建或集成滿足嚴(yán)格時延、吞吐量和內(nèi)存訪問要求的特定應(yīng)用邏輯。

為了加快部署速度,需要尋找一款可提供強(qiáng)大 FPGA 工具鏈、預(yù)驗證 IP 和合作伙伴生態(tài)系統(tǒng)的平臺,該平臺支持從 RTL 開發(fā)到完整解決方案集成的所有環(huán)節(jié)——助力您的團(tuán)隊滿懷信心地從概念走向量產(chǎn)。

下一步

這些只是低時延和工作負(fù)載靈活應(yīng)變性至關(guān)重要的幾項考慮因素。盡管 CPU 和 GPU 仍然作為數(shù)據(jù)中心的核心,但它們并非永遠(yuǎn)最適合流式工作負(fù)載。自適應(yīng)平臺——例如集成 HBM 的 AMD Alveo V80 計算加速卡——則提供了另一條途徑。憑借連網(wǎng)連接、自適應(yīng)硬件架構(gòu)和高帶寬存儲器,Alveo V80 計算加速卡可以在最關(guān)鍵時刻提供實時性能。

-

處理器

+關(guān)注

關(guān)注

68文章

20250瀏覽量

252186 -

cpu

+關(guān)注

關(guān)注

68文章

11277瀏覽量

224934 -

數(shù)據(jù)中心

+關(guān)注

關(guān)注

18文章

5647瀏覽量

75008

原文標(biāo)題:在數(shù)據(jù)中心進(jìn)行實時加速

文章出處:【微信號:賽靈思,微信公眾號:Xilinx賽靈思官微】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

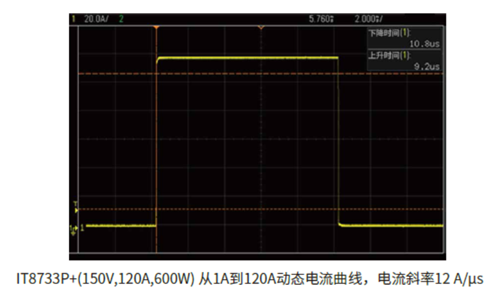

艾德克斯IT8700P+多通道電子負(fù)載測試特性及應(yīng)用

【產(chǎn)品介紹】Altair PBS Professional HPC工作負(fù)載管理器和作業(yè)調(diào)度管理系統(tǒng)

新思科技HAPS技術(shù)助力Skymizer加速HyperThought開發(fā)

高精度可編程直流負(fù)載箱—專攻氫燃料電池充放電測試與動態(tài)消納

如何匹配晶振的負(fù)載電容

直流負(fù)載箱的主要功能有哪些?

通過NVIDIA RTX PRO服務(wù)器加速企業(yè)工作負(fù)載

為什么要用電子負(fù)載?

直流電子負(fù)載是直流負(fù)載嗎?

基于RAKsmart云服務(wù)器的AI大模型實時推理方案設(shè)計

電子負(fù)載的動態(tài)負(fù)載模擬

動力電池測試中的直流負(fù)載挑戰(zhàn)與應(yīng)對策略

NVIDIA加速的Apache Spark助力企業(yè)節(jié)省大量成本

如何加速實時工作負(fù)載

如何加速實時工作負(fù)載

評論