Texas Instruments LMKDB1超低抖動時鐘緩沖器是一系列超低抖動LP-HCSL緩沖器和MUX,支持PCIe Gen 1至Gen 6,符合DB2000QL標準。這些器件具有靈活的上電序列、故障安全輸入、獨立的輸出啟用和禁用引腳、輸入信號丟失 (LOS) 檢測和自動輸出禁用功能,以及出色的電源噪聲抑制性能。支持1.8V和3.3V兩種電源電壓。對于Texas Instruments LMKDB1120,與3.3V相比,1.8V電源可節省250mW功率。

數據手冊:*附件:Texas Instruments LMKDB1超低抖動時鐘緩沖器數據手冊.pdf

特性

- LP-HCSL時鐘緩沖器和時鐘MUX支持

- PCIe Gen 1至Gen 6

- CC(通用時鐘)和IR(獨立參考)PCIe架構

- 帶或不帶SSC的輸入時鐘

- 符合 DB2000QL

- 所有設備均符合DB2000QL規范

- LMKDB1120引腳兼容DB2000QL

- 超低附加抖動:

- 156.25MHz時最大31fs 12kHz至20MHz RMS附加抖動

- PCIe Gen 4的最大附加抖動為13fs

- PCIe Gen 5的最大附加抖動為5fs

- PCIe Gen 6的最大附加抖動為3fs

- 故障安全輸入

- 靈活的上電序列

- 自動輸出禁用

- 單獨輸出使能

- 用于啟用或禁用高速輸出的SBI(邊帶接口

- LOS(信號丟失)輸入檢測

- 輸出阻抗:85Ω或100Ω

- 電源:1.8V/3.3V (±10%)

- 環境溫度范圍:-40 °C至105 °C

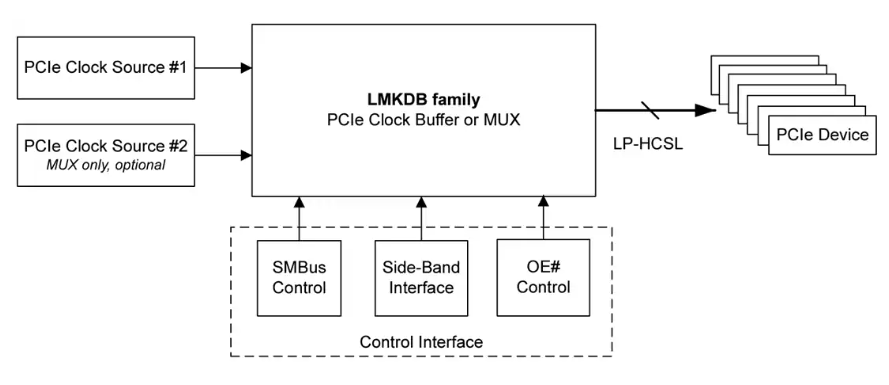

典型應用

德州儀器LMKDB11xx超低抖動時鐘緩沖器技術解析

概述

德州儀器(TI)的LMKDB11xx系列是專為PCIe Gen 1至Gen 7應用設計的超低抖動LP-HCSL時鐘緩沖器家族,符合DB2000QL規范。該系列產品在?高性能計算、服務器主板、NIC/SmartNIC和硬件加速器?等領域有廣泛應用。其主要特點包括極低的附加抖動、靈活的電源上電序列、故障安全輸入/輸出、獨立輸出使能控制等。

關鍵特性

超低抖動性能

- ?PCIe Gen 5附加抖動?:僅5fs(最大值)

- ?PCIe Gen 6附加抖動?:僅3fs(最大值)

- ?PCIe Gen 7附加抖動?:僅2.1fs(最大值)

- ?156.25MHz下12kHz-20MHz RMS附加抖動?:31fs(最大值)

靈活配置選項

- 支持1.8V和3.3V雙電源電壓

- 85Ω或100Ω可編程輸出阻抗(LMKDB1102)

- 可編程輸出擺幅(600mV至975mV,25mV/步進)

- 可編程輸出斜率(16種可選設置)

系統可靠性

- 故障安全輸入(所有型號)

- 故障安全輸出(帶"FS"后綴型號)

- 自動輸出禁用功能

- 輸入信號丟失檢測(LOS)

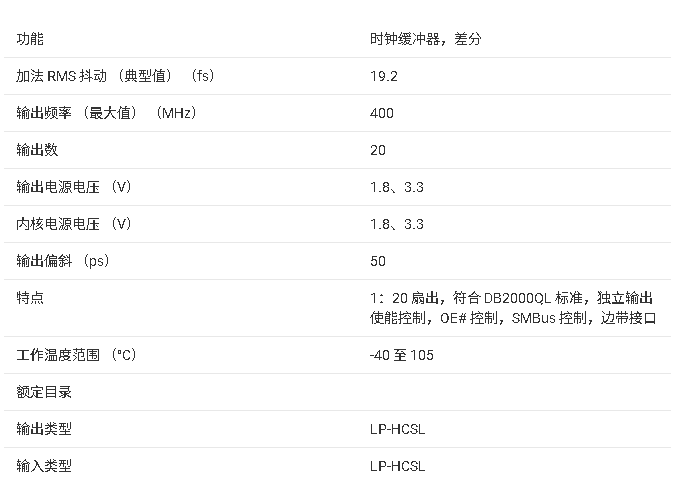

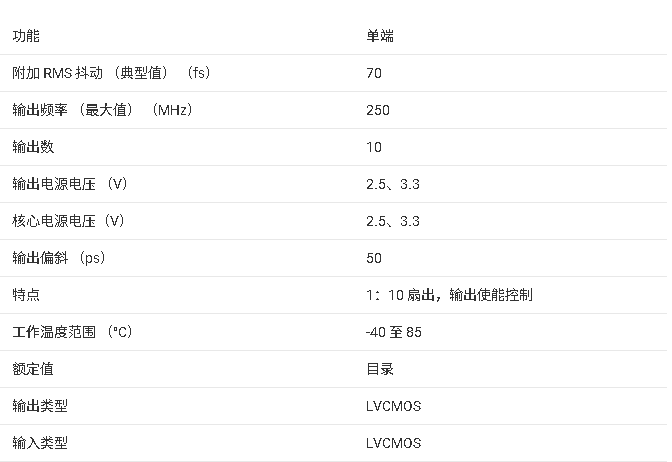

產品系列與選型

LMKDB11xx系列包含多種型號,主要區分如下:

| 型號 | 輸出數量 | 封裝尺寸 | 特殊功能 |

|---|---|---|---|

| LMKDB1120/FS | 20 | 6mm×6mm (NPP) | 故障安全輸出(FS型號) |

| LMKDB1108/FS | 8 | 5mm×5mm (RKP) | 故障安全輸出(FS型號) |

| LMKDB1104/FS | 4 | 4mm×4mm (REX) | 故障安全輸出(FS型號) |

| LMKDB1102 | 2 | 3mm×3mm (REY) | 可編程輸出阻抗 |

應用設計要點

電源設計

布局建議

時鐘輸入配置

支持四種輸入配置方式:

控制接口

LMKDB11xx提供三種控制方式,可同時使用:

1. SMBus模式

- 通過SMB_DATA和SMB_CLK引腳進行寄存器讀寫

- 支持塊讀寫操作

- 可配置器件地址(通過SADR1和SADR0引腳設置)

2. 邊帶接口(SBI)模式

- 3線或4線串行接口(SHFT_LD#、SBI_IN、SBI_CLK和可選的SBI_OUT)

- 比SMBus更快的輸出使能/禁用速度(最高25MHz)

- 支持星型和菊花鏈拓撲

3. 引腳模式

- 通過專用OE#引腳直接控制輸出使能

- 當不使用SMBus或SBI時,相關引腳可懸空

典型應用示例

?PCIe時鐘分配系統?:

- 輸入:100MHz PCIe時鐘源

- 輸出:15路PCIe Gen5時鐘

- 選用LMKDB1120(20輸出)

- 計算抖動預算:sqrt(502 - 452) = 21fs

- 器件實際附加抖動:13fs(滿足要求)

?以太網時鐘分配系統?:

- 輸入:156.25MHz以太網時鐘

- 輸出:7路以太網時鐘

- 選用LMKDB1108(8輸出)

- 計算抖動預算:sqrt(1002 - 902) = 43fs

- 器件實際附加抖動:31fs(滿足要求)

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

時鐘緩沖器

+關注

關注

2文章

270瀏覽量

51910 -

Mux

+關注

關注

0文章

44瀏覽量

24138 -

低抖動

+關注

關注

0文章

62瀏覽量

6073

發布評論請先 登錄

相關推薦

熱點推薦

德州儀器推出超低噪聲底限及附加抖動時鐘緩沖器

日前,德州儀器 (TI) 宣布推出 2 款最新通用時鐘緩沖器系列,進一步壯大其高性能時鐘緩沖器產品陣營。CDCLVC1310 LVCMOS

發表于 04-05 08:47

?1447次閱讀

LMKDB1120和LMKDB1108超低抖動PCIe第1代到第6代LP-HCSL時鐘緩沖器數據表

電子發燒友網站提供《LMKDB1120和LMKDB1108超低抖動PCIe第1代到第6代LP-HCSL時鐘

發表于 08-20 10:51

?0次下載

?LMKDB11xx系列PCIe時鐘緩沖器技術文檔總結

LMKDB 器件是一系列極低抖動的 LP-HCSL 緩沖器,支持 PCIe Gen 1 至 Gen 7,并且符合 DB2000QL 標準。這些器件提供靈活的上電順序、故障安全輸入、故障安全輸出、單獨的輸出有源和非有源引腳、輸入信

CDCLVC1110 低抖動、1:10 LVCMOS 扇出時鐘緩沖器技術手冊

CDCLVC11xx 是德州儀器 (TI) 的模塊化、高性能、低偏斜、通用時鐘緩沖器系列。

整個系列的設計都考慮到了模塊化方法。它旨在匯總 TI 的 LVCMOS

LMKDB11xx系列:PCIe時鐘緩沖器的卓越之選

LMKDB11xx系列:PCIe時鐘緩沖器的卓越之選 在當今高速發展的電子世界里,PCIe技術的應用范圍越來越廣泛,從服務器到高性能計算系統

LMKDB11xx系列PCIe時鐘緩沖器深度解析

了眾多工程師的首選。本文將深入剖析該系列產品,為電子工程師們提供全面的技術參考。 文件下載: lmkdb1104.pdf 一、產品概述 LMKDB11xx是一系列超低

探索LMKDB11xx:PCIe時鐘緩沖器的卓越之選

Gen 7超低抖動LP - HCSL時鐘緩沖器,以其卓越的性能和豐富的特性,為工程師們提供了理想的解決方案。 文件下載: lmkdb1102

探秘LMKDB11xx:PCIe時鐘緩沖器的卓越之選

探秘LMKDB11xx:PCIe時鐘緩沖器的卓越之選 在當今高速發展的電子領域,PCIe技術不斷演進,對時鐘

德州儀器CDCDB400:PCIe時鐘緩沖器的理想之選

德州儀器CDCDB400:PCIe時鐘緩沖器的理想之選 在電子設計領域,時鐘緩沖器對于確保系統時鐘

德州儀器LMK1C110x時鐘緩沖器的特性與設計應用

德州儀器LMK1C110x時鐘緩沖器的特性與設計應用 在電子設計領域,時鐘緩沖器是確保信號穩定傳輸和同步的關鍵組件。

深入解析LMK00105:超低抖動LVCMOS扇出緩沖器與電平轉換器

深入探討德州儀器(TI)的LMK00105超低抖動LVCMOS扇出緩沖器與電平轉換器,了解其特性、應用及設計要點。 文件下載: lmk001

CDCLVD2106:高性能雙路 1:6 低附加抖動 LVDS 時鐘緩沖器的深度解析

CDCLVD2106:高性能雙路 1:6 低附加抖動 LVDS 時鐘緩沖器的深度解析 在電子設計領域,時鐘

CDCLVC11xx:高性能LVCMOS時鐘緩沖器的卓越之選

CDCLVC11xx:高性能LVCMOS時鐘緩沖器的卓越之選 在電子設計領域,時鐘緩沖器的性能對于系統的穩定性和可靠性起著至關重要的作用。今

深入剖析CDCLVC11xx:高性能時鐘緩沖器的卓越之選

深入剖析CDCLVC11xx:高性能時鐘緩沖器的卓越之選 在當今電子設備飛速發展的時代,高性能時鐘緩沖器對于確保設備穩定運行起到了至關重要的

德州儀器LMKDB11xx超低抖動時鐘緩沖器技術解析

德州儀器LMKDB11xx超低抖動時鐘緩沖器技術解析

評論