高速先生成員--周偉

之前高速先生發(fā)表過(guò)一篇《過(guò)孔STUB長(zhǎng),DDR信號(hào)“強(qiáng)”?》的文章,最近大家也都在問(wèn)DDR4或DDR5長(zhǎng)stub是否有影響,是否要背鉆等,然后正好有個(gè)項(xiàng)目在仿真DDR4地址信號(hào)的時(shí)候我們讓設(shè)計(jì)人員將走線移到stub較長(zhǎng)的層面,信號(hào)居然變好了,到底怎么回事呢,下面我們就來(lái)看看吧。

這個(gè)項(xiàng)目共16層,板厚2.9mm,主控芯片拖了3片DDR4顆粒,這些器件都分布在底層,數(shù)據(jù)速率(下文簡(jiǎn)稱數(shù)率)需要運(yùn)行到2400Mbps。如下圖所示為對(duì)應(yīng)的疊層信息。

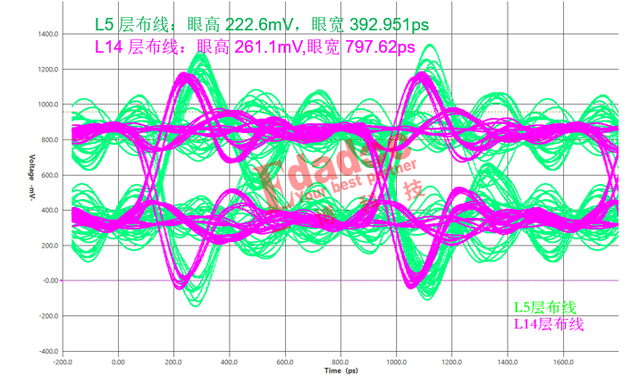

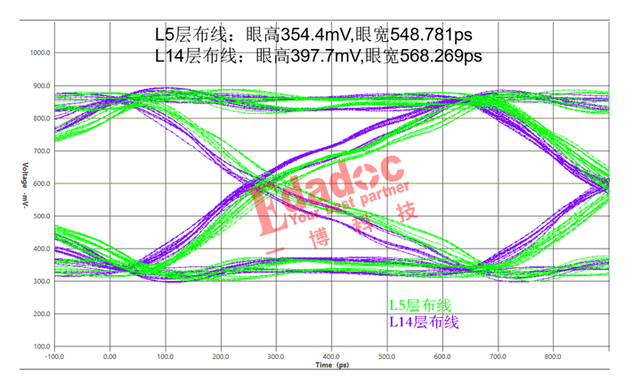

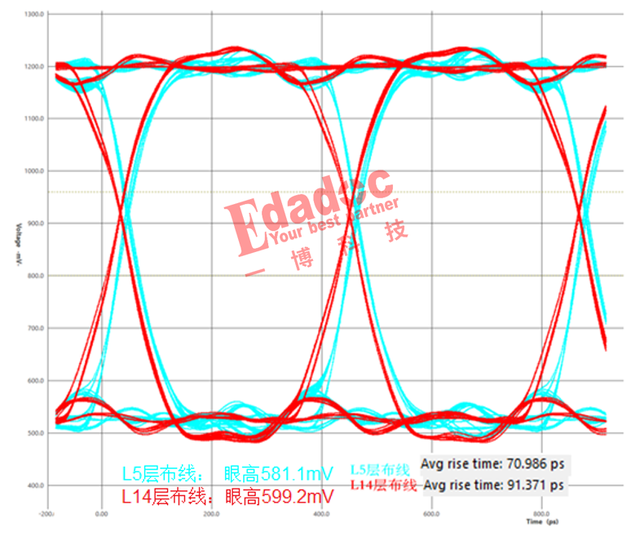

采用同樣的模型進(jìn)行仿真,發(fā)現(xiàn)主干在L14層的(Stub較長(zhǎng))信號(hào)質(zhì)量居然比L5層(Stub較短)的信號(hào)質(zhì)量更好,可見(jiàn)如下圖所示的第一個(gè)顆粒信號(hào)眼圖的對(duì)比。

圖1 數(shù)率2400Mbps時(shí)第一個(gè)顆粒處地址信號(hào)眼圖

上圖所示L5層的走線眼圖基本快閉合了,眼寬也比較小,這種眼圖的質(zhì)量可能會(huì)影響到信號(hào)的正常工作,會(huì)導(dǎo)致速率跑不上去或者會(huì)數(shù)據(jù)出錯(cuò),而L14層的走線眼圖就好很多,再優(yōu)化一下就會(huì)有一定的裕量,看起來(lái)過(guò)孔stub長(zhǎng)居然對(duì)DDR4的信號(hào)質(zhì)量有一定的改善作用。

這個(gè)原理其實(shí)在上篇文章中講到過(guò),我們?cè)賮?lái)重溫一下:過(guò)孔stub本質(zhì)是一種能量泄放的通道,越是高頻的能量受到的影響越大,因此,高速串行需要控制過(guò)孔stub盡量短,以避免能量損耗。但是,對(duì)于主控芯片的驅(qū)動(dòng)較強(qiáng),加上一驅(qū)多拓?fù)涞姆瓷涓菀自诮祟w粒處積累,所以近端顆粒的信號(hào)質(zhì)量就成了通道的瓶頸,增加近端顆粒的過(guò)孔stub長(zhǎng)度能夠很好的衰減高頻分量,使主芯片輸出的強(qiáng)度減弱,上升沿變緩,最終達(dá)到減少反射的目的,相應(yīng)的,信號(hào)質(zhì)量也得到了改善。這也印證了我們一直說(shuō)的:大部分信號(hào)完整性問(wèn)題歸根到底就是信號(hào)的上升沿太快造成的。

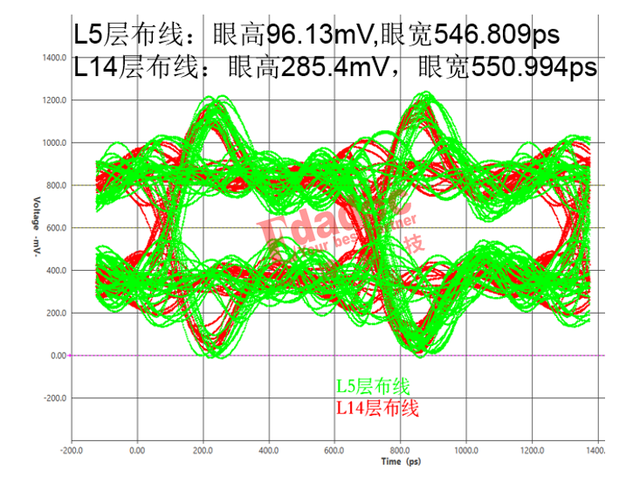

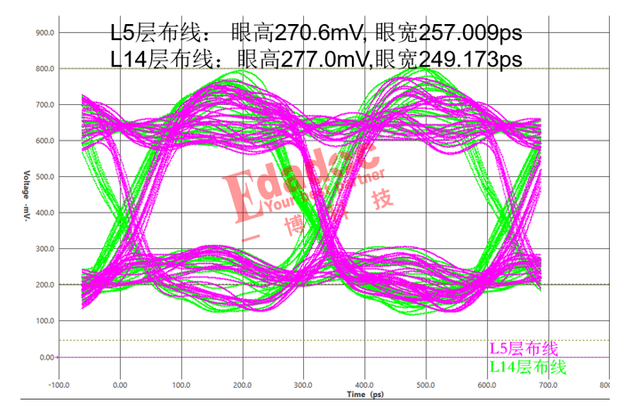

我們接下來(lái)看當(dāng)數(shù)據(jù)速率上升到3200Mbps時(shí)地址信號(hào)的眼圖會(huì)怎么樣,其他都不變,直接改變地址信號(hào)的速率到1600Mbps,如下是對(duì)應(yīng)的眼圖:

圖2 數(shù)率3200Mbps時(shí)第一個(gè)顆粒處地址信號(hào)眼圖

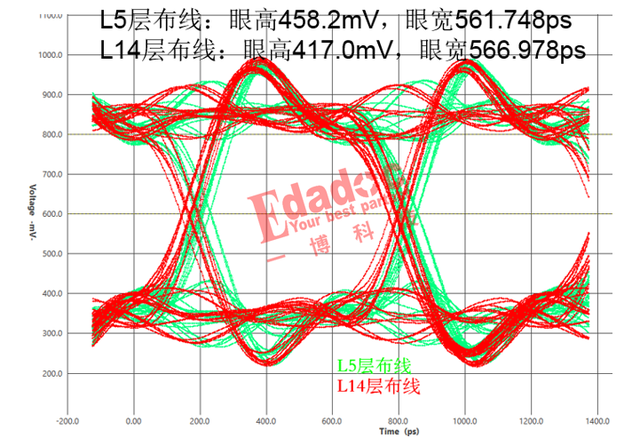

可以看到速率上升后整體的眼高反而變好了,同時(shí)趨勢(shì)還是一樣,比較長(zhǎng)的stub孔 L14層的走線比短stub孔L5層的走線信號(hào)質(zhì)量好。看起來(lái)在模型上升沿比較快(驅(qū)動(dòng)強(qiáng))的時(shí)候,地址信號(hào)保留一定的過(guò)孔stub確實(shí)會(huì)對(duì)信號(hào)質(zhì)量有一定的改善作用,接下來(lái)我們?cè)儆肵ilinx的fast slew rate模型來(lái)驗(yàn)證一下,保持同樣的拓?fù)洌瑢Ⅱ?qū)動(dòng)模型換成Xilinx的driver48_fast,其他不變的情況下,地址信號(hào)還是按照1600Mbps的速率仿真的結(jié)果如下所示。

圖3 數(shù)率3200Mbps時(shí)第一個(gè)顆粒處地址信號(hào)眼圖(xilinx_driver48_fast驅(qū)動(dòng))

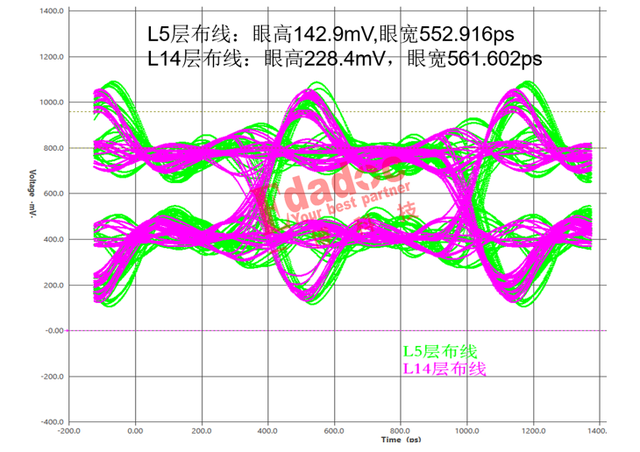

此時(shí)還是比較強(qiáng)的驅(qū)動(dòng),可以看到比較長(zhǎng)的stub孔 L14層的走線比短stub孔L5層的走線信號(hào)質(zhì)量好。如果換成不是那么快的比較正常的驅(qū)動(dòng)結(jié)果會(huì)怎么樣呢?下面我們把驅(qū)動(dòng)改成Xilinx的driver48_typical,其他條件不變,仿真出來(lái)的眼圖如下圖所示。

圖4 數(shù)率3200Mbps時(shí)第一個(gè)顆粒處地址信號(hào)眼圖(xilinx_driver48_typical驅(qū)動(dòng))

兩個(gè)眼圖肉眼看起來(lái)其實(shí)差不多,量測(cè)下來(lái)短stub孔的眼高稍微好點(diǎn),但長(zhǎng)stub孔的信號(hào)質(zhì)量也還不錯(cuò),可以滿足要求,這么看來(lái)在3200Mbps數(shù)據(jù)速率下,不管驅(qū)動(dòng)正常還是比較強(qiáng),長(zhǎng)stub過(guò)孔都有比較好的表現(xiàn),這樣是否就能說(shuō)明過(guò)孔stub比較長(zhǎng)其實(shí)對(duì)3200Mbps速率下的地址信號(hào)反而更好呢?大部分情況下看起來(lái)是這樣的,那如果這個(gè)信號(hào)本身的驅(qū)動(dòng)比較弱,此時(shí)長(zhǎng)stub過(guò)孔會(huì)將信號(hào)上升沿變得更緩,這樣對(duì)信號(hào)質(zhì)量是否有影響呢?接下來(lái)我們也通過(guò)仿真來(lái)驗(yàn)證下。

其他都不變的情況下將驅(qū)動(dòng)模型換成比較弱一點(diǎn)的ron80,再比較兩種情況在數(shù)據(jù)速率3200Mbps時(shí)的眼圖如下圖所示。

圖5 數(shù)率3200Mbps時(shí)第一個(gè)顆粒處地址信號(hào)眼圖(本案例_ron80驅(qū)動(dòng))

可以看到結(jié)論還是和上面差不多,這是由于此時(shí)這個(gè)模型的沿也不是很緩,相對(duì)于普通的弱驅(qū)其實(shí)也并不弱,那我們?cè)賮?lái)看看Xilinx的slow模式,這個(gè)可能更有代表性一點(diǎn),直接將驅(qū)動(dòng)模型換成Xilinx的driver48_slow,其他不變還是在3200Mbps數(shù)率下的仿真結(jié)果如下圖所示。

圖6 數(shù)率3200Mbps時(shí)第一個(gè)顆粒處地址信號(hào)眼圖(xilinx_driver48_slow驅(qū)動(dòng))

從仿真結(jié)果來(lái)看,還是過(guò)孔stub較長(zhǎng)的信號(hào)眼圖會(huì)好點(diǎn),看起來(lái)結(jié)論已經(jīng)比較明顯了,那就是3200Mbps數(shù)率下,過(guò)孔stub對(duì)地址信號(hào)的影響比較小,甚至?xí)盏粢徊糠址瓷湫盘?hào)使得信號(hào)質(zhì)量更好。再拓展一下,如果到了DDR5地址信號(hào)也有ODT了,結(jié)論還是不是這樣呢?都到門口了,我們接下來(lái)就最后再仿真看看如果地址按照3200Mbps結(jié)果會(huì)怎么樣。

拓?fù)溥€是不變,驅(qū)動(dòng)改為之前比較強(qiáng)一點(diǎn)的Ron48,顆粒模型換成DDR5,外部上拉端接去掉,地址信號(hào)按照3200Mbps速率仿真,結(jié)果如下圖所示。

圖7 數(shù)率6400Mbps時(shí)第一個(gè)顆粒處地址信號(hào)眼圖(Ron48驅(qū)動(dòng))

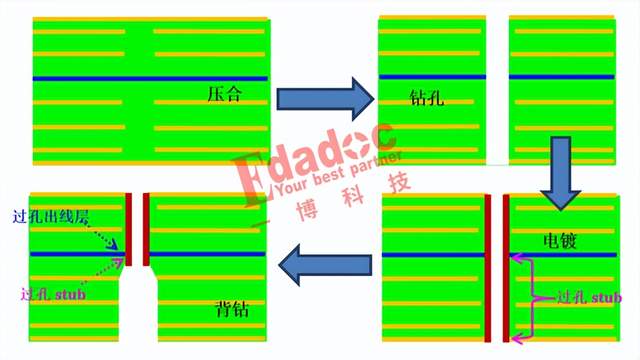

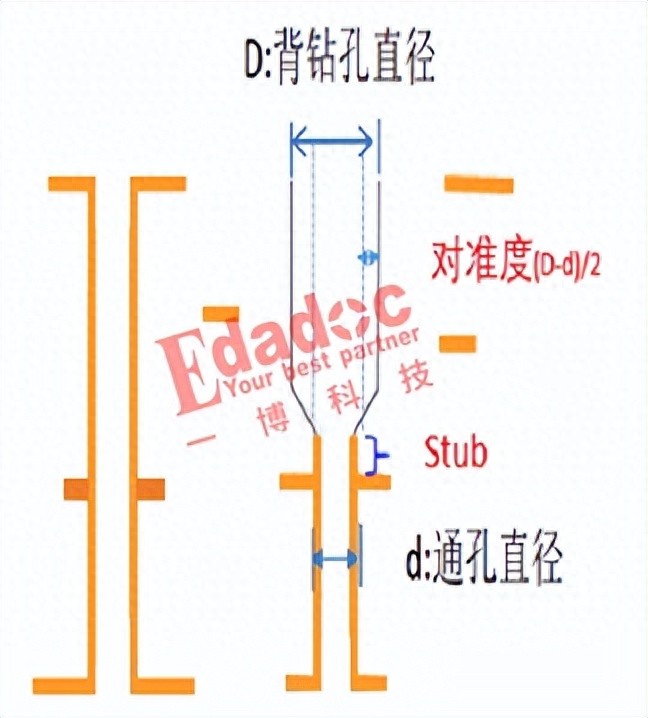

可以看到當(dāng)?shù)刂沸盘?hào)速率到3200Mbps時(shí)(數(shù)據(jù)率6400Mbps),長(zhǎng)過(guò)孔stub對(duì)地址信號(hào)的影響也還不是很大,這樣我們以后DDR4設(shè)計(jì)的時(shí)候就不用想著stub的影響了,也不用考慮地址信號(hào)長(zhǎng)stub要不要做背鉆了,甚至有時(shí)候還可以特意把地址信號(hào)走在長(zhǎng)過(guò)孔stub的層面。

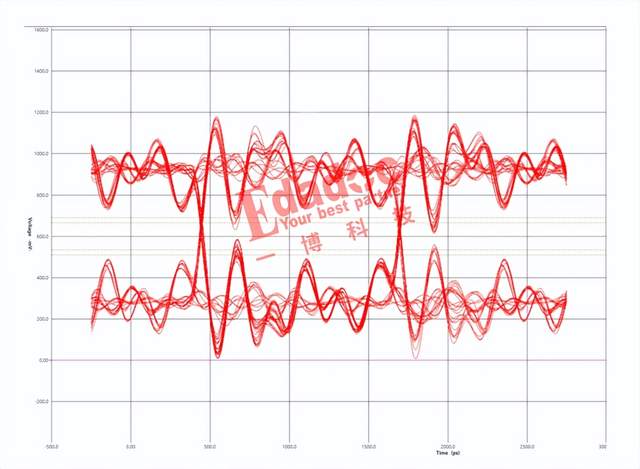

按照這個(gè)思路,我們正好把這個(gè)結(jié)論用在了一個(gè)一拖五的錯(cuò)位正反貼的DDR4項(xiàng)目上,而且最終驗(yàn)證也成功了。該項(xiàng)目板厚也是3mm共18層板,一開(kāi)始設(shè)計(jì)的時(shí)候采用常規(guī)的做法,盡量避開(kāi)長(zhǎng)過(guò)孔stub的層面,后面仿真的時(shí)候發(fā)現(xiàn)信號(hào)質(zhì)量整體不太好,尤其是第一片顆粒的眼圖比較小,信號(hào)反射嚴(yán)重,如下圖所示。

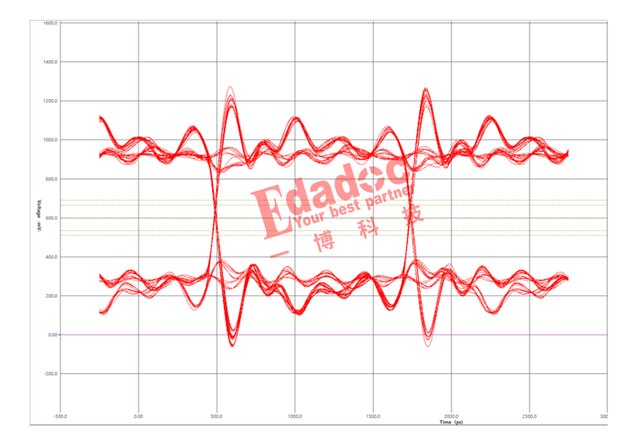

后面我們建議引入一定的過(guò)孔stub,把TOP層的顆粒,前面的走線換到L3層;BOT層的顆粒,前面的走線換到L16層,這樣顆粒前面的換層孔stub就比較長(zhǎng),然后再仿真得到如下比較好的眼圖。

有時(shí)候不得不覺(jué)得,這個(gè)世界就是這么神奇!尤其是DDRx的設(shè)計(jì)套路太多了,設(shè)計(jì)難度越來(lái)越大,不仿真還真不好保證能跑到那么高的速率。

關(guān)于一博:

一博科技成立于2003年3月,深圳創(chuàng)業(yè)板上市公司,股票代碼: 301366,專注于高速PCB設(shè)計(jì)、SI/PI仿真分析等技術(shù)服務(wù),并為研發(fā)樣機(jī)及批量生產(chǎn)提供高品質(zhì)、短交期的PCB制板與PCBA生產(chǎn)服務(wù)。致力于打造一流的硬件創(chuàng)新平臺(tái),加快電子產(chǎn)品的硬件創(chuàng)新進(jìn)程,提升產(chǎn)品質(zhì)量。

審核編輯 黃宇

-

PCB

+關(guān)注

關(guān)注

1文章

2325瀏覽量

13204

發(fā)布評(píng)論請(qǐng)先 登錄

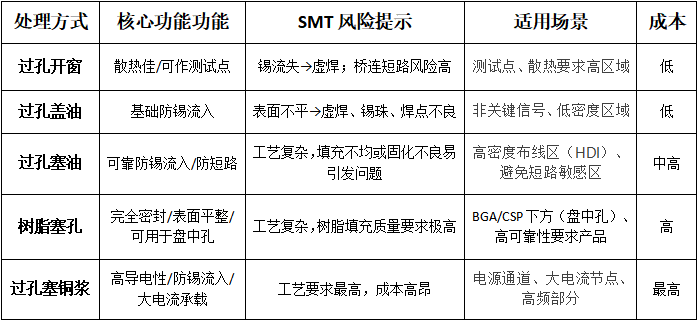

過(guò)孔焊盤,你真的了解嗎?PCB設(shè)計(jì)中的“隱形殺手”揭秘

高速PCB諧振威力,不容小覷

隔離地過(guò)孔要放哪里,才能最有效減少高速信號(hào)過(guò)孔串?dāng)_?

高速PCB板DDR5數(shù)據(jù)信號(hào)的長(zhǎng)STUB要背鉆嗎?

高速PCB板DDR5數(shù)據(jù)信號(hào)的長(zhǎng)STUB要背鉆嗎?

PCB過(guò)孔STUB對(duì)DDRX地址信號(hào)的影響

PCB為啥現(xiàn)在行業(yè)越來(lái)越流行“淺背鉆”了?

PCB為啥現(xiàn)在行業(yè)越來(lái)越流行“淺背鉆”了?

毫米之間定成敗:PCB背鉆深度設(shè)計(jì)與生產(chǎn)如何精準(zhǔn)把控

別讓孔偏毀了信號(hào)!PCB 背鉆的 XY 精準(zhǔn)度如何做到分毫不差?

PCB仿真結(jié)果天下無(wú)敵,板廠加工讓你一敗涂地

PCB設(shè)計(jì)中過(guò)孔為什么要錯(cuò)開(kāi)焊盤位置?

過(guò)孔處理:SMT訂單中的隱形裁判

Allegro Skill布線功能-添加差分過(guò)孔禁布區(qū)

高速電路中的過(guò)孔效應(yīng)與設(shè)計(jì)

PCB過(guò)孔STUB對(duì)DDRX地址信號(hào)的影響

PCB過(guò)孔STUB對(duì)DDRX地址信號(hào)的影響

評(píng)論