作者:Anne Meixner

來源:https://semiengineering.com/progress-in-wafer-and-package-level-defect-inspection/

在生產環境中,實現抽樣的技術與對更多計量及檢測數據的需求恰好同步發展,可滿足半導體行業最新、最復雜制造工藝的需求。

在晶圓制造和封裝組裝環節,長期以來,工程團隊一直依賴成像工具在特定工藝后測量關鍵特征并檢測缺陷。這些工具采用不同的發射源(光學、X 射線和電子束),對工藝開發、良率提升及生產監控至關重要。

與此同時,檢測細微缺陷的需求卻在不斷增加。先進 CMOS 設計與工藝的復雜性導致特征尺寸更小,設計布局敏感性更高。同樣,2.5D 等先進封裝工藝采用更高的互連密度,這進而要求超過 100 萬個凸點 / 柱體具備共面性。

一、光學系統的性能瓶頸與檢測需求的升級

在量產場景中,光學系統仍是絕對主力:不僅吞吐量最高,且數十年來,其測量分辨率始終能匹配 “關鍵尺寸” 與 “目標缺陷尺寸” 的演進需求。

但這一優勢正遭遇挑戰:在≤14nm 的先進 CMOS 邏輯節點,以及凸點 / 柱體間距≤50μm 的封裝環節,光學系統的性能已逐漸 “力不從心”。

與此同時,“檢測細微缺陷” 的需求卻在持續升級:

先進CMOS 的設計與工藝復雜度提升,導致芯片特征尺寸更小、設計布局對缺陷的敏感性更高;

2.5D等先進封裝工藝采用更高互連密度,要求超過100 萬個凸點 / 柱體實現“共面性”(即高度一致性)。

這帶來了核心成像難題:掃描區域與測量分辨率的比例急劇擴大。例如:300mm晶圓的 “掃描區域 - 分辨率比” 約為10?:1;50×50mm 封裝基板的這一比例約為10?:1。若再疊加“量產場景需支持 100% 抽樣” 的吞吐量要求,成像難度將進一步加劇。

二、技術突破:如何平衡吞吐量與檢測精度?

幸運的是,依托工程創新、計算技術進步與 CCD 探測器升級,設備廠商已開發出能應對這一挑戰的系統 —— 不僅能識別缺陷、測量關鍵尺寸(支撐工藝開發與良率提升),還優化了設備調試流程,實現了 “近實時工藝控制”。

但需注意:檢測結果仍受 “抽樣率” 影響——這本質是工廠管理層需權衡的 “時間 / 成本” 與 “良率 / 可靠性” 關系。

“檢測不只是為了‘學習良率’,”普迪飛VPIndranil De指出,“即便是量產流程,晶圓廠也需提前規劃檢測預算的分配策略:檢測不僅覆蓋晶體管、Metal-1(第一層金屬)、Metal-2(第二層金屬),而是每一層金屬都要檢測,且不同層的檢測頻率不同。團隊能夠根據“可能出現工藝偏差的環節”,以最高效的方式分配投入。”

業界有個共識:“數據獲取越早越好”—— 這進一步推高了對 “成像衍生數據” 的需求。但關鍵在于兩點:

1.數據需是“有效數據”:能在工程師可干預的時間窗口內提供決策支撐;

2.成本需可控:CMOS晶圓制造周期至少 3 個月,先進封裝至少 1 個月,過高的檢測時間 / 成本會直接影響量產效率。

因此,評估檢測方案的投資回報率(ROI)時,必須納入 “未檢出缺陷導致終端故障” 的風險 —— 而這一風險取決于芯片的應用場景:對于數據中心、汽車、軍事 / 航空航天等 “任務關鍵型 / 安全關鍵型領域”,缺陷流到終端市場的風險極高;在這類場景中,100% 檢測與計量不再是 “額外成本”,而是 “合理的風險保障措施”。

圖 1:故障檢測越晚,風險及關聯成本越高 來源:Bruker

盡管如此,推動工程師采納 “100% 檢測” 仍需更多依據 —— 畢竟其成本居高不下。“質量因素固然重要,但企業最終需實現盈利,” Bruker應用與產品管理總監Frank Chen解釋道,“因此,必須從商業角度說明:100% 檢測的價值究竟在哪里?”

Frank Chen以 “采用Bruker X200 X 射線檢測系統對 CPU 先進封裝進行 100% 檢測” 為例,提供了一個假設性 ROI 計算模型(見圖 2)。

圖 2:基于 4156 個產品單元的 “終端市場故障成本” 與 “出廠前故障成本” 對比 來源:Bruker

三、更高標準:成像系統的核心技術要求

“高吞吐量 + 高分辨率” 本身已對成像系統提出嚴苛要求,而 “支持 100% 抽樣” 則進一步拉高了技術門檻。

要滿足這一要求,工程團隊需從三方面突破:

借力探測器技術進步;

搭配不同類型的發射源;

構建高效的計算分析方法。

其中關鍵在于 “檢測目標的針對性”:目標越具體,成像系統的設計就能越高效、越經濟。

無論是光學、X 射線還是電子束成像,核心組成部分其實一致:

運動系統(控制檢測位置移動);

“照明” 源(光學 / X 射線 / 電子束);

圖像采集模塊;

可選多物鏡設計(調節放大倍數);

計算資源(通過算法分析檢測數據)。

“歸根結底,核心是‘速度’,” Nordson Test & Inspection計算機視覺工程經理John Hoffman強調,“決定速度的有兩大因素:

第一是‘移動速度’—— 從一個檢測點到下一個的耗時,這取決于運動系統性能,也與‘待移動的傳感器 / 晶圓重量’‘所需穩定性’‘停止速度’直接相關;

第二是‘數據采集速度’—— 需拍攝多少張圖像、需要多少光源、相機速度有多快、需多少種照明方案。我們團隊的核心任務是開發信號處理算法:算法速度必須超過‘移動時間 + 數據采集時間’之和。我們希望瓶頸來自‘物理限制’(如運動系統性能),而非‘計算限制’。”

所謂 “物理限制”,主要源于三方面:

運動系統的實際性能;

所選成像方式的物理原理(如光學反射、X 射線穿透性);

期望的視場(FOV,即發射源覆蓋的區域)與測量分辨率。

其中,視場指投影光 / X 射線 / 電子束覆蓋的區域;探測器的像素數量決定了每個像素覆蓋的面積;模數轉換(A/D 轉換)則決定了將檢測亮度轉換為數字編碼的數據位數。

成像系統主要分為 “連續掃描型” 與 “啟停型”:在光學領域,連續掃描一直是主流。

“基于光學圖像的檢測技術,是高產量制造(HVM)場景中‘前端晶圓廠’與‘后端封裝廠’的主流選擇 —— 因其抽樣率高,能滿足特定工藝環節的 100% 檢測需求,” Onto Innovation產品營銷經理彭 Nathan Peng表示,“要實現晶圓 / 面板的 100% 全抽樣檢測,連續掃描是更優方案。具體速率取決于分辨率或缺陷尺寸:以 300mm 晶圓為例,若像素分辨率在 10μm 級別,吞吐量通常可達 100 片 / 小時(WPH)。”

CCD 相機像素密度的躍升,為速度與分辨率的雙重提升提供了可能:Hoffman提到,諾信首款 3D 傳感器采用 500 萬像素相機,8 年后已升級為 8500 萬像素 —— 數據量提升 20 倍。這一進步讓 “啟停型系統” 實現突破:不僅速度能與連續掃描型媲美,分辨率還更具優勢。例如 “條紋投影輪廓測量法”,就能充分借力這一硬件升級。

“對于光學成像,‘動態掃描相位輪廓測量系統’在實現客戶所需精度時,靈活性非常有限,” Hoffman補充道,“而‘移動 - 停止’模式能顯著提升精度與重復性:我們采用的數字光投影儀(DLP)具備高靈活性,可微調圖像采集過程,最大限度從每張圖像中提取信息;同時通過‘減少圖像數量、提升單圖利用率’加快數據采集。我們的系統還搭載多臺 DLP 與相機,能實現‘一臺投影、多臺同步采集’。”

這一 “速度與分辨率的權衡”,在 X 射線系統的對比中尤為明顯。“傳統失效分析 X 射線系統,為實現 1μm 特征尺寸的高分辨率,視場僅為幾平方毫米 —— 這是 103 量級的差距,” Frank Chen解釋道,“快速系統掃描一次需 15 分鐘,慢速系統則需數小時。但先進封裝需要的是 10?量級的‘視場 - 分辨率平衡’:高吞吐量工具雖能覆蓋大視場,卻會犧牲分辨率,無法滿足先進封裝需求 —— 這正是我們的技術要填補的空白。”

圖 3:不同 X 射線系統在 “每小時晶圓檢測量”“視場(FOV)”“像素分辨率” 上的對比 來源:Bruker

四、電子束檢測:從實驗室走向量產的突破

電子束檢測的優勢在于 “高精度”—— 測量精度可達 1nm 級別,非常適合檢測先進 CMOS 邏輯 / 存儲節點中的微小缺陷。

典型電子束系統采用“光柵掃描法”,但其測量時間限制需從物理原理理解:“電子束柱體有特定的光斑寬度與對應電流 —— 電流代表測量時段內撞擊目標區域的電子數量,”普迪飛的 De 解釋道,“電流越小,單個像素(由光斑寬度決定)的測量耗時越長。例如:10×10μm 的區域若劃分為 10×10nm 的像素,每個像素測量需 100 納秒;對 100 萬個像素的測量,總耗時約 0.1 秒。”

當前最先進的電子束系統(單柱 / 多柱),每小時僅能對幾百平方毫米區域進行光柵掃描 —— 據此推算,掃描 300mm 全晶圓需約 237 小時。因此,電子束工具長期局限于 “研發” 與 “失效分析實驗室”。

突破這一局限的關鍵,在于 “精準定位檢測區域”。“聚焦特定區域,能大幅提升吞吐量,” De 表示,“我們將掃描方式從‘光柵掃描’(逐點覆蓋)改為‘點掃描’(直接跳轉至目標位置)—— 這是核心突破。”

電子束檢測:攻克5nm以下先進節點關鍵缺陷的利器

100% 檢測的優勢

借助這些兼具高吞吐量和高分辨率的新型成像系統,芯片制造商可在以往無法實現的場景中考慮采用 100% 抽樣檢測。當工程師聚焦于 “關鍵缺陷”時,檢測系統可針對這類缺陷進行優化,從而以經濟高效的方式支持 100% 抽樣。例如,當前行業對晶圓邊緣和背面檢測的關注度日益提升。

“當客戶轉向更先進的工藝節點時,會加強制造過程中的質量控制,檢測范圍從晶圓正面擴展到邊緣和背面,” Nathan Peng表示,“通過我們的邊緣和背面檢測模塊,可識別晶圓邊緣的崩裂、裂紋以及背面的劃痕 —— 這些缺陷可能會擴散或轉移到芯片區域,最終導致良率損失。我們觀察到的趨勢是,客戶在質量保證(QA)環節對晶圓采用 100% 邊緣 / 背面檢測。”

另一個典型場景是 “隱藏缺陷檢測”。數十年來,第一層金屬互連的自對準硅化物(salicide)裂紋,以及接觸孔 / 通孔中的部分空洞,一直是影響良率和失效分析的難題。這些缺陷帶來的電學影響可能表現為時序延遲,進而導致系統故障。在晶圓工藝早期檢測出這些缺陷,有助于改進工藝,并在晶圓測試前篩選出不良芯片。

電子束成像結合電壓對比技術已成功實現此類缺陷的識別,但如前所述,光柵掃描中每個像素的測量時間使其難以應用于量產環境。然而,通過縮小檢測區域范圍,采用點掃描方式,可顯著提高吞吐量。

我們用 “街道交通” 類比這一邏輯:“假設你在固定寬度的街道上行駛,速度有限;即便拓寬街道或提速,單位時間內的‘通行量’(類比電子數量)仍有上限。但如果不覆蓋整條街道,只關注 2% 的關鍵路段(類比目標檢測區域),就能顯著提升‘行駛效率’(檢測速度)。”

圖 4:光柵掃描法(上)與點掃描法(下)的對比 來源:PDF Solutions

借助這一思路,普迪飛的電子束系統可在 2-4 小時內,完成 300mm 晶圓上 “數十億個選定特征” 的掃描 —— 這為量產場景的應用提供了可能。但前提是 “精準定義目標檢測區域”:需通過詳細的 “設計敏感性分析”,結合每一層的布局敏感性、信號與電源互連布線信息(例如:僅關注 3 個冗余通孔的布線,忽略 10 個冗余通孔的布線)。

五、2.5D 封裝中的檢測與計量難點

高性能計算需求推動 2.5D 封裝技術快速發展,也讓 “芯片(die)與基板的鍵合密度” 大幅飆升。如今,產品的功能與可靠性,高度依賴近 100 萬個 “鍵合焊料凸點” 或 “銅柱”—— 其中銅柱的尺寸 / 間距已縮小至 25μm,銅焊盤未來還將進一步縮小至 10μm。

這一趨勢倒逼兩大檢測需求:

凸點 / 柱體形成過程中,需100% 檢測與計量;

鍵合后,需檢測冶金完整性(如是否存在裂紋、空洞)。

尤其關鍵的是 “凸點 / 柱體的共面性”:數百萬個凸點的高度一致性,直接影響封裝翹曲與鍵合質量 —— 因此,工藝工程師需重點監控 “影響共面性的工藝指標”。

圖 5:銅柱凸點工藝流程 傳統凸點高度測量在 “光刻膠剝離后” 進行;a)凸點形成前;b)凸點電鍍;c)光刻膠剝離;d)UBM 蝕刻;e)焊料回流 來源:諾信測試與檢測公司

值得注意的是,工程團隊更關注 “工藝中期” 而非 “末期” 的計量數據。“Hoffman曾以為客戶只會關注銅柱的最終檢測 —— 即‘是否合格’,” Hoffman坦言,“但實際需求是‘光刻膠剝離前’的原位測量:在 10-12 步制造流程的中期,同步測量‘光刻膠厚度’(決定銅柱最終高度)與‘當前銅柱高度’。”

光學測量在此場景中面臨兩大挑戰:

銅的光澤表面會產生強反射;

多層結構(光刻膠+ 銅)的反射信號會相互干擾。

要解決這一問題,需采用 “條紋投影輪廓測量法”,并搭配復雜的信號處理算法 —— 通過算法區分不同反射信號、融合多張圖像,最終實現精準測量。

圖 6:光刻膠剝離前的凸點高度測量原理 借助光刻膠折射的光線,先確定光刻膠厚度,再計算晶圓表面上方的凸點高度 來源:Nordson Test & Inspection

在鍵合后質量檢測中,傳統量產場景僅能實現 “邊緣光學檢測”,而 X 射線系統可 “穿透封裝” 觀察內部鍵合狀態:在具備合適像素分辨率的前提下,能識別 “焊料頸縮”“頭枕缺陷”“部分裂紋” 等典型問題。

此外,“像素信號的量化水平” 也至關重要 —— 直接影響圖像可解釋性。例如,將動態范圍從 8 位提升至 16 位,能顯著提升 “缺陷識別精度” 與 “凸點高度測量準確性”;而鍵合后的凸點高度數據,還可用于評估 “芯片與基板的翹曲程度”。

圖 7:8 位與 16 位動態范圍在金屬結構測量中的差異 來源:Bruker

圖 8:X 射線系統對鍵合后凸點高度的評估結果 來源:Bruker

六、結論

管控先進 CMOS 與 2.5D 封裝工藝,核心在于 “更多、更精準的檢測與計量數據”。在部分場景中,100% 抽樣檢測對良率與可靠性的提升效果顯著,但 “改變現有制造流程” 需克服不小的阻力 —— 尤其是新增檢測工具時,成本始終是決策者的核心考量。

“我們的所有優化,最終都指向‘提升速度’—— 這是客戶的核心需求,” Hoffman總結道,“若能將檢測吞吐量提升一倍,客戶實現 100% 抽樣的成本就能降低一半。”

-

半導體

+關注

關注

339文章

30892瀏覽量

265152 -

光學

+關注

關注

4文章

875瀏覽量

38156 -

電子束

+關注

關注

2文章

134瀏覽量

14045

發布評論請先 登錄

功率放大器在電子束金屬3D打印中的應用

BW-4022A半導體分立器件綜合測試平臺---精準洞察,卓越測量

極細同軸線束如何解決AI設備的高速信號傳輸難題?

國產首臺28 納米關鍵尺寸電子束量測量產設備出機

電子束檢測:攻克5nm以下先進節點關鍵缺陷的利器

今日看點丨全國首臺國產商業電子束光刻機問世;智元機器人發布行業首個機器人世界模型開源平臺

CCLINK IE 與 PROFINET 無法互通?99% 的工程師都靠這招破局

三星在4nm邏輯芯片上實現40%以上的測試良率

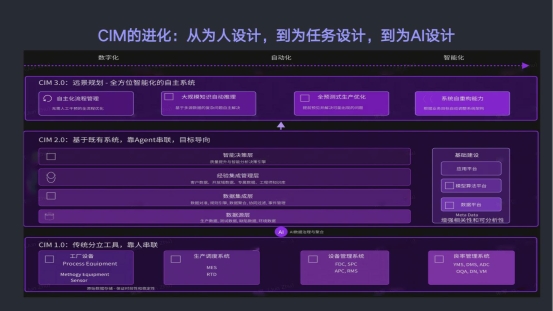

半導體制造AI大腦:從CIM1.0到CIM 3.0的中國式躍遷

APEX經濟型減速器——助力TETA電子束焊機高性價比焊接

從光學 “乏力” 到電子束 “開掛”!半導體缺陷檢測:細抓1nm 瑕疵,量產難題靠這招破局!

從光學 “乏力” 到電子束 “開掛”!半導體缺陷檢測:細抓1nm 瑕疵,量產難題靠這招破局!

評論