文章來源:老虎說芯

原文作者:老虎說芯

本文主要講述數字芯片的常用術語。

核心概念與目標

PPA (Power, Performance, Area)

解釋: 這是數字芯片設計永恒的“鐵三角”。Power指芯片功耗,越低越好;Performance通常指芯片能跑多快(頻率),越高越好;Area指芯片的面積,越小成本越低。

行家視角: 這三者是互相矛盾、需要權衡的。比如,為了提高性能,你可能需要插入更多的buffer,這會增加面積和功耗。工程師很大程度上就是根據項目需求,在PPA之間找到最佳的平衡點。這是我們一切工作的出發點和最終目標。

Foundry / Fab(晶圓廠)

解釋: 制造芯片的工廠。比如臺積電(TSMC)、三星(Samsung)、中芯國際(SMIC)。

行家視角: 物理設計的所有工作,最終都是為了生成一個能讓Foundry看懂并制造出來的版圖文件。我們必須嚴格遵守他們提供的規則。

Process Node / Tech Node (工藝節點)

解釋: 指的是芯片制造工藝的水平,比如28nm, 16nm, 7nm, 5nm。數字越小,代表晶體管可以做得越小,單位面積能集成的晶體管就越多。

行家視角: 對物理設計工程師來說,節點越先進,意味著設計規則(DRC)越復雜,線間距(spacing)越小,串擾(crosstalk)和電壓降(IR drop)等問題越嚴重,設計挑戰呈指數級增長。

PDK (Process Design Kit)

解釋: Foundry提供給我們設計公司的一套數據包,是連接設計和制造的橋梁。

行家視角: PDK就是物理設計工程師的“法律和字典”。它里面包含了標準單元庫(Standard Cell Library)、技術文件(Tech File, 如.tf,.lef)、設計規則文件(DRC/LVS Rule Deck)等等。

Tapeout / TO (流片)

解釋: 設計完成的最后一步,指將最終的版圖數據(通常是GDSII或OASIS格式)提交給Foundry進行生產。

行家視角: Tapeout是一個里程碑,但也意味著巨大的成本投入。一旦Tapeout,再發現問題就晚了,損失可能是數百萬甚至上千萬美元。所以我們之前的每一步驗證都必須做到極致。

設計流程中的關鍵術語

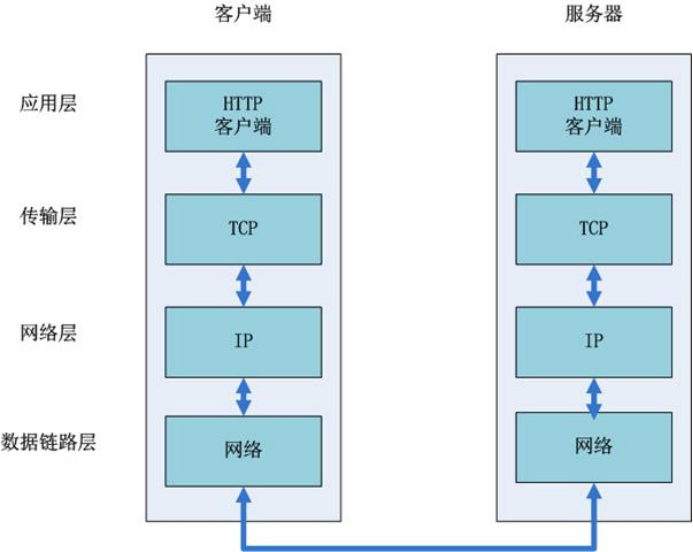

RTL (Register Transfer Level)

解釋: 硬件描述語言(如Verilog, VHDL)寫成的代碼,描述了芯片的邏輯功能,是前端設計的產物,也是我們物理設計的起點。

行家視角: RTL的質量直接決定了PPA的上限。一個“爛”的RTL,神仙也難做出好的物理實現。我們會經常和前端設計師溝通,建議他們優化RTL結構,比如打斷長邏輯鏈、優化狀態機等。

Synthesis (綜合)

解釋: 使用EDA工具(如Synopsys的Fusion Compiler/DC, Cadence的Genus)將RTL代碼“翻譯”成由邏輯門(與門、或門、觸發器等標準單元)組成的門級網表(Gate-level Netlist)。

行家視角: 綜合是連接邏輯設計和物理設計的關鍵一步。綜合的好壞直接影響初始的時序和面積。這一步需要高質量的約束文件(SDC)作為指導。

SDC (Synopsys Design Constraints)

解釋: 一個時序約束文件,是設計的“性能合同”。它定義了時鐘頻率、輸入/輸出延遲、設計中的偽路徑(false path)等。

行家視角: SDC是整個物理設計流程的指揮棒。如果SDC錯了,那么后面所有的時序優化、收斂工作都是在“緣木求魚”。檢查和確認SDC的質量,是我們開始P&R前最重要的任務之一。

Floorplan (布局規劃)

解釋:在芯片上“畫地盤”。決定芯片的整體形狀,放置大的模塊(Macro,如SRAM、IP核),規劃電源網絡(Power Grid),以及確定IO引腳的位置。

行家視角: Floorplan是藝術和經驗的結合。一個好的Floorplan決定了項目的成敗。它需要預判后續布局布線的擁塞(Congestion)和時序熱點(Timing Hotspot)。一個糟糕的Floorplan,后面再怎么努力都難以挽救。

CTS (Clock Tree Synthesis - 時鐘樹綜合)

解釋: 生成一個“樹狀”網絡,將時鐘信號從時鐘源(Clock Source)精準、同步地傳遞到芯片里每一個需要時鐘的觸發器(Flip-flop)。

行家視角: CTS是整個設計的“心臟起搏器”。我們的目標是控制Skew(時鐘到達不同觸發器的時間差)和Latency(時鐘從源頭到終點的總延遲)。先進工藝下,我們還會設計復雜的Mesh Clock或Multi-source CTS來獲得更好的性能。

Routing (布線)

解釋: 用金屬導線將芯片上所有的標準單元和宏單元根據網表連接起來。分為全局布線(Global Routing)和詳細布線(Detail Routing)。

行家視角: 布線不僅僅是連線,更要考慮**SI (Signal Integrity)**問題,尤其是串擾(Crosstalk)。在先進節點,我們會通過加屏蔽線(Shielding)、調整間距等手段來避免信號間互相干擾。

驗證與簽核(Signoff)

STA (Static Timing Analysis - 靜態時序分析)

解釋: 在不運行仿真(Simulation)的情況下,通過計算邏輯路徑的延遲,來檢查設計是否滿足SDC中定義的時序要求。是性能簽核的核心。

行家視角: 我們每天都在跟STA報告打交道。主要修復兩種違例(Violation):Setup Violation(信號太慢,下一拍來臨前數據沒準備好)和Hold Violation(信號太快,當前拍還沒結束數據就變了)。工具如PrimeTime (PT)是行業標準。

DRC (Design Rule Check - 設計規則檢查)

解釋: 檢查版圖是否滿足Foundry制定的所有物理制造規則。比如最小線寬、最小間距等。

行家視角: DRC必須100%干凈(clean),一個DRC錯誤都不能留。這直接關系到芯片能否被制造出來。我們會用Calibre或ICV這樣的工具來跑DRC檢查。

LVS (Layout Versus Schematic - 版圖與電路圖對比)

解釋: 對比最終的物理版圖和最初的門級網表,確保兩者在電氣連接上是完全一致的。

行家視角: LVS同樣必須100%干凈。LVS不通過,意味著我們做的物理版圖和邏輯設計的功能不符,這是致命錯誤。

Signoff (簽核)

解釋: 在Tapeout之前,對設計進行一系列最終、最嚴格的檢查和確認的過程。

行家視角: Signoff不是一個動作,而是一個狀態。它意味著我們已經完成了所有必要的分析和驗證(STA, DRC, LVS, IR Drop, EM等),并對結果負責,確認設計可以送去生產了。這背后是巨大的責任和壓力。

這些術語構成了我們日常工作的基本框架。先理解它們各自的含義,然后在實際項目中去體會它們是如何相互關聯、相互影響的。

-

晶圓

+關注

關注

53文章

5429瀏覽量

132448 -

RTL

+關注

關注

1文章

395瀏覽量

62768 -

數字芯片

+關注

關注

1文章

120瀏覽量

19092

原文標題:一文了解數字芯片常用術語和行話

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

硬件工程師必備!晶振術語中英文對照速查表,收藏這一篇就夠了

宏展科技北京淺談JEDEC半導體可靠度測試與規范

SMT貼片加工必備術語手冊:49個常用名詞及其詳細定義

機器視覺系統中光源的相關行業術語解讀

掌握數字設計基礎:邁向芯片設計的第一步

通俗易懂的晶振專業術語

電源管理芯片常見術語

IEC 62353中常用的術語和定義

技術干貨 | 功能安全術語的暗黑森林

常用的錄音芯片型號有哪些

淺談電池管理系統芯片

芯片前端設計中常用的軟件和工具

如果要使用數字信號隔離芯片將AD7606對數字系統隔離,應該如何鋪地?

想快速掌握電路電子術語?這些關鍵名詞別錯過!(附:基礎詞匯電子版)

探索物聯網專業術語:開啟智能互聯世界的鑰匙

淺談數字芯片的常用術語

淺談數字芯片的常用術語

評論