UCIe協(xié)議誕生背景

過去幾十年,摩爾定律一直是半導體行業(yè)發(fā)展的核心驅(qū)動力,芯片上晶體管數(shù)量每18-24個月翻倍,性能隨之大幅提升。但近年來這一定律明顯放緩,芯片制程向7nm、5nm甚至3nm推進時,技術(shù)難度呈指數(shù)級增長,研發(fā)成本飆升,且物理極限日益逼近,傳統(tǒng)通過提升制程提高性能的路徑愈發(fā)艱難。

為應對這一困境,Chiplet技術(shù)應運而生。它將大型芯片分解為多個小型芯粒,各芯粒可按功能需求采用最適配的工藝制造,既能提高良率、降低流片成本,又能增強設計靈活性。不過在發(fā)展初期,由于缺乏統(tǒng)一互連標準,不同廠商的芯粒無法兼容互通,每次設計都需重新開發(fā)互連方案,嚴重制約了Chiplet技術(shù)的規(guī)模化應用。

正是在這一背景下,UCIe(通用芯粒高速互連標準)協(xié)議應運而生。其核心目標是建立開放的Die-to-Die互連標準,打破廠商間的技術(shù)壁壘,實現(xiàn)不同功能芯粒的靈活組合。2022年3月,英特爾、AMD、ARM、臺積電等十家行業(yè)巨頭聯(lián)合推出UCIe并成立聯(lián)盟,這一舉措為Chiplet技術(shù)提供了標準化支撐,解決了互聯(lián)互通的關(guān)鍵難題,正式開啟了Chiplet技術(shù)標準化發(fā)展的新階段,也為半導體行業(yè)突破摩爾定律限制提供了新路徑。

UCIe協(xié)議原理

分層協(xié)議架構(gòu)

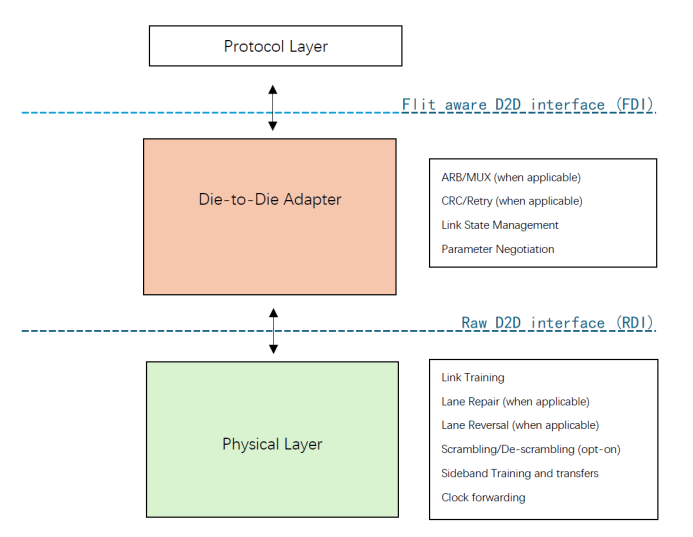

UCIe協(xié)議是一種分層協(xié)議,主要分為PHY 層、Adapter層和Protocol層,各層之間通過標準接口連接,PHY層和Adapter層之間接口為RDI(Raw Die - to - Die Interface),Adapter層和Protocol層之間接口為FDI(Flit-Aware Die-to-Die Interface)。這種分層架構(gòu)使得各層功能明確,各司其職,便于協(xié)議的通用和復用。

UCIe接口架構(gòu)示意圖

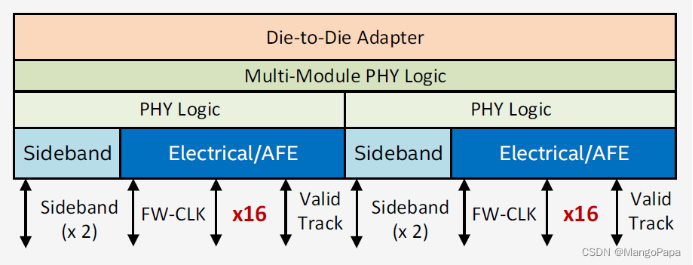

·PHY層:負責物理信號的傳輸,包括電氣物理層和邏輯物理層。電氣物理層方面,UCIe支持Standard及Advanced Package兩種封裝形式,支持低功耗模式,單Lane支持的傳輸速率有4,8,12,16,24,32 GT/s。邏輯物理層主要負責UCIe鏈路的初始化及鏈路訓練,將Adapter發(fā)來的數(shù)據(jù)分發(fā)到各條Lane上、進行Lane序重排、壞Lane修復及時鐘校正等工作。例如,數(shù)據(jù)包以Byte形式發(fā)出,一個Byte占用一個Lane使用4個clk傳輸,Main_band采用DDR的雙沿采樣。UCIe單個Adapter可對接1、2或4個物理層Module。配置為2個Module的示意圖如圖所示。

Two module configuration for standard package

(圖源:【UCIe】初識 UCIe-CSDN博客)

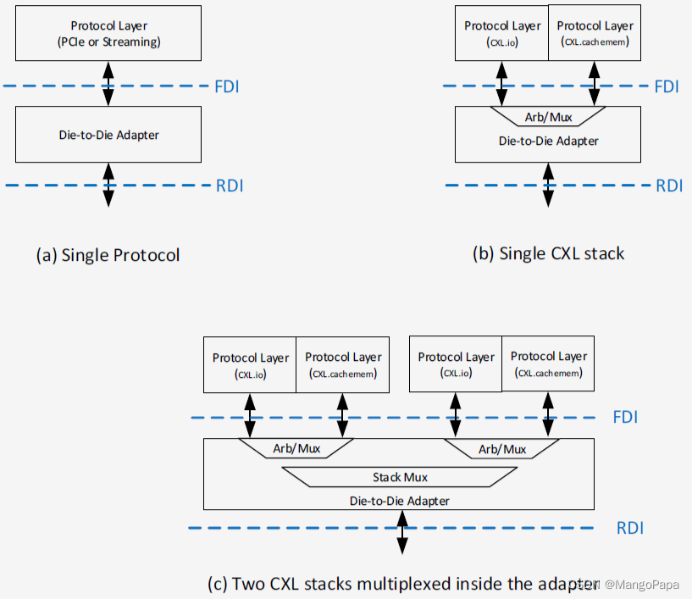

·Adapter層:主要功能包括CRC(循環(huán)冗余校驗)、FEC(前向糾錯)、Retry(重傳)等,以確保數(shù)據(jù)可靠傳輸。當協(xié)議層發(fā)送64B Flit數(shù)據(jù)時,會在前加上2B hdr(Protocol ID, Stack ID)和后面加上2B CRC值;對于 256B Flit需要額外增加2B CRC。此外,它還通過Sideband消息跟對端的UCIe設備進行協(xié)商,確定采用的協(xié)議及一些參數(shù),并且支持多個協(xié)議層架在統(tǒng)一Adapter上,通過Adapter中的Arb/Mux實現(xiàn)多個協(xié)議層的分時復用。

UCIe 與Adapter的連接

(圖源:【UCIe】初識 UCIe-CSDN博客)

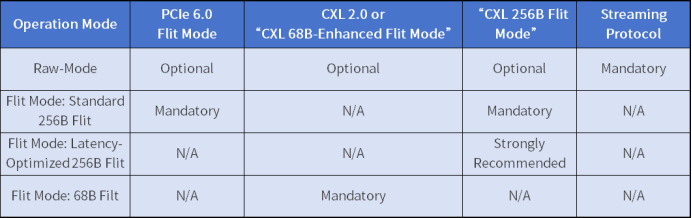

·Protocol層:支持PCIe 6.0、CXL 2.0/3.0協(xié)議,同時還支持Streaming Protocol(用于映射自定義傳輸協(xié)議),允許用戶根據(jù)自身需求定制協(xié)議。在傳輸模式上,分為Raw Mode和Flit Mode。PCIE6.0、CXL2.0/3.0都支持 Raw Mode,在該模式下,所有64B或者 256B數(shù)據(jù)都由協(xié)議層來負責填充,繞過適配層,CRC、FEC和Retry都由協(xié)議層處理;而在Flit Mode下,適配層要對協(xié)議層數(shù)據(jù)添加2B hdr和2B CRC,并在協(xié)商過程中,通過FDI接口把這些信息作為Link Trainning的一部分傳給協(xié)議層。

UCIe Protocol層對應接口運行機制

數(shù)據(jù)傳輸機制

UCIe提供了Mainband及Sideband兩大數(shù)據(jù)通路。

·Mainband:主要用來傳輸業(yè)務數(shù)據(jù)流,采用 DDR雙沿采樣方式。例如,對于標準封裝 x16,8個UI傳輸1個Byte,若有16Lane,傳輸256B數(shù)據(jù)需要128UI。不同條件下單Lane 支持多種傳輸速率,可滿足不同應用場景對帶寬的需求。

·Sideband:主要用來處理鏈路訓練、鏈路管理、參數(shù)交換及寄存器訪問等非數(shù)據(jù)傳輸業(yè)務,作為Mainband的Back Channel。它能夠簡化UCIe中的鏈路訓練、鏈路管理和D2D參數(shù)交換過程,提升Mainband的帶寬利用率并簡化其設計復雜度。UCIe Sideband支持配置讀寫(CfgRd/Wr)、內(nèi)存讀寫(MRd/Wr)、完成(Cpl/Cpld)及消息(Msg/MsgD)4種不同的數(shù)據(jù)包,通過這些數(shù)據(jù)包實現(xiàn)寄存器訪問、Message傳遞等功能,在D2D參數(shù)交換、鏈路訓練、鏈路管理及寄存器訪問等方面發(fā)揮著不可或缺的作用。

鏈路訓練

UCIe采用分層的鏈路狀態(tài)機(LSM),包括 FDI FSM、RDI FSM 和 PHY LSM,來進行鏈路訓練。鏈路訓練是UCIe中非常重要的環(huán)節(jié),通過鏈路訓練,UCIe設備能夠建立起穩(wěn)定可靠的數(shù)據(jù)傳輸鏈路,確定鏈路的各項參數(shù),如傳輸速率、編碼方式等,確保數(shù)據(jù)在不同的UCIe設備之間能夠準確無誤地傳輸。在鏈路訓練過程中,各層狀態(tài)機協(xié)同工作,通過一系列的信號交互和參數(shù)協(xié)商,完成鏈路的初始化和配置,為后續(xù)的數(shù)據(jù)傳輸做好準備。

UCIe與Chiplet發(fā)展的緊密聯(lián)系

為Chiplet提供標準化互連

在UCIe協(xié)議出現(xiàn)之前,Chiplet之間的互連缺乏統(tǒng)一標準,導致不同廠商的Chiplet難以實現(xiàn)互聯(lián)互通,極大地限制了Chiplet技術(shù)的應用范圍。UCIe協(xié)議的誕生填補了這一空白,它定義了一套通用的、開放的Die-to-Die互連標準,包括支持的封裝類型(帶有標準凸點的標準封裝和帶有微凸點的各種高級封裝)、物理層和協(xié)議層規(guī)范、軟件堆棧模型等,使得不同廠商生產(chǎn)的Chiplet能夠按照統(tǒng)一標準進行連接和通信,實現(xiàn)了Chiplet在芯片封裝內(nèi)的即插即用,為Chiplet技術(shù)的大規(guī)模推廣和應用奠定了堅實基礎。

UCIe協(xié)議憑借自身優(yōu)異特性,成為助力 Chiplet技術(shù)發(fā)揮優(yōu)勢的關(guān)鍵。它具備高速、低延遲、低功耗、高帶寬密度等特點,且擁有極低的誤碼率,低速時BER<1e-27,高速時BER<1e-15。這些特性為Chiplet之間的數(shù)據(jù)傳輸提供了堅實保障,讓不同功能的Chiplet 能在穩(wěn)定高效的環(huán)境中協(xié)同工作。以數(shù)據(jù)中心的高性能計算芯片為例,通過UCIe連接多個Chiplet后,能顯著提升計算性能,同時降低功耗,很好地滿足了數(shù)據(jù)中心對算力和能效的高要求。

與此同時,UCIe聯(lián)盟的成立以及協(xié)議的不斷更新完善,吸引了眾多行業(yè)巨頭參與其中。這推動了Chiplet產(chǎn)業(yè)生態(tài)在設計、制造、封裝等各個環(huán)節(jié)的完善。像英偉達等芯片廠商已采用相關(guān)設計方案,將Chiplet技術(shù)與UCIe協(xié)議結(jié)合應用到產(chǎn)品中。

該協(xié)議獲得了英特爾、AMD、臺積電等巨頭的支持,技術(shù)標準也在持續(xù)演進。從2022年的1.0版本到2024年的2.0版本,不斷優(yōu)化提升。目前已有基于該協(xié)議的Chiplet產(chǎn)品面市,其在性能、成本等方面的良好表現(xiàn),驗證了UCIe協(xié)議的可行性。可以說,UCIe為Chiplet技術(shù)的發(fā)展提供了有力支撐,未來有望推動半導體行業(yè)邁向新高度。

使用SIDesigner進行仿真

以UCIe為典型代表的Chiplet互連技術(shù),面臨多重物理層挑戰(zhàn):其單通道最高傳輸速率達32Gbps的高速特性、單位面積內(nèi)密集的信號網(wǎng)絡布局,以及對誤碼率(如部分場景需低至 1e-27)的嚴苛要求,共同構(gòu)成了設計難點。

當采用先進封裝技術(shù)實現(xiàn)多芯片模塊高效互連時,信號完整性問題會顯著凸顯 —— 具體包括信號傳輸中的串擾與損耗、時序偏移(Skew)、寄生參數(shù)干擾、電源完整性惡化、熱 - 電耦合效應,以及如何滿足極端嚴苛的誤碼率標準等。

這也使得Chiplet的高速信號完整性仿真成為技術(shù)難題。此類仿真需融合SerDes與DDR總線的雙重仿真特性:既要應對高速率、高誤碼率要求,處理多信號線并行傳輸場景;又要適配單端信號傳輸模式,依賴單端IBIS-AMI模型進行仿真,并需完成電壓傳輸函數(shù)(VTF)等專項仿真驗證。而通過IBIS-AMI模型以及S參數(shù)模型可以簡化這一復雜的過程,同時保證仿真的高精度和高準確性。

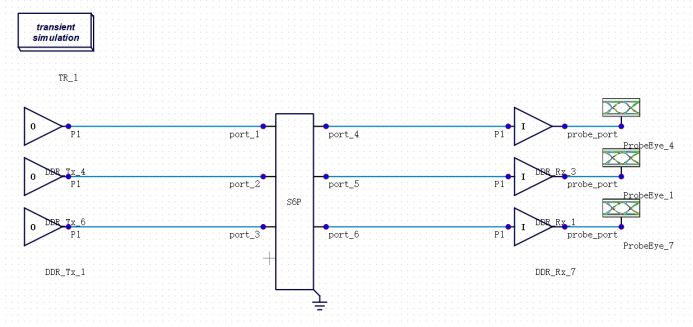

使用巨霖仿真軟件SIDesigner搭建UCIe信號完整性的仿真電路,原理圖如下:

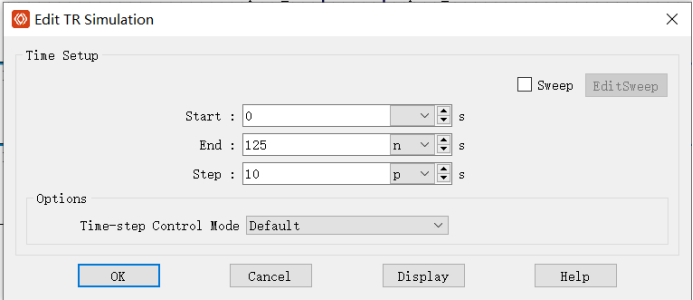

使用瞬態(tài)仿真進行眼圖的測量,仿真設置如下:

信號傳輸速率為16Gbps,使用NRZ調(diào)制方式。模式選擇瞬態(tài)仿真,約1500個UI疊加眼圖。

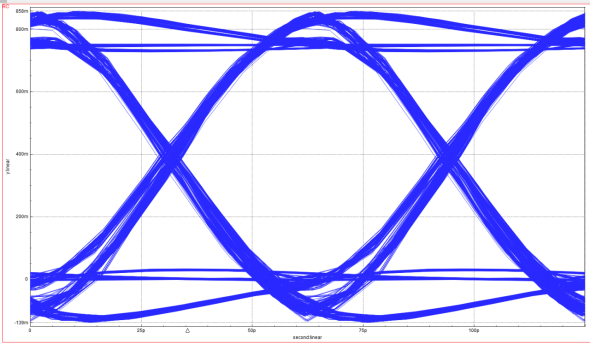

仿真眼圖結(jié)果如下:

工程師可以依據(jù)眼圖直觀反映信號是否滿足高速傳輸?shù)奈锢項l件(如速率、誤碼率),還能定位損耗、抖動、串擾等具體問題,為設計優(yōu)化提供精準依據(jù)。對于UCIe這類高帶寬、高密度、高可靠性要求的Chiplet互連技術(shù),眼圖分析是驗證設計可行性、保障最終性能的核心環(huán)節(jié)。

-

半導體

+關(guān)注

關(guān)注

339文章

31113瀏覽量

265935 -

chiplet

+關(guān)注

關(guān)注

6文章

499瀏覽量

13638 -

UCIe

+關(guān)注

關(guān)注

0文章

53瀏覽量

2029 -

芯粒

+關(guān)注

關(guān)注

1文章

88瀏覽量

443

原文標題:UCIe協(xié)議: 推動Chiplet發(fā)展的關(guān)鍵力量

文章出處:【微信號:巨霖,微信公眾號:巨霖】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

GSM GPRS模塊數(shù)據(jù)傳輸格式問題

UART協(xié)議的數(shù)據(jù)傳輸格式是怎樣的

數(shù)據(jù)傳輸介質(zhì)

基于短消息的OTA數(shù)據(jù)傳輸安全機制

數(shù)據(jù)傳輸,數(shù)據(jù)傳輸的工作方式有哪些?

數(shù)據(jù)傳輸速率是什么意思

數(shù)字數(shù)據(jù)傳輸(DDN),數(shù)字數(shù)據(jù)傳輸(DDN)的工作原理是什

基于CLRP_MS位置疊取的節(jié)能WSNs數(shù)據(jù)傳輸機制_王德銘

以太網(wǎng)數(shù)據(jù)傳輸系統(tǒng)的設計與應用介紹

tcp_ip 協(xié)議講座:介紹數(shù)據(jù)傳輸

基于UDP協(xié)議和FPGA的點到點數(shù)據(jù)傳輸方案

如何實現(xiàn)MQTT協(xié)議數(shù)據(jù)傳輸?

DTU的多種協(xié)議,解鎖數(shù)據(jù)傳輸的無限可能

UCIe協(xié)議的工作原理和數(shù)據(jù)傳輸機制

UCIe協(xié)議的工作原理和數(shù)據(jù)傳輸機制

評論