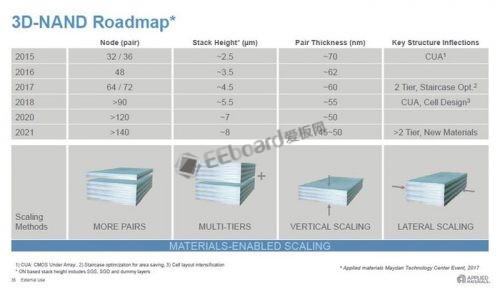

在正在舉行的國際存儲研討會2018(IMW 2018)上,應用材料公司Sean Kang介紹了未來幾年3D-NAND的發展線路圖,到了2021年,3D-NAND的堆疊層數會超過140層,而且每一層的厚度會不斷的變薄。

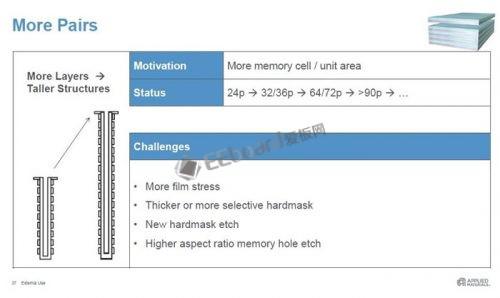

身在日本的PC Watch前往了本次會議的研討會,自3D-NAND誕生以來它的堆疊層數就在不斷的增長,三星造出來的第一代3D V-NAND只有24層,下一代就變成了32層,隨后就變成48層,到了現在大多數廠商都是64層,而SK海力士則是72層,而下一代的3D-NAND堆疊層數將超過90層,再下一個階段會超過120層,到了2021年會超過140層。

而閃存的Die Size也隨著堆疊層數的增長而增長,在32層時代的時候是128Gbit,48層時256Gbit,64/72層是512Gbit,明年的96層閃存應該會達到768Gbit,128層應該會有1024Gbit的Die Size,達到144層時就不清楚會有多大了,肯定會大于等于1024Gbit。

在堆疊層數增加的時候,存儲堆棧的高度也在增大,然而每層的厚度缺在縮小,以前的32/36層3D NAND的堆棧厚度為2.5μm,層厚度大約70nm,48層的閃存堆棧厚度為3.5μm,層厚度減少到62nm,現在的64/72層閃存堆棧厚度大約4.5μm,每層厚度減少到60nm,沒升級一次堆棧厚度都會變成原來的1.8倍,而層厚度會變成0.86倍。

現在各家廠商都在3D NAND上加大力度研發,盡可能提升自己閃存的存儲密度,此前東芝與西數就宣布計劃在今年內大規模生產96層堆疊的BiCS4芯片,并會在年底前發貨。

-

閃存

+關注

關注

16文章

1913瀏覽量

117441 -

可制造性設計

+關注

關注

10文章

2066瀏覽量

16492 -

3D-NAND

+關注

關注

0文章

4瀏覽量

2817 -

華秋DFM

+關注

關注

20文章

3515瀏覽量

6515

發布評論請先 登錄

纖納光電亮相2026鈣鈦礦與疊層電池產業融合發展論壇

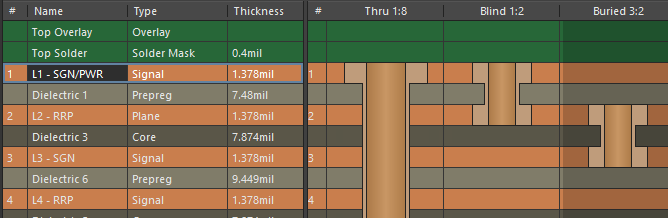

從8層到30層:AI服務器PCB層數進階,PCle 5.0高速傳輸需求成關鍵

疊層固態電容的性能優勢

洛微科技攜4D FMCW激光雷達與3D感知方案閃耀光博會,引領行業新趨勢

貼片電感代理-疊層電感的實際應用

SK海力士321層4D NAND的誕生

PCB疊層設計避坑指南

Sean Kang介紹未來幾年3D-NAND的發展線路圖,2021年堆疊層數會超過140層,而且會不斷變薄

Sean Kang介紹未來幾年3D-NAND的發展線路圖,2021年堆疊層數會超過140層,而且會不斷變薄

評論