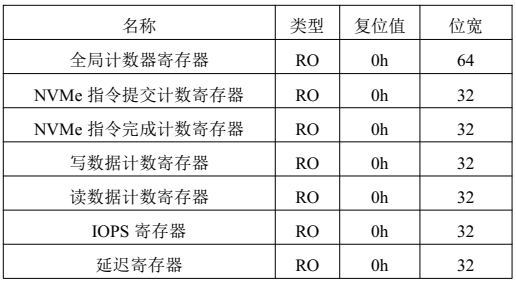

性能監(jiān)測(cè)單元負(fù)責(zé)監(jiān)測(cè) NVMe over PCIe 邏輯加速引擎的運(yùn)行狀態(tài)和統(tǒng)計(jì)信息, 包括復(fù)位后運(yùn)行時(shí)間信息、 NVMe 指令數(shù)量統(tǒng)計(jì)信息、 數(shù)據(jù)操作數(shù)量統(tǒng)計(jì)信息、 IOPS 性能統(tǒng)計(jì)信息、 指令延遲統(tǒng)計(jì)信息等。 這些信息存儲(chǔ)在性能監(jiān)測(cè)單元中的性能監(jiān)測(cè)寄存器組中,性能監(jiān)測(cè)寄存器組定義如表1 所示。

表1 性能監(jiān)測(cè)寄存器組定義

聲明:本文內(nèi)容及配圖由入駐作者撰寫(xiě)或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

FPGA

+關(guān)注

關(guān)注

1660文章

22411瀏覽量

636278 -

PCIe

+關(guān)注

關(guān)注

16文章

1461瀏覽量

88407 -

高速存儲(chǔ)

+關(guān)注

關(guān)注

0文章

15瀏覽量

6085 -

nvme

+關(guān)注

關(guān)注

0文章

299瀏覽量

23839

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

NVMe高速傳輸之擺脫XDMA設(shè)計(jì)23:UVM驗(yàn)證平臺(tái)

驗(yàn)證的硬核 IP,因此在驗(yàn)證過(guò)程中可以只使用其接口進(jìn)行模擬,這將極大減小驗(yàn)證平臺(tái)復(fù)雜度和構(gòu)建難度,同時(shí)對(duì)驗(yàn)證的完備性影響較小.驗(yàn)證平臺(tái)由 UVM 驗(yàn)證包、DUT、AXI BRAM IP 和 NVMe

發(fā)表于 08-26 09:49

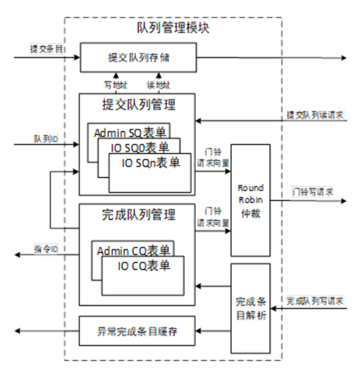

NVMe IP高速傳輸卻不依賴(lài)XDMA設(shè)計(jì)之九:隊(duì)列管理模塊(上)

這是采用PCIe設(shè)計(jì)NVMe,并非調(diào)用XDMA方式,后者在PCIe4.0時(shí)不大方便,故團(tuán)隊(duì)直接采用PCIe設(shè)計(jì),結(jié)合UVM驗(yàn)證加快設(shè)計(jì)速度。 隊(duì)列管理模塊采用隊(duì)列的存儲(chǔ)與控制分離的設(shè)計(jì)結(jié)構(gòu)。

NVMe高速傳輸之擺脫XDMA設(shè)計(jì)18:UVM驗(yàn)證平臺(tái)

驗(yàn)證的硬核 IP,因此在驗(yàn)證過(guò)程中可以只使用其接口進(jìn)行模擬,這將極大減小驗(yàn)證平臺(tái)復(fù)雜度和構(gòu)建難度,同時(shí)對(duì)驗(yàn)證的完備性影響較小.驗(yàn)證平臺(tái)由 UVM 驗(yàn)證包、DUT、AXI BRAM IP 和 NVMe

發(fā)表于 07-31 16:39

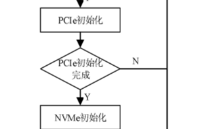

NVMe IP高速傳輸卻不依賴(lài)XDMA設(shè)計(jì)之八:系統(tǒng)初始化

采用XDMA是許多人常用xilinx庫(kù)實(shí)現(xiàn)NVMe或其他傳輸的方法。但是,XDMA介紹較少,在高速存儲(chǔ)設(shè)計(jì)時(shí),尤其是PCIe4.0模式下,較

NVMe高速傳輸之擺脫XDMA設(shè)計(jì)之六:性能監(jiān)測(cè)單元設(shè)計(jì)

性能監(jiān)測(cè)單元負(fù)責(zé)監(jiān)測(cè) NVMe over PCIe 邏輯加速引擎的運(yùn)行狀態(tài)和統(tǒng)計(jì)信息, 包括復(fù)位后

運(yùn)行時(shí)間信息、

發(fā)表于 07-02 19:51

NVMe IP高速傳輸卻不依賴(lài)XDMA設(shè)計(jì)之五:DMA 控制單元設(shè)計(jì)

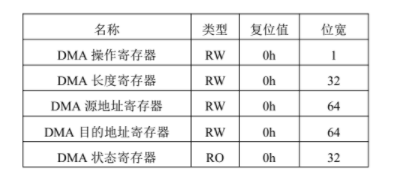

DMA 控制單元負(fù)責(zé)控制 DMA 傳輸事務(wù), 該單元承擔(dān)了 DMA 事務(wù)到 NVMe 事務(wù)的轉(zhuǎn)換任務(wù), 使用戶(hù)對(duì)數(shù)據(jù)傳輸事務(wù)的控制更加簡(jiǎn)單快

NVMe IP高速傳輸卻不依賴(lài)XDMA設(shè)計(jì)之五:DMA 控制單元設(shè)計(jì)

DMA 控制單元負(fù)責(zé)控制 DMA 傳輸事務(wù), 該單元承擔(dān)了 DMA 事務(wù)到 NVMe 事務(wù)的轉(zhuǎn)換任務(wù), 使用戶(hù)對(duì)數(shù)據(jù)傳輸事務(wù)的控制更加簡(jiǎn)單快

發(fā)表于 07-02 19:45

NVMe IP高速傳輸擺脫XDMA設(shè)計(jì)之四:系統(tǒng)控制模塊設(shè)計(jì)

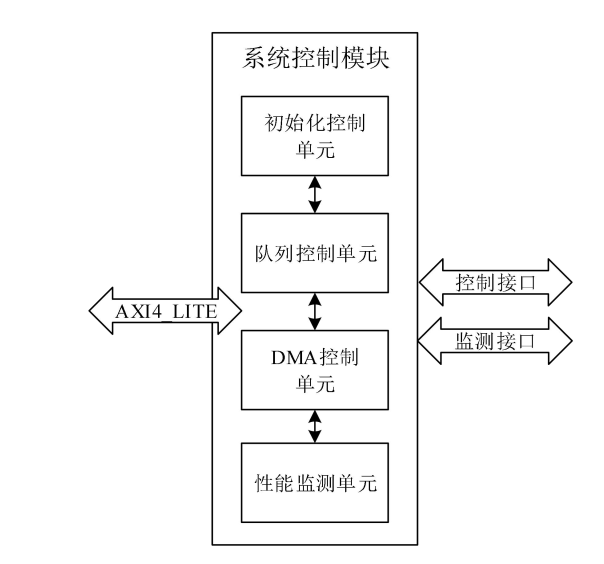

加速引擎的工作狀態(tài)也通過(guò)此模塊反饋給用戶(hù)。 系統(tǒng)控制模塊包含了初始化控制單元、 隊(duì)列控制單元、 DMA 控制單元和性能監(jiān)測(cè)

發(fā)表于 06-29 18:07

NVMe IP高速傳輸卻不依賴(lài)XDMA設(shè)計(jì)之四:系統(tǒng)控制模塊

系統(tǒng)控制模塊負(fù)責(zé)實(shí)現(xiàn) NVMe over PCI 邏輯加速引擎的控制功能, 其結(jié)構(gòu)如圖 1 所示。 用戶(hù)通過(guò)系統(tǒng)控制模塊實(shí)現(xiàn)對(duì)初始化功能、 隊(duì)列管理功能、 DMA 功能等主要功能的控制, 同時(shí)邏輯加速引擎的工作狀態(tài)也通過(guò)此模塊反饋給用戶(hù)。

NVMe IP高速傳輸卻不依賴(lài)XDMA設(shè)計(jì)之三:系統(tǒng)架構(gòu)

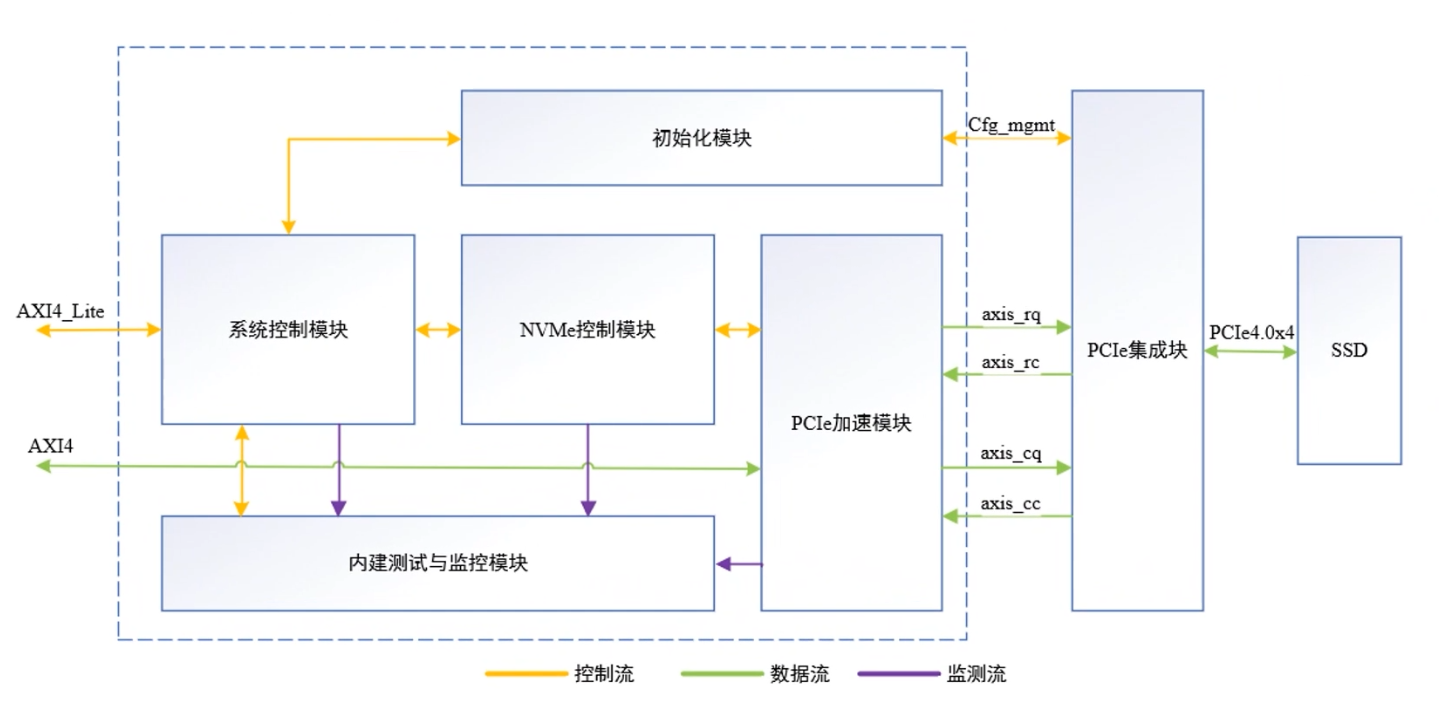

所設(shè)計(jì)的新系統(tǒng)架構(gòu)中,Nvme over PCIe IP通過(guò) PCIe 3.0x4 接口連接 NVMe固態(tài)硬盤(pán), 并提供 AXI4-Lite 接口用于系統(tǒng)控制, 以及 AXI4 接口用于數(shù)據(jù)傳

NVMe IP高速傳輸卻不依賴(lài)便利的XDMA設(shè)計(jì)之三:系統(tǒng)架構(gòu)

請(qǐng)求數(shù)據(jù)傳輸, 數(shù)據(jù)傳輸通過(guò) AXI4總線(xiàn)接口對(duì)接用戶(hù)邏輯, 使用突發(fā)傳輸提高數(shù)據(jù)傳輸性能。

圖1 Nv

發(fā)表于 06-29 17:42

NVMe IP高速傳輸卻不依賴(lài)XDMA設(shè)計(jì)之二:PCIe讀寫(xiě)邏輯

應(yīng)答模塊的具體任務(wù)是接收來(lái)自PCIe鏈路上的設(shè)備的TLP請(qǐng)求,并響應(yīng)請(qǐng)求。由于基于PCIe協(xié)議的NVMe數(shù)據(jù)傳輸只使用PCIe協(xié)議的存儲(chǔ)器讀請(qǐng)求TLP和存儲(chǔ)器寫(xiě)請(qǐng)求TLP,應(yīng)答模塊分別針對(duì)兩種TLP設(shè)置處理引擎來(lái)提高并行性和處理速度。

NVMe IP高速傳輸卻不依賴(lài)便利的XDMA設(shè)計(jì)之二

NVMe IP放棄XDMA原因

選用XDMA做NVMe IP的關(guān)鍵

發(fā)表于 05-25 10:20

NVMe IP高速傳輸卻不依賴(lài)便利的XDMA設(shè)計(jì)之一

NVMe IP放棄XDMA原因

選用XDMA做NVMe IP的關(guān)鍵

發(fā)表于 05-24 17:09

NVMe IP over PCIe 4.0:擺脫XDMA,實(shí)現(xiàn)超高速!

基于NVMe加速引擎,它直接放棄XDMA,改為深度結(jié)合PCIe,通過(guò)高速傳輸機(jī)制開(kāi)發(fā)。同時(shí)利用UVM驗(yàn)證平臺(tái)驗(yàn)證,有效提升工作效率。

NVMe IP高速傳輸卻不依賴(lài)XDMA設(shè)計(jì)之六:性能監(jiān)測(cè)單元設(shè)計(jì)

NVMe IP高速傳輸卻不依賴(lài)XDMA設(shè)計(jì)之六:性能監(jiān)測(cè)單元設(shè)計(jì)

評(píng)論