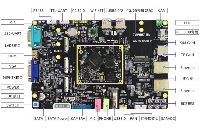

在使用飛凌嵌入式RK3568核心板搭配自制底板時,由于PCB走線與參考設計存在差異,常導致RGMII接口時序異常,進而出現網口不通或頻繁丟包的情況。本文將為大家提供一套簡單高效的調試方案,通過三步操作即可解決此類問題。

1、測試條件

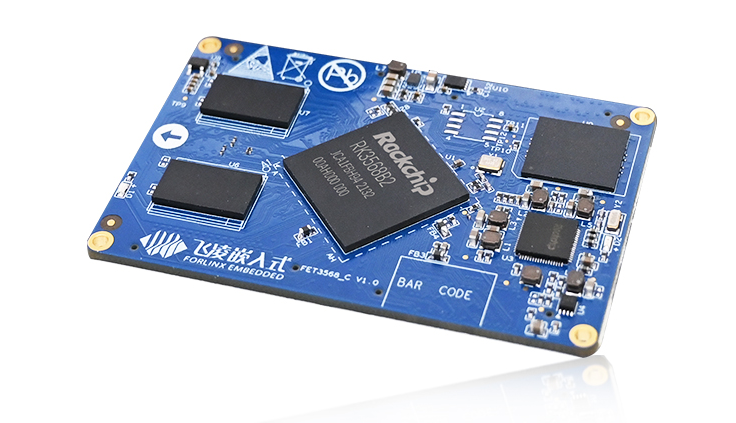

① 硬件:飛凌嵌入式RK3568核心板;

② 系統:Linux4.19.206;

③ 底板:用戶自制底板,且底板設計基本遵循飛凌提供的RK3568核心板參考原理圖,但PCB走線存在差異;

④ 問題:網口無法連接或網絡丟包現象嚴重。

2、調試步驟

① 確認系統節點(以RK3568為例)

?進入目錄:/sys/devices/platform/fe300000.ethernet

?確認存在以下關鍵節點:

phy_lb_scan rgmii_delayline phy_lb

② 掃描Delayline窗口(獲取中間值)

重要提示:如果使用RTL8211E PHY 芯片,測試前務必拔掉網線!

?使用1000M (千兆)速率進行掃描:

echo1000> phy_lb_scan

?命令執行完成后,終端會輸出掃描結果,包含兩個關鍵參數:tx_delay 和 rx_delay(例如:tx_delay=0x2e rx_delay=0x0f)。

?記錄這兩個值。

③ 測試掃描得到的Delayline值

?將步驟2中掃描得到的tx_delay和rx_delay值寫入rgmii_delayline節點進行臨時配置:

echo > rgmii_delayline #例如:echo0x2e0x0f > rgmii_delayline

?驗證配置是否生效:

catrgmii_delayline #應顯示剛寫入的值

?使用phy_lb節點進行回環測試 (Loopback Test),驗證TX/RX數據傳輸是否正常:

echo1000 > phy_lb #使用千兆速率測試

?關鍵要求:

必須 確保phy_lb回環測試通過 (pass)。這是后續操作的基礎。如果測試失敗,可能需要重新掃描或檢查硬件。

④ 固化配置到設備樹(DTS)并燒寫固件

?在 phy_lb 測試通過后,將測試有效的 tx_delay 和 rx_delay 值寫入設備樹源文件(DTS)中的GMAC節點。

?找到RK3568的DTS文件中定義gmac的部分(通常在rk3568.dtsi或板級DTS文件中)。

?修改tx_delay和rx_delay屬性值為測試通過的值:

&gmac { assigned-clocks = <&cru SCLK_RMII_SRC>; assigned-clock-parents = <&clkin_gmac>; clock_in_out ="input"; phy-supply = <&vcc_lan>; phy-mode ="rgmii"; pinctrl-names ="default"; pinctrl-0= <&rgmii_pins>; snps,reset-gpio = <&gpio3 RK_PB7 GPIO_ACTIVE_LOW>; snps,reset-active-low; snps,reset-delays-us = <0?10000?50000>; tx_delay = <0x2e>; //替換為掃描測試得到的有效tx_delay值(十六進制) rx_delay = <0x0f>;//替換為掃描測試得到的有效rx_delay值(十六進制) status ="okay"; };

?重新編譯包含修改后DTS的內核或完整固件。

?將新固件燒錄到 RK3568核心板。

⑤ 最終驗證

?設備啟動后,進行網絡連接測試:

使用ping命令測試網絡連通性和穩定性。

使用iperf3等工具進行網絡帶寬和性能測試,檢查是否還存在丟包。

?一般情況下,完成以上步驟并驗證通過后,網口不通或丟包問題應得到解決。

3、重要提示

① 操作風險:

修改RGMII delayline 參數是底層硬件調優。錯誤的參數可能導致網口完全失效。強烈建議在操作前備份原始固件和DTS文件。

② 測試必要性:

步驟3 (phy_lb回環測試)必須通過才能將參數寫入 DTS。跳過此測試直接固化參數風險極高。

③ 硬件差異:

此方法主要解決因PCB走線差異引起的時序問題。如果自制底板與參考設計差異很大,或者存在其他硬件故障,此方法可能無效。

④參數值:

示例中的0x2e和0x0f僅為說明格式,必須使用phy_lb_scan掃描并結合phy_lb測試驗證得到的實際有效值。

4、總結

當用RK3568自制底板遇到因PCB走線差異導致的RGMII時序跑偏問題時,使用“掃描-驗證-固化”三步急救:echo掃描最佳tx/rx_delay → phy_lb回環驗證 → DTS一鍵寫入,即可讓崩潰的網口原地復活。

飛凌嵌入式FET3568-C核心板基于Rockchip RK3568處理器開發設計,該處理器是Rockchip面向于AIoT和工業市場打造的一款高性能、低功耗、功能豐富的國產化應用處理器。四核64位Cortex-A55架構,主頻高達2.0GHz,且內置1TOPS算力NPU,而且經過了嚴苛的環境溫度測試、壓力測試、長期穩定性運行測試,確保其工作的穩定可靠。

-

嵌入式

+關注

關注

5202文章

20532瀏覽量

335570 -

AI

+關注

關注

91文章

40354瀏覽量

301935 -

VLMx234

+關注

關注

0文章

2瀏覽量

5747 -

大模型

+關注

關注

2文章

3696瀏覽量

5216 -

LLM

+關注

關注

1文章

348瀏覽量

1367

發布評論請先 登錄

鴻蒙OpenHarmony【標準系統編譯】 (基于RK3568開發板)

用RK3568自制底板狂丟包?5分鐘教你用Delayline一鍵復活網口

【HZ-RK3568開發板免費體驗】合眾HZ-RK3568開發板初次使用

RK3568掃描千兆網口延時TX RX出錯請問該怎么解決這個問題

一文解析RK3568編譯OpenHarmony

迅為RK3568開發板 OpenHarmony v3.2-Beta4 版本測試

RK3568底板PCB設計總結

ROC RK3568 PC源代碼RK3568/RK3588 RKNN SDK

RK3568自制底板狂丟包?教你5分鐘用Delayline一鍵復活網口

RK3568自制底板狂丟包?教你5分鐘用Delayline一鍵復活網口

評論