干擾從何而來

在深入探討提升晶振抗干擾能力的電路設(shè)計(jì)方法之前,我們先來追根溯源,了解一下干擾究竟從何而來。干擾就像隱藏在暗處的“敵人”,時(shí)刻威脅著晶振的正常工作,而了解這些干擾源,是我們戰(zhàn)勝它們的第一步。

電磁干擾(EMI):看不見的電波“殺手”

在我們生活的空間里,充滿了各種電磁波,它們就像一張無形的網(wǎng),無處不在。手機(jī)信號(hào)、Wi-Fi信號(hào)、藍(lán)牙信號(hào),還有各種電子設(shè)備產(chǎn)生的電磁輻射,都可能成為干擾晶振的源頭。當(dāng)這些電磁波與晶振電路相互作用時(shí),就會(huì)在電路中產(chǎn)生感應(yīng)電流或電壓,從而干擾晶振的正常振蕩,導(dǎo)致頻率漂移、信號(hào)失真等問題。

電源噪聲:不穩(wěn)定的供電“隱患”

電源是電子設(shè)備的“心臟”,而電源噪聲則是這顆“心臟”的不穩(wěn)定因素。電源在為晶振提供電能時(shí),可能會(huì)因?yàn)殡娫幢旧淼馁|(zhì)量問題、其他設(shè)備的干擾或者電路中的紋波等原因,產(chǎn)生各種噪聲。這些噪聲會(huì)通過電源線路傳導(dǎo)到晶振電路中,影響晶振的工作。

溫度變化:環(huán)境的“隱形殺手”

溫度,這個(gè)看似平常的環(huán)境因素,對(duì)晶振的影響卻不容小覷。晶振中的石英晶體對(duì)溫度非常敏感,當(dāng)溫度發(fā)生變化時(shí),石英晶體的物理特性也會(huì)隨之改變。溫度升高,晶體可能會(huì)發(fā)生熱膨脹,導(dǎo)致其諧振頻率發(fā)生偏移;溫度降低,晶體的彈性系數(shù)等參數(shù)也會(huì)變化,同樣會(huì)影響晶振的頻率穩(wěn)定性。

電路設(shè)計(jì)來救場

面對(duì)這些干擾源的重重挑戰(zhàn),我們并非束手無策。通過精心設(shè)計(jì)電路,就像為晶振打造一座堅(jiān)固的堡壘,能有效提升它的抗干擾能力。

電源設(shè)計(jì)優(yōu)化

電源噪聲是干擾晶振的重要因素之一,因此優(yōu)化電源設(shè)計(jì)至關(guān)重要。我們可以在電源輸入端加入適當(dāng)?shù)?a href="http://www.3532n.com/tags/濾波器/" target="_blank">濾波器,如低通濾波器或去耦電容,像瓷片電容或鉭電容,它們能夠有效濾除電源中的高頻噪聲和紋波,為晶振提供相對(duì)穩(wěn)定的直流電壓。也可以為晶振和其他高頻模塊提供獨(dú)立電源,減少電源相互干擾。增加穩(wěn)壓電路,采用穩(wěn)壓芯片或穩(wěn)壓模塊,確保晶振的供電電壓穩(wěn)定在其規(guī)定的工作電壓范圍內(nèi),避免因電壓波動(dòng)導(dǎo)致晶振頻率不穩(wěn)定,進(jìn)而提高其抗干擾能力。

地線設(shè)計(jì)強(qiáng)化

良好的地線設(shè)計(jì)有助于降低系統(tǒng)的噪聲耦合,提高抗干擾能力。在多層電路板設(shè)計(jì)中,我們可以使用單獨(dú)的地線層,確保晶振電路的地線與其他高頻信號(hào)電路分開,避免地線噪聲影響。盡可能縮短晶振與相關(guān)電路元件之間的連線長度,減少信號(hào)傳輸過程中的延遲和衰減,降低信號(hào)受到干擾的可能性。同時(shí),要防止晶振的時(shí)鐘信號(hào)線路與其他高頻信號(hào)線路或強(qiáng)干擾源線路交叉,以減少信號(hào)間的串?dāng)_。如果無法避免交叉,應(yīng)采用垂直交叉方式,并在交叉處增加隔離措施,如用地線進(jìn)行隔離。設(shè)計(jì)低阻抗的地線,使地線盡量寬且短,以降低地線噪聲,還要避免形成地環(huán)路,防止地電流對(duì)晶振產(chǎn)生干擾。對(duì)于高速時(shí)鐘信號(hào),考慮使用差分信號(hào)線(如LVDS),通過差分傳輸技術(shù)提高抗干擾能力。

屏蔽與隔離措施

在電磁干擾(EMI)較強(qiáng)的環(huán)境中,為晶振提供適當(dāng)?shù)钠帘魏透綦x,可以有效提高抗干擾能力。我們可以通過使用金屬外殼或其他電磁屏蔽材料將晶振模塊封裝起來,隔離外部電磁干擾。將晶振和可能產(chǎn)生干擾的高功率元件(如功率放大器、電機(jī)驅(qū)動(dòng)電路等)隔離開,減少噪聲源對(duì)時(shí)鐘信號(hào)的影響。

外部濾波器運(yùn)用

對(duì)于高頻干擾,添加外部濾波器或信號(hào)調(diào)節(jié)電路(如低通濾波器或帶通濾波器)可以幫助降低噪聲對(duì)時(shí)鐘信號(hào)的影響。濾波器可以用于時(shí)鐘輸出端口,去除高頻噪聲,確保時(shí)鐘信號(hào)的質(zhì)量。

布局與安裝要點(diǎn)

晶振的布局和安裝位置也會(huì)影響其抗干擾能力。將晶振模塊安裝在遠(yuǎn)離強(qiáng)電磁干擾源的位置。過熱會(huì)影響晶振的穩(wěn)定性,所以要選擇良好的散熱設(shè)計(jì)和位置,確保晶振在最佳溫度范圍內(nèi)工作。在多層電路板設(shè)計(jì)中,可以為時(shí)鐘信號(hào)和電源設(shè)計(jì)專門的“電源層”和“地層”,通過良好的電磁屏蔽來減少干擾,這種設(shè)計(jì)有助于提高信號(hào)質(zhì)量和系統(tǒng)抗干擾能力。

審核編輯 黃宇

-

電路設(shè)計(jì)

+關(guān)注

關(guān)注

6741文章

2700瀏覽量

219502 -

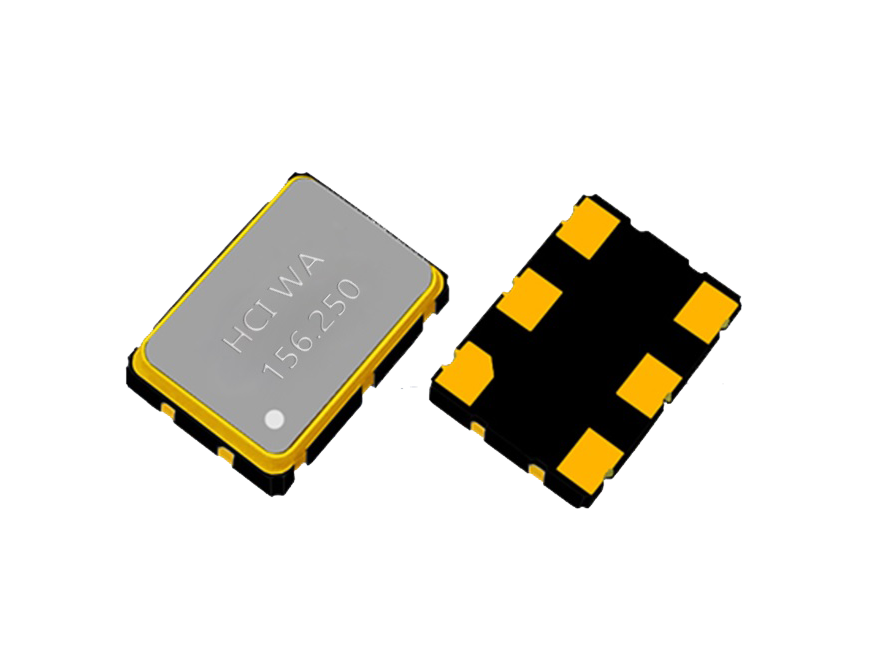

晶振

+關(guān)注

關(guān)注

35文章

3560瀏覽量

73436

發(fā)布評(píng)論請(qǐng)先 登錄

高速外部無源晶振(HEXT)抗干擾設(shè)計(jì)

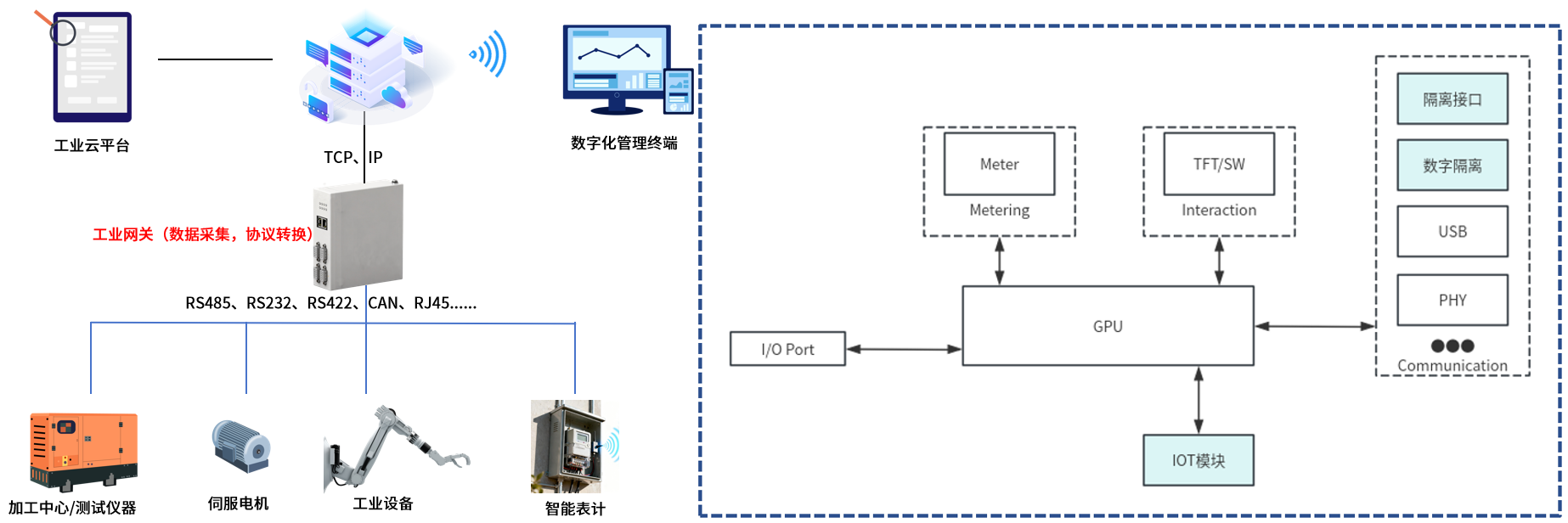

數(shù)字隔離器,如何拉滿工業(yè)網(wǎng)關(guān)的電氣安全性能與抗干擾能力?

淺談晶振在PCB設(shè)計(jì)中的要點(diǎn)

電子發(fā)燒友必看!電子水尺抗干擾電路設(shè)計(jì)的3個(gè)核心技巧

晶振的頻率誤差可以修正嗎

單片機(jī)硬件設(shè)計(jì)原則,抗干擾常用方法

提高單片機(jī)抗干擾能力的十個(gè)細(xì)節(jié)

晶振電路的PCB設(shè)計(jì)

晶振為什么要緊靠著IC

差分晶振在高速 FPGA 上的應(yīng)用

芯片抗干擾能力概述

網(wǎng)線怎么抗干擾

如何通過電路設(shè)計(jì)提升晶振的抗干擾能力

如何通過電路設(shè)計(jì)提升晶振的抗干擾能力

評(píng)論