在電路設計中,系統晶振時鐘頻率很高,干擾諧波出來的能量也強,諧波除了會從輸入與輸出兩條線導出來外,也會從空間輻射出來,這也導致在PCB設計中對晶振的布局要求嚴格,如果出錯會很容易造成很強的雜散輻射問題,并且很難通過其他方法來解決,所以在PCB板布局時對晶振和CLK信號線布局很關鍵。

布局與走線設計

晶振內部是石英晶體,如果不慎掉落或受不明撞擊,石英晶體易斷裂破損,所以晶振的放置遠離板邊,靠近MCU的位置布局。

晶振緊鄰主控芯片(如MCU、FPGA)時鐘輸入引腳,最大走線長度≤10mm。

遠離高速信號線(如DDR、USB差分對),間距≥3倍線寬,避免串擾。

走線長度與寬度?:時鐘走線應盡量短且直,線寬適當加粗以降低阻抗,但需平衡與發熱源的距離。?對于高頻信號(如10 MHz以上),走線長度需控制在500 mil以內。

包地屏蔽?:時鐘走線建議包地處理,用地線包圍信號線,并每隔一段距離(如100 mil)打過孔連接地層,增強抗干擾能力。?

避免交叉干擾?:晶振輸出信號線不得跨越電源層或敏感信號線,若必須跨越需垂直走線并保持間距。

去耦與濾波

電源去耦?:晶振電源引腳需加去耦電容(如100nF陶瓷電容),靠近引腳放置,以濾除高頻噪聲。?4 對于有源晶振,電源線可串聯小電阻(47~100 Ω)限流。?

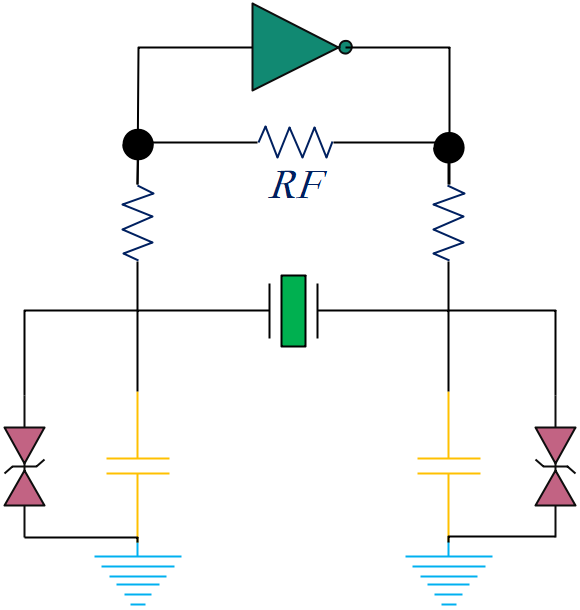

負載電容配置?:無源晶振需外接負載電容(Cg和Cd),其值需滿足:負載電容CL = (Cg × Cd) / (Cg + Cd) + 雜散電容(Cs)。雜散電容通常取2~5 pF,設計時需根據晶振規格調整Cg和Cd值(例如CL=15 pF時,可取Cg=Cd=24 pF)

耦合電容應盡量靠近晶振的電源管腳,如果多個耦合電容,按照電源流入方向,依次容值從大到小擺放;晶振則要盡量的靠近MCU

其他說明

高獨立:盡可能保證晶振周圍的沒有其他元件。防止器件之間的互相干擾,影響時鐘和其他信號的質量。晶振周圍 1mm 禁布器件,0.5mm 禁布過孔走線,所有晶振下不打過孔(包括地過孔)。當心晶振和地的走線。

盡可能將其它時鐘線路與頻繁切換的信號線路布置在遠離晶振連接的位置。

外殼要接地:晶振的外殼必須要接地,除了防止晶振向外輻射,也可以屏蔽外來的干擾。

-

晶振

+關注

關注

35文章

3616瀏覽量

73719 -

PCB設計

+關注

關注

396文章

4931瀏覽量

95629 -

時鐘頻率

+關注

關注

0文章

73瀏覽量

21151

原文標題:炬烜知識匯|晶振在PCB設計中的要點

文章出處:【微信號:炬烜科技,微信公眾號:炬烜科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

晶振不起振也可能是PCB設計的鍋

石英晶振的設計要點有哪些

晶振電源電路及PCB設計要點資料下載

淺談晶振在PCB設計中的要點

淺談晶振在PCB設計中的要點

評論