聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

dsp

+關注

關注

561文章

8244瀏覽量

366646 -

FPGA

+關注

關注

1660文章

22412瀏覽量

636317 -

Xilinx

+關注

關注

73文章

2200瀏覽量

131139

發布評論請先 登錄

相關推薦

熱點推薦

基于4片DSP6678+FPGA KU115 的VPX高速信號處理平臺

板卡基于標準6U VPX架構,板載一片Xilinx FPGA XCKU115-2FLVF1924I和四片 TI 多核DSP TMS320C6678,每個DSP有配有2GB的儲存空間,該板卡可以通過

發表于 03-06 14:58

從算法到部署:Enclustra如何用DSP+FPGA/SoC專長,實現功耗與成本雙優化?

DSP技術數字信號處理(DSP)是FPGA和SoC的常見應用領域。為了在此領域為客戶提供最優服務,Enclustra積累了深厚的DSP專業知識,不僅能提供純粹的實現服務,更能從零開始支

FPGA DSP模塊使用中的十大關鍵陷阱

FPGA 芯片中DSP(數字信號處理)硬核是高性能計算的核心資源,但使用不當會引入隱蔽性極強的“坑”。這些坑不僅影響性能和精度,甚至會導致功能錯誤。以下是總結了十大關鍵陷阱及其解決方案,分為 功能正確性、性能優化、系統集成 三個層面。

基于DSP與FPGA異構架構的高性能伺服控制系統設計

DSP+FPGA架構在伺服控制模塊中的應用,成功解決了高性能伺服系統對實時性、精度和復雜度的多重需求。通過合理的功能劃分,DSP專注于復雜算法和上層控制,FPGA處理高速硬件任務,兩者協同實現了傳統架構難以達到的性能指標。

DSP的基礎

高速數字信號處理技術是以DSP為核心,具有高速,實時的特點的一種信息處理技術。其本質是信息的變換和提取。DSP(Digital Signal Processor),即數字信號處理器,是一種專用

發表于 11-20 06:35

DSP、FPGA之間SRIO通信的問題?

目前在使用DSP和FPGA之間通過SRIO的SWRITE事務完成雙向數據通信,大多數情況下都正常,但是在我不停的給DSP進行燒寫程序時,會偶爾出錯,FPGA無法收到

發表于 11-15 16:22

如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試

本篇將詳細介紹如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試。SRAM是一種非易失性存儲器,具有高速讀取和寫入的特點。在FPGA中實現SRAM讀寫測試,包括設計SRAM接口模塊

【 VPX638】青翼凌云科技基于KU115 FPGA+C6678 DSP的6U VPX雙FMC接口通用信號處理平臺

VPX638是一款基于KU115 FPGA + C6678 DSP的6U VPX雙FMC接口通用信號處理平臺,該平臺采用一片Xilinx的Kintex UltraScale系列FPGA

中科億海微SoM模組——FPGA+DSP核心板

FPGA+DSP核心板是基于中科億海微EQ6HL130型FPGA芯片搭配國產DSP開發的高性能核心板卡。對外接口采取郵票孔連接方式,可以極大提高信號傳輸質量和焊接后的機械強度。核心板卡的系統框圖如下

適用于Versal的AMD Vivado 加快FPGA開發完成Versal自適應SoC設計

設計、編譯、交付,輕松搞定。更快更高效。 Vivado 設計套件提供經過優化的設計流程,讓傳統 FPGA 開發人員能夠加快完成 Versal 自適應 SoC 設計。 面向硬件開發人員的精簡設計流程

智多晶FIFO_Generator IP介紹

FIFO_Generator是智多晶設計的一款通用型FIFO IP。當前發布的FIFO_Generator IP是2.0版本,相比之前的1.1版本主要新增了非等比輸入輸出數據位寬支持和異步FIFO跨時鐘級數配置功能。

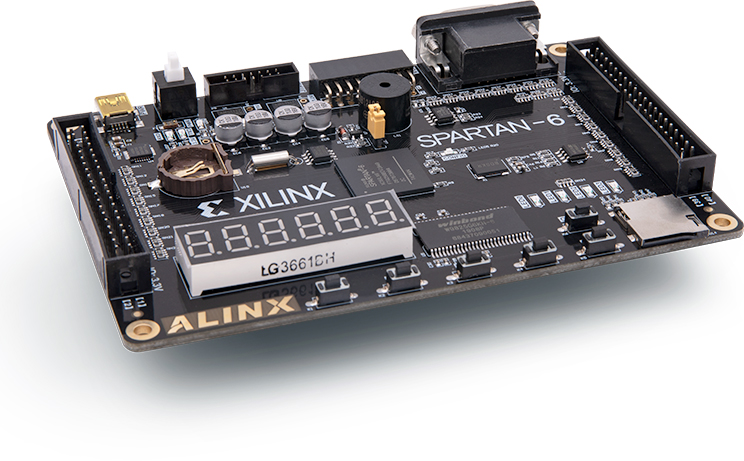

利用 AccelDSP 和 System Generator for DSP? 加快 FPGA 設計

利用 AccelDSP 和 System Generator for DSP? 加快 FPGA 設計

評論