聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

處理器

+關(guān)注

關(guān)注

68文章

20250瀏覽量

252206 -

ADI

+關(guān)注

關(guān)注

151文章

46104瀏覽量

277168 -

sharc

+關(guān)注

關(guān)注

0文章

49瀏覽量

13843

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

ADM8690/ADM8691/ADM8695:微處理器監(jiān)控電路的理想之選

ADM8690/ADM8691/ADM8695:微處理器監(jiān)控電路的理想之選 在微處理器系統(tǒng)的設(shè)計(jì)中,電源監(jiān)控和電池控制是至關(guān)重要的環(huán)節(jié)。ADI公司的ADM8690/ADM8691/AD

Cortex-M0 處理器介紹

Cortex-M0 處理器簡(jiǎn)介ARM公司的Cortex-M0應(yīng)用于各種微控制器(MCU)中,并可讓研發(fā)工程師以8位的價(jià)位創(chuàng)造32位的的效能,并將傳統(tǒng)的8位和16位的處理器升級(jí)到更高效、

發(fā)表于 01-16 08:04

Cortex-M0+處理器的HardFault錯(cuò)誤介紹

在ARM處理器中,如果一個(gè)程序產(chǎn)生了錯(cuò)誤并且被處理器檢測(cè)到,就會(huì)產(chǎn)生錯(cuò)誤異常。Cortex-M0+處理器只有一種異常用以處理錯(cuò)誤:HardFault。

Analog Devices Inc. ADSP-21591/ADSP-21593 SHARC+ 雙核DSP數(shù)據(jù)手冊(cè)

) 瓶頸)以及創(chuàng)新的數(shù)字音頻接口 (DAI)。這些器件是32位、40位或64位浮點(diǎn)處理器。此外,這些器件還具有緩存增強(qiáng)和分支預(yù)測(cè)功能,同時(shí)保持指令集與以前的SHARC產(chǎn)品的兼容性。

Analog Devices Inc. ADSP-21594/ADSP-SC594 SHARC+雙核DSP數(shù)據(jù)手冊(cè)

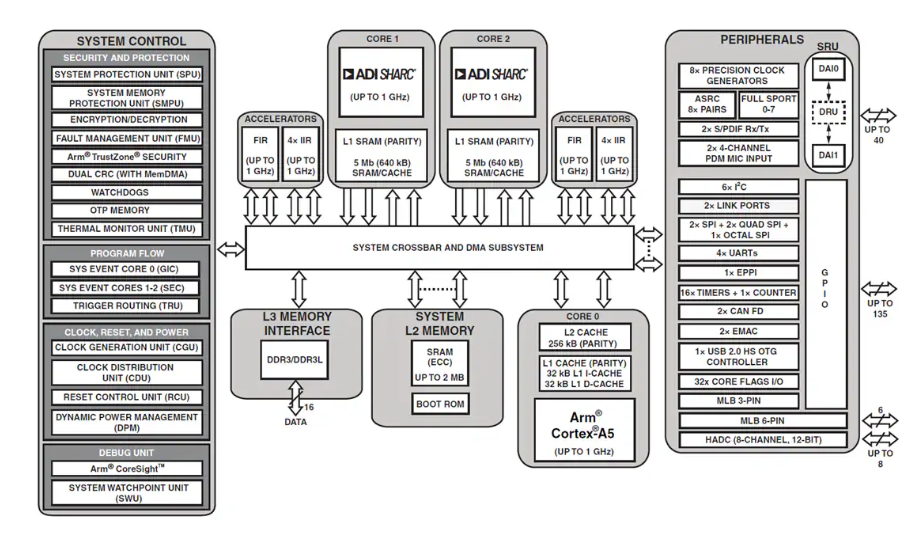

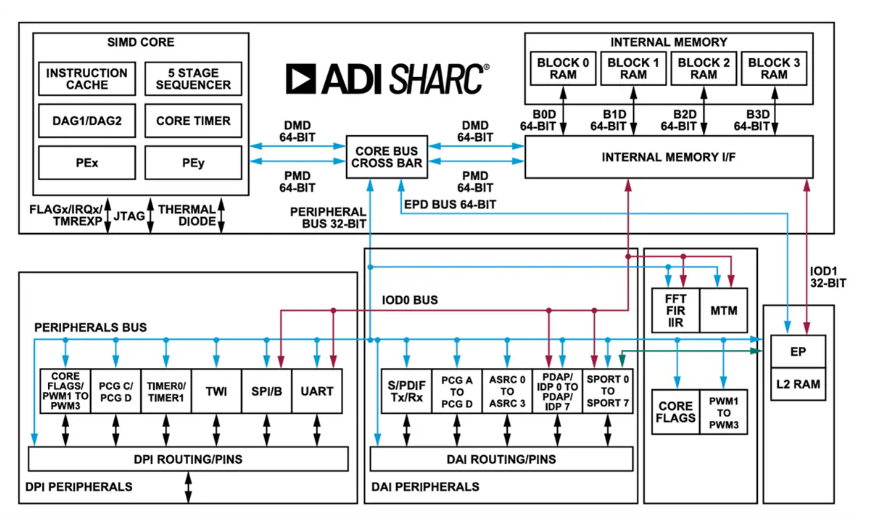

Analog Devices ADSP-21594/ADSP-SC594 SHARC+雙核DSP是單指令多數(shù)據(jù)(SIMD)SHARC系列數(shù)字信號(hào)處理器(DSP)的成員,采用Analog

Analog Devices Inc. ADSP-SC598雙SHARC+?數(shù)字信號(hào)處理器數(shù)據(jù)手冊(cè)

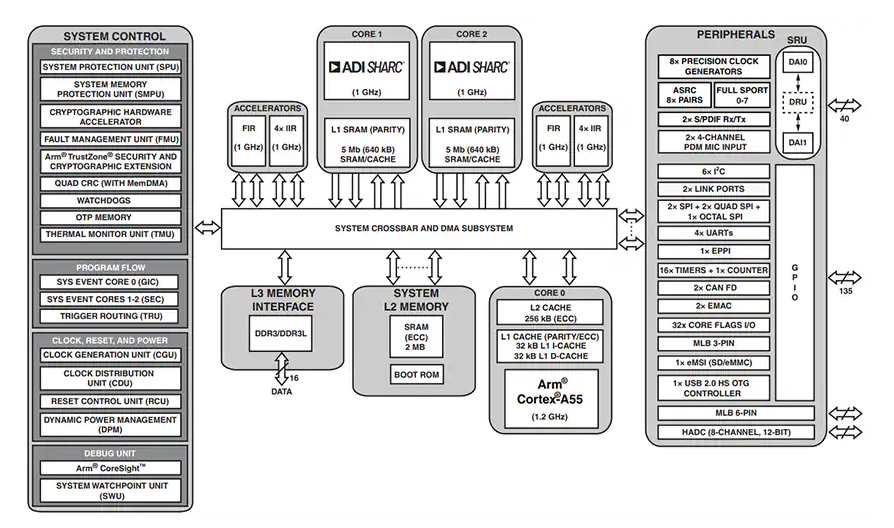

Analog Devices ADSP-SC598雙SHARC+? 數(shù)字信號(hào)處理器 (DSP) 采用集成式Arm? Cortex-A55,運(yùn)行頻率高達(dá)1.2GHz。A55處理器帶有FPU和Neon

Analog Devices Inc. ADSP-SC592 SHARC+?雙核DSP數(shù)據(jù)手冊(cè)

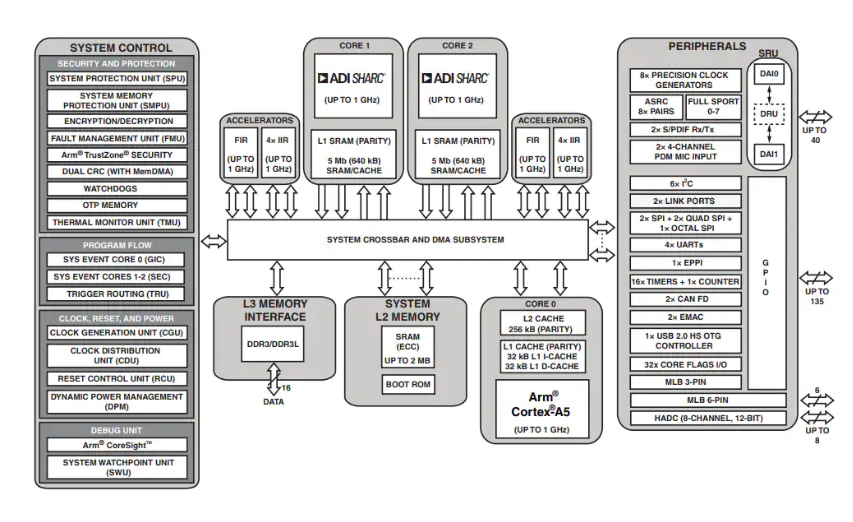

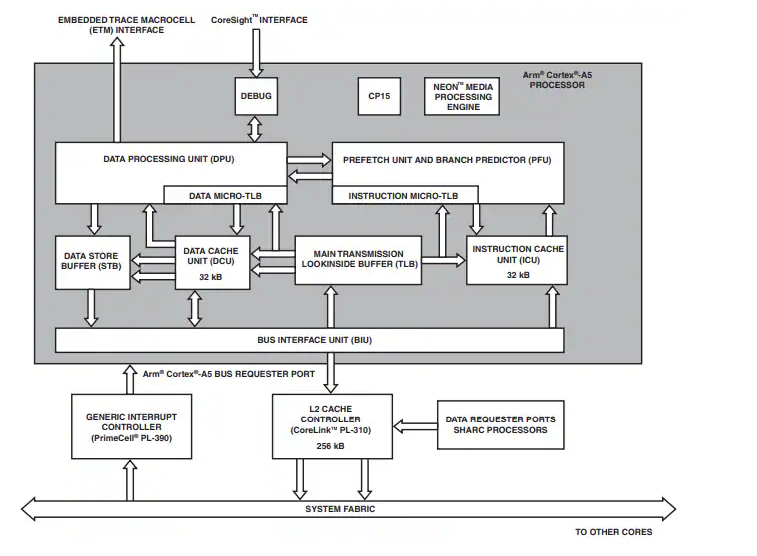

Analog Devices ADSP-SC592 SHARC+^?^ 雙核DSP基于SHARC+雙核和Arm^?^ Cortex ^?^ -A5內(nèi)核。這些數(shù)字信號(hào)處理器(DSP)采用ADI

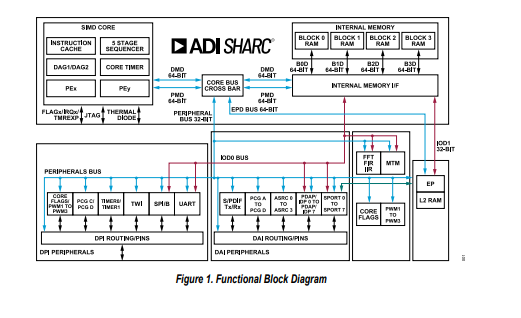

Analog Devices Inc. ADSP1802 SHARC?處理器數(shù)據(jù)手冊(cè)

Analog Devices ADSP1802 SHARC^?^ 處理器是采用ADI Super Harvard架構(gòu)單芯片計(jì)算機(jī)(SHARC)的數(shù)字信號(hào)

請(qǐng)問NICE協(xié)處理器與傳統(tǒng)ocb外設(shè)相比的優(yōu)勢(shì)有什么?

使用擴(kuò)展指令調(diào)用NICE協(xié)處理器完成預(yù)定操作,給出的優(yōu)勢(shì)通常為代替CPU處理數(shù)據(jù),但其實(shí)使用片上總線掛一個(gè)外設(shè),然后驅(qū)動(dòng)外設(shè)完成操作也可以實(shí)現(xiàn)相同的功能,所以想問一下協(xié)處理器相比于外設(shè)

發(fā)表于 05-29 08:21

NICE協(xié)處理器與傳統(tǒng)ocb外設(shè)相比的優(yōu)勢(shì)有什么?

使用擴(kuò)展指令調(diào)用NICE協(xié)處理器完成預(yù)定操作,給出的優(yōu)勢(shì)通常為代替CPU處理數(shù)據(jù),但其實(shí)使用片上總線掛一個(gè)外設(shè),然后驅(qū)動(dòng)外設(shè)完成操作也可以實(shí)現(xiàn)相同的功能,所以想問一下協(xié)處理器相比于外設(shè)

發(fā)表于 05-28 08:31

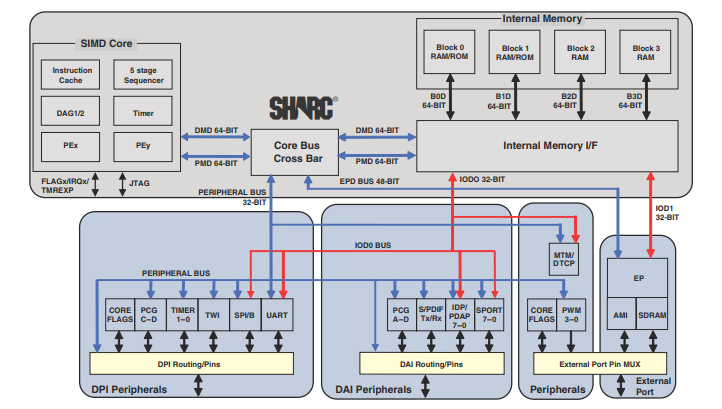

ADSP-21371/ADSP-21375面向汽車音頻的32位高性能浮點(diǎn)SHARC處理器技術(shù)手冊(cè)

第三代SHARC?處理器,其中包括ADSP-21375和ADSP-21371,提供了更高的性能、以音頻和應(yīng)用為重點(diǎn)的外設(shè)和存儲(chǔ)器配置,能夠支持環(huán)繞聲解碼器算法。所有的器件與其它

ADSP1802 SHARC處理器技術(shù)手冊(cè)

ADSP1802 是一款數(shù)字信號(hào)處理器 (DSP),具有 Analog Devices, Inc. 超級(jí)哈佛架構(gòu)單芯片計(jì)算機(jī) (SHARC) 的 S PackageADSP1802 是一個(gè) 32 位

光子 AI 處理器的核心原理及突破性進(jìn)展

,光子 AI 處理器依靠光信號(hào)的傳輸、調(diào)制及檢測(cè)來完成計(jì)算任務(wù),因其具備高速、低功耗、高帶寬等突出優(yōu)勢(shì),被視作突破現(xiàn)有計(jì)算瓶頸的關(guān)鍵技術(shù)之一。 核心原理及面臨的技術(shù)挑戰(zhàn) 光子 AI 處理器的核心原理,是用光子取代電子進(jìn)行運(yùn)算。具

兆芯榮登2025中國(guó)IC設(shè)計(jì)處理器公司TOP10榜單

的自主CPU產(chǎn)品體系、以及顯著的行業(yè)信創(chuàng)成果等多項(xiàng)優(yōu)勢(shì),兆芯成功入圍中國(guó)IC設(shè)計(jì)處理器公司TOP10榜單,再度收獲業(yè)界高度贊許。 ? ? 2025中國(guó)IC設(shè)計(jì)Fabless100榜單覆蓋MCU、AI芯片

ADI公司 SHARC處理器的優(yōu)勢(shì)介紹

ADI公司 SHARC處理器的優(yōu)勢(shì)介紹

評(píng)論