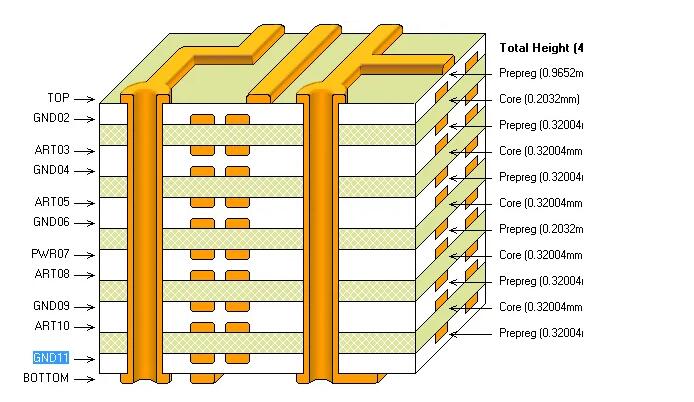

在PCB打樣過程中,層疊結構的設計是至關重要的環(huán)節(jié)。它不僅關系到PCB的性能和穩(wěn)定性,還直接影響到生產(chǎn)成本和制造周期。本文將從PCB的兩個重要組成部分Core和Prepreg(半固態(tài)片,簡稱PP)出發(fā),深入探討PCB多層板的層疊結構設計的先決條件。

一、Core和PP的簡要介紹

Core是PCB多層板的核心組成部分,它的兩個表層都鋪有銅箔,可作為信號層、電源層、地層等導電層。Core的上、下表層之間填充的是固態(tài)材料,具有良好的機械強度和電氣性能。而PP則是一種半固態(tài)的樹脂材料,表面不鋪銅箔,在PCB中起填充作用。PP的材質(zhì)比Core略軟一些,因此在制作多層板時,需配合使用Core和PP,一般在兩個Core之間應選用PP作為填充物。

二、層疊結構設計的先決條件

在進行PCB多層板的層疊結構設計時,需要預先獲取以下信息:單板總層數(shù):包括信號層、電源層、地層的數(shù)目。這些層數(shù)的確定需要根據(jù)單板尺寸、單板規(guī)模(如信號數(shù)目、電源種類等)以及EMC的要求進行粗略估計。

2.jpg

單板厚度:單板厚度與導軌寬度有關,同時也取決于總層數(shù)等因素。例如,14層以內(nèi)的單板厚度可以選擇為1.6mm,而16層以上的單板厚度需在2mm以上。在某些設計中,受限于導軌寬度,而單板總層數(shù)又不能減少,可以采取削邊的方式將單板與導軌接觸的區(qū)域削薄。

目標阻抗:從信號完整性考慮,要求在信號傳輸路徑上實現(xiàn)阻抗的匹配。一般取單端信號對地阻抗為50Ω,而差分對信號間阻抗為100Ω。

PCB材質(zhì)的選擇:主要關注介電常數(shù)Er和材質(zhì)正切值tanδ。介電常數(shù)越大,則電磁場在該材質(zhì)中導通的能力越強。而材質(zhì)正切值tanδ越大,則信號的損耗越大。在高速電路設計中,應盡量選擇Er和tanδ小的材質(zhì)。嘉立創(chuàng)提供的板材在介電常數(shù)和材質(zhì)正切值方面有著優(yōu)異的表現(xiàn),能夠滿足高速電路設計的需求。

三、層疊結構設計的后續(xù)步驟

確定信號層的數(shù)目:根據(jù)PCB上關鍵器件的擺放位置,打開PCB設計軟件的飛線顯示功能,可以粗略估計這些關鍵器件之間的信號線密度,以便對信號層的數(shù)目進行評估。

評估所需電源層、地層的數(shù)目:根據(jù)電源的種類、信號層隔離的要求等,可以評估所需電源層、地層的數(shù)目。

選擇合適的Core和PP厚度:根據(jù)單板總層數(shù)和厚度要求,選擇合適的Core和PP厚度進行搭配。

進行阻抗設計:根據(jù)目標阻抗要求,進行阻抗設計,確保信號在傳輸路徑上實現(xiàn)阻抗匹配。

考慮EMC性能:在層疊結構設計中,還需要考慮EMC性能的要求,通過合理的層疊結構設計來提高PCB的EMC性能。

綜上所述,PCB多層板的層疊結構設計是一個復雜而細致的過程,需要綜合考慮多個因素。通過合理的層疊結構設計,可以確保PCB的性能和穩(wěn)定性,同時降低生產(chǎn)成本和制造周期。

審核編輯 黃宇

-

層疊

+關注

關注

0文章

7瀏覽量

7369 -

PCB

+關注

關注

1文章

2334瀏覽量

13204

發(fā)布評論請先 登錄

復合機器人機械結構設計與創(chuàng)新:智能制造的前沿技術與發(fā)展趨勢

ePTFE防水透氣膜與塑料零件焊接的結構設計指南

知識分享:產(chǎn)品的結構構架與EMC

DES加密運算模塊結構設計

改進型乘法器結構設計

解析GaN-MOSFET的結構設計

自主創(chuàng)新賦能半導體封裝產(chǎn)業(yè)——江蘇拓能半導體科技有限公司與 “半導體封裝結構設計軟件” 的突破之路

冠坤臺系電容:憑獨特卷繞結構設計,成為車規(guī)空間內(nèi)能量儲備的 “擴容專家”

如何優(yōu)化層疊結構以提高PCB線路板整體性能簡述

微孔霧化設備結構設計要點 – 陶瓷片固定&受力分析

OCAD應用:菲涅爾透鏡初始結構設計

高層數(shù)層疊結構PCB的布線策略

在任何平臺上使用PetaLinux的先決條件

PCB層疊結構設計的先決條件

PCB層疊結構設計的先決條件

評論