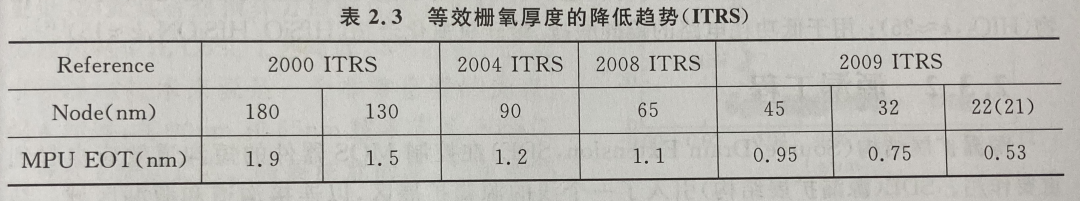

為了有效抑制短溝道效應,提高柵控能力,隨著MOS結構的尺寸不斷降低,就需要相對應的提高柵電極電容。提高電容的一個辦法是通過降低柵氧化層的厚度來達到這一目的。柵氧厚度必須隨著溝道長度的降低而近似地線性降低,從而獲得足夠的柵控能力以確保良好的短溝道行為。另外,隨著柵氧厚度的降低,MOS 器件的驅動電流將獲得提升。由表2.3可見不同技術節點下對柵氧厚度的要求。

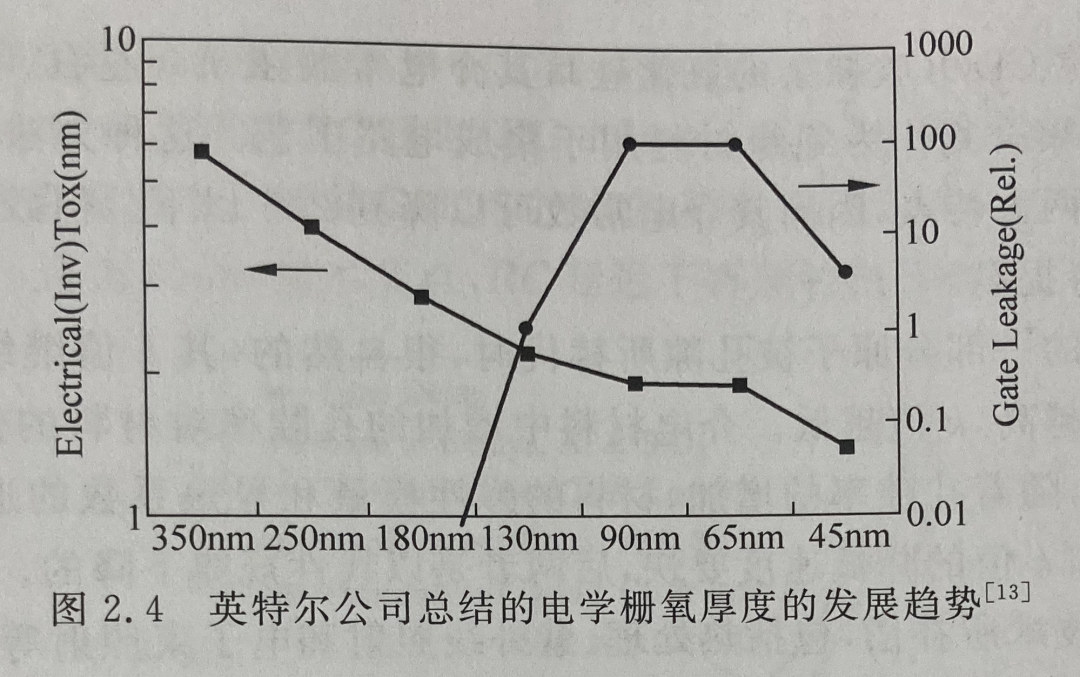

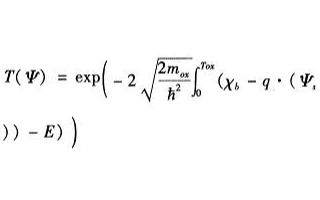

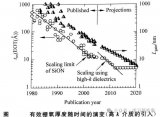

從20世紀70年代第一次被引入集成電路工業中,二氧化硅一直作為硅基MOS管的柵介電材料。然而,不斷降低的二氧化硅的厚度會導致隧穿漏電流的指數提升,功耗增加,而且器件的可靠性問題更為突出;氧化層陷阱和界面陷阱會引起顯著的界面散射和庫倫散射等,降低載流子遷移率;硼穿通問題則影響 PMOSFET 閾值電壓的穩定性;此外,薄柵氧帶來的強場效應會導致明顯的反型層量子化和遷移率退化以及隧穿電流后。圖2.4為英特爾公司總結的柵氧厚度的降低趨勢。

從圖2.4可見,在0.13μm 工藝節點之前,柵氧厚度一般降低到上一工藝節點的0.7倍左右。到 90nm階段,柵氧厚度的降低變得緩慢,這是為了避免柵極漏電流(gate leakage)的急劇增大。而從 90nm 技術節點到65nm 技術節點,柵氧的厚度基本沒有改變,也是出于同樣的原因。然后,在45nm 技術節點,奇異的是,其電學柵氧厚度繼續降低,同時柵極漏電流也顯著減小。這是為什么呢?

提高電容的另外一個辦法是提高介電層的介電常數,這樣就可以提高柵介質材料的物理厚度,以限制柵極漏電流,同時其有效柵氧厚度(EOT)能夠做到很薄,以對 FET通道有足夠的控制、維持或提高性能。在 45nm 之前,工業界通過將柵氧化層部分氮化,以提高柵極電容,并降低漏電流。氮化硅跟已有的工藝比較兼容,但是其k值提高的幅度有限。而當尺寸需要進一步降低時候,就需要引入高k柵介電材料。

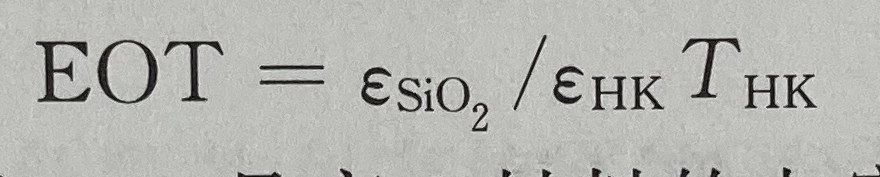

高k介電材料的物理厚度和其EOT 之間的關系如下

上式中,THK是高k材料的物理厚度,εHK 是高k材料的電容率,它與介電常數k呈正比關系。由于εHk 遠遠大于εSiO2,在降低 EOT 的同時,高k材料的物理厚度獲得大幅度提升。英特爾公司的45nm 技術已經采用該技術,并已經進入量產階段。

高k材料的選擇,需要綜合考慮介電常數和漏電的要求。高k介質在硅上必須具有熱動力穩定性,它們必須具有最小的高k/Si界面態,并為NMOS和PMOS 器件提供專門的功函數。為實現批量生產,還必須滿足動態要求和刻蝕選擇性標準。綜上所述,以元素鉿為基礎的介電層材料成為首選。給的系列材料包括:可以用于微處理器等高性能電路的鉿氧化物(HfO2,k~25);用于低功耗電路的鉿硅酸鹽/鉿硅氧氮化合物(HfSiO/HfSiON,k~15)。

-

集成電路

+關注

關注

5460文章

12631瀏覽量

375293 -

電容

+關注

關注

100文章

6502瀏覽量

159839 -

MOS

+關注

關注

32文章

1752瀏覽量

101049

原文標題:等效柵氧厚度的微縮

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

3300V SiC MOSFET柵氧可靠性研究

什么是MOSFET柵極氧化層?如何測試SiC碳化硅MOSFET的柵氧可靠性?

未來推動芯片尺寸微縮的五種技術

MOSFET柵漏電流噪聲特性、模型的特性和局限性研究分析

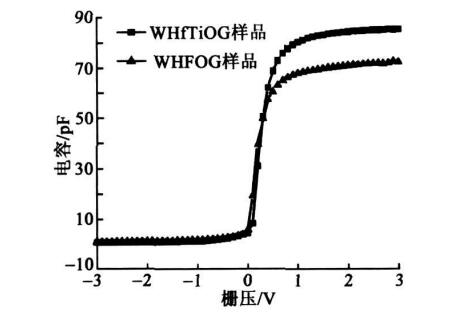

一文讀懂HfTiO高柵介質GeMOS電容

AEC---SiC MOSFET 高溫柵氧可靠性研究

高k柵介質NMOSFET遠程聲子散射對溝道遷移率的影響

vdmos器件厚度對電阻的影響

集成電路制造工藝中的偽柵去除技術介紹

等效柵氧厚度的微縮

等效柵氧厚度的微縮

評論