1.RDMA 傳輸系統(tǒng)架構(gòu)設計目的

隨著數(shù)據(jù)中心對于網(wǎng)絡帶寬和延遲的要求日益增長,傳統(tǒng)的 TCP/IP 網(wǎng)絡已無法滿足性能要求, RDMA 網(wǎng)絡則憑借其高帶寬、低延時的特性脫穎而出錯誤!未找到引用源。相較于傳統(tǒng) TCP/IP 協(xié)議, RDMA 具有零拷貝、不需要 CPU 接入、消息基于事務等特點。

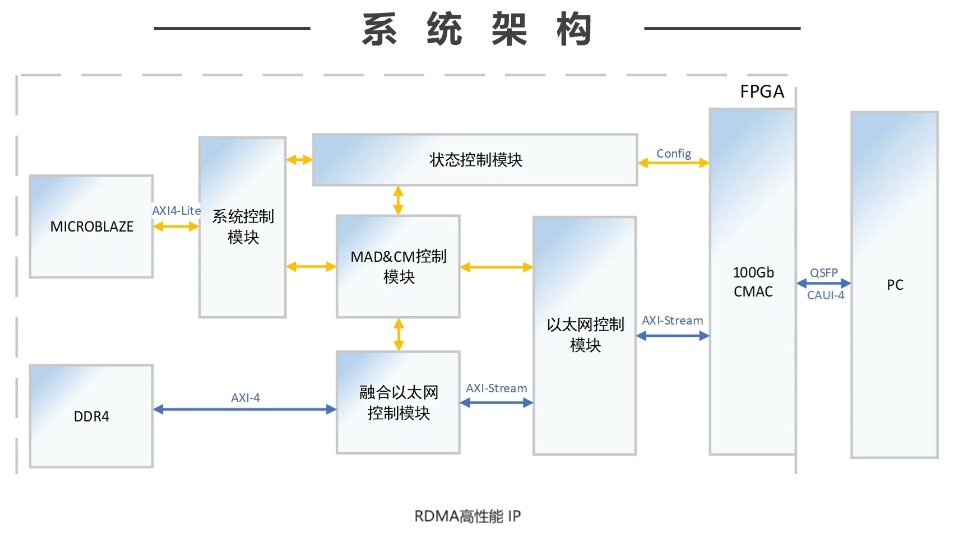

該系統(tǒng)架構(gòu)主要解決適合于FPGA端的RDMA傳輸。它支持FPGA之間,F(xiàn)PGA與PC之間高速通信。只需一根光纖(當然,PC端需要轉(zhuǎn)接卡,將光纖轉(zhuǎn)入PC端,例如100G的CX455A-ECAT 100Gbe網(wǎng)卡 就可以)。它注重通用性強,性能優(yōu)越,非私有化協(xié)議設計,以便用戶后續(xù)升級或更換IP。

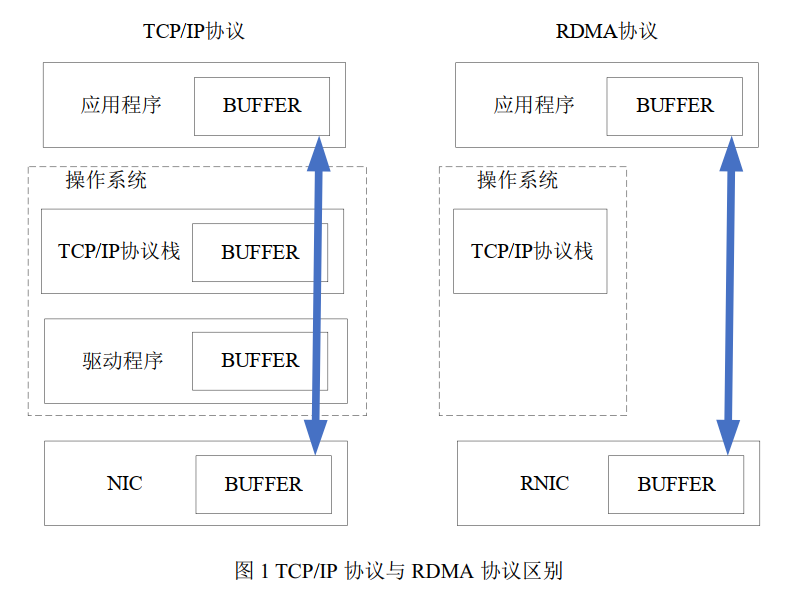

2. RDMA 協(xié)議與傳統(tǒng) TCP/IP 協(xié)議在通信過程中的區(qū)別

如圖 1 所示,左側(cè)部分為傳統(tǒng) TCP/IP 協(xié)議的通信過程,首先使操作系統(tǒng)進入內(nèi)核態(tài),而后傳輸?shù)臄?shù)據(jù)通過 BUFFER 拷貝進 TCP/IP 協(xié)議棧進行組包處理,而后通過網(wǎng)卡(NIC)驅(qū)動下發(fā)到網(wǎng)卡內(nèi)的 BUFFER。右側(cè)部分則為 RDMA 協(xié)議的通信過程,其將 RDMA 協(xié)議部署在融合以太網(wǎng)卡(RNIC)上,在對數(shù)據(jù)包的組裝和拆解過程中,不需要 CPU 及操作系統(tǒng)介入干預,也不需要進行內(nèi)存拷貝操作。當發(fā)送數(shù)據(jù)包時,直接由應用程序通知網(wǎng)卡要發(fā)送的數(shù)據(jù)在內(nèi)存中的起始地址及數(shù)據(jù)長度,而后 RNIC 則讀取其已經(jīng)在內(nèi)存中注冊好的區(qū)域數(shù)據(jù)并依照協(xié)議規(guī)范進行數(shù)據(jù)包的組裝及傳輸。

3.系統(tǒng)架構(gòu)如圖2:

圖2 系統(tǒng)架構(gòu)圖

對IP的簡單控制由Microblaze完成,DDR負責讀寫等數(shù)據(jù)緩存。該架構(gòu)也可以換成zynq的arm控制,便于后續(xù)NVMe oF開發(fā)。

視頻可以搜B站 用戶名: 專注與守望

4測試

在xilinx開發(fā)平臺測試,網(wǎng)卡支持100G,選用的是CX455A-ECAT 100Gbe。該IP支持 RoCE V2。實測數(shù)據(jù):

SEND71Gbps

READ91 Gbps(PC端給FPGA發(fā)包,受PC性能限制多一點)

WRITE 96 Gbps

審核編輯 黃宇

-

FPGA

+關(guān)注

關(guān)注

1662文章

22469瀏覽量

638123 -

內(nèi)存

+關(guān)注

關(guān)注

9文章

3222瀏覽量

76450 -

傳輸系統(tǒng)

+關(guān)注

關(guān)注

0文章

164瀏覽量

38151 -

RDMA

+關(guān)注

關(guān)注

0文章

99瀏覽量

9651

發(fā)布評論請先 登錄

GT-BGA-2003高性能BGA插座

國產(chǎn)高性能ONFI IP解決方案全解析

2025年高性能音頻傳輸模塊選購指南與應用方案推薦

高性能網(wǎng)絡存儲設計:NVMe-oF IP的實現(xiàn)探討

GT-BGA-2002高性能BGA測試插座

AMD UltraScale架構(gòu):高性能FPGA與SoC的技術(shù)剖析

Xilinx高性能低延時8通道PCIe-DMA控制器IP,SGDMA,QDMA,CDMA,RDMA, V4L2驅(qū)動,高速視頻采集, 高速AD采集

基于DSP與FPGA異構(gòu)架構(gòu)的高性能伺服控制系統(tǒng)設計

高性能 RDMA 傳輸系統(tǒng):通用性及高性能架構(gòu)考慮

高性能 RDMA 傳輸系統(tǒng):通用性及高性能架構(gòu)考慮

評論