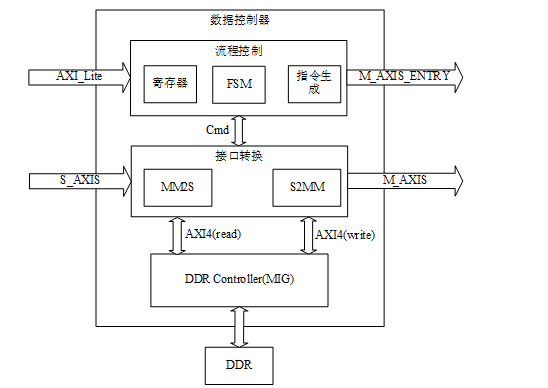

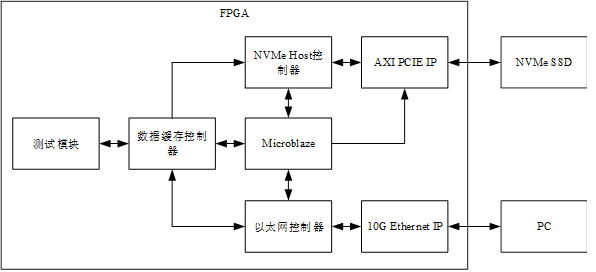

數(shù)據(jù)緩存控制器主要實現(xiàn)了對大量突發(fā)數(shù)據(jù)的緩存、AXI4接口與AXI4-Stream接口之間的轉(zhuǎn)換和NVMe命令的生成等功能。數(shù)據(jù)緩存控制器的整體架構(gòu)如圖1所示。

圖1數(shù)據(jù)緩存控制器整體架構(gòu)

根據(jù)功能需求將數(shù)據(jù)緩存控制器劃分為了3個模塊:流程控制模塊、接口轉(zhuǎn)換模塊和MIG模塊。

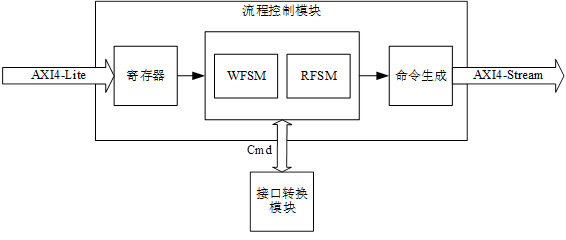

(1)流程控制模塊:流程控制模塊主要實現(xiàn)三個功能,一是根據(jù)用戶命令或輸入的數(shù)據(jù)量大小來組裝相應(yīng)的NVMe提交命令,并發(fā)送至NVMe Host控制器;二是控制接口轉(zhuǎn)換模塊工作的開啟與關(guān)閉;三是實現(xiàn)乒乓操作,來提高系統(tǒng)傳輸性能。

(2)接口轉(zhuǎn)換模塊:接口轉(zhuǎn)換模塊負責完成將DDR控制器的AXI4接口轉(zhuǎn)換為與其他模塊進行數(shù)據(jù)交互的AXI4-Stream接口。

(3)MIG模塊:MIG模塊是Xilinx提供的DDR存儲控制器,可以幫助用戶快速的搭建工程,完成對DDR等外部存儲器的控制。MIG IP核內(nèi)部由用戶接口、存儲控制器和物理層模塊三部分組成。同時MIG IP還支持AXI4接口,用戶可以直接通過AXI4接口訪問DDR存儲器。

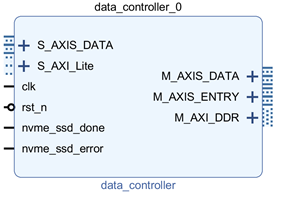

如圖2所示,它為數(shù)據(jù)緩存控制器的頂層模塊框圖。

圖2 數(shù)據(jù)緩存控制器的頂層模塊框圖

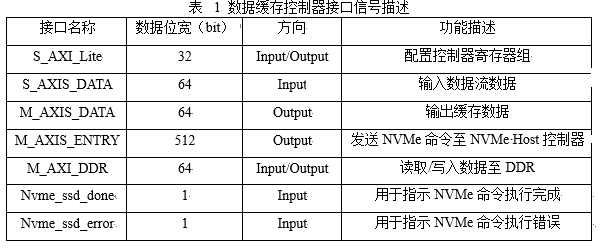

數(shù)據(jù)緩存控制器的外部接口信號主要包括與Microblaze處理器、NVMe Host控制器、以太網(wǎng)控制器、外部DDR存儲器相連接的端口。其中AXI4_Lite接口用于配置數(shù)據(jù)緩存控制器的寄存器;M_AXIS_ENTRY接口用于向NVMe Host控制器發(fā)送NVMe命令;S_AXIS_DATA接口用于接收輸入的數(shù)據(jù)流數(shù)據(jù);M_AXIS_DATA接口用于輸出的緩存數(shù)據(jù);M_AXI_DDR用于讀寫DDR內(nèi)緩存的數(shù)據(jù);NVMe_Done信號用于指示命令執(zhí)行成功;NVMe_Error信號用于指示命令執(zhí)行錯誤。

數(shù)據(jù)緩存控制器的頂層接口信號定義如表1所示。

對相關(guān)視頻感興趣者請看B站。搜用戶名:專注與守望

審核編輯 黃宇

-

控制器

+關(guān)注

關(guān)注

114文章

17822瀏覽量

194291 -

SSD

+關(guān)注

關(guān)注

21文章

3124瀏覽量

122327 -

存儲系統(tǒng)

+關(guān)注

關(guān)注

2文章

433瀏覽量

41926 -

數(shù)據(jù)緩存

+關(guān)注

關(guān)注

0文章

25瀏覽量

7408

發(fā)布評論請先 登錄

如何突破AI存儲墻?深度解析ONFI 6.0高速接口與Chiplet解耦架構(gòu)

憶聯(lián)發(fā)布新款企業(yè)級SATA SSD UM311d

基于FPGA的DDR控制器設(shè)計

SSD為何需要DRAM緩存?天碩工業(yè)級SSD帶來深度解析!

NAS存儲系統(tǒng)斷電風險大?UPS電源守護數(shù)據(jù)安全刻不容緩

PCIe協(xié)議分析儀能測試哪些設(shè)備?

高性能存儲控制器的技術(shù)解析

Ceph分布式存儲系統(tǒng)解析

半導(dǎo)體存儲芯片核心解析

NVME控制器之隊列管理模塊

NVME控制器之指令控制模塊設(shè)計

27MHz HCSL 差分晶體振蕩器在數(shù)據(jù)中心網(wǎng)絡(luò)存儲系統(tǒng)中的應(yīng)用方案

高速ssd存儲系統(tǒng)中數(shù)據(jù)緩存控制器流程控制設(shè)計

高速SSD存儲系統(tǒng)中數(shù)據(jù)緩存控制器整體頂層設(shè)計

高速SSD存儲系統(tǒng)中數(shù)據(jù)緩存控制器整體頂層設(shè)計

評論