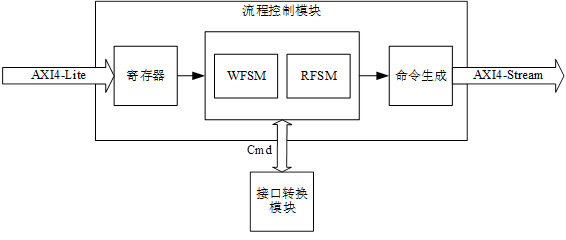

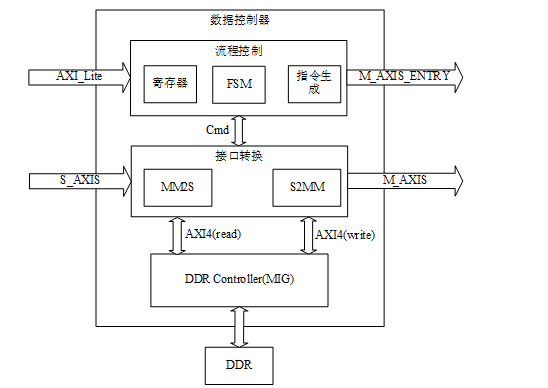

流程控制模塊的框圖如圖1所示,該模塊主要由寄存器、讀狀態機、寫狀態機和命令生成模塊組成。

圖1 流程控制模塊框圖

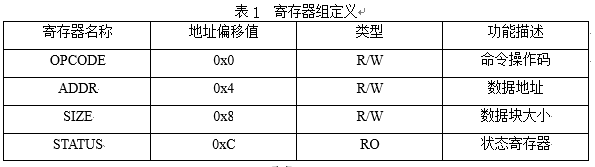

流程控制模塊的工作首先從配置模塊中的寄存器組開始,由于只需要配置四個寄存器,因此使用資源占用較小的AXI_Lite總線接口來實現。表1所示為流程控制模塊內寄存器的類型與功能描述等信息。

表1中的操作碼寄存器(OPCODE)用于表示命令類型,流程控制模塊通過操作碼寄存器不同的值來組裝相應的NVMe命令,本設計主要實現了NVMe協議中常用的識別、讀、寫、SMART、FLUSH以及關機命令。數據地址寄存器(ADDR)用于指定要讀取的數據塊的起始地址。數據塊大小寄存器(SIZE)用于指定要讀取的數據塊的大小。狀態寄存器(STATUS)為只讀狀態,用來指示當前控制器的狀態信息。

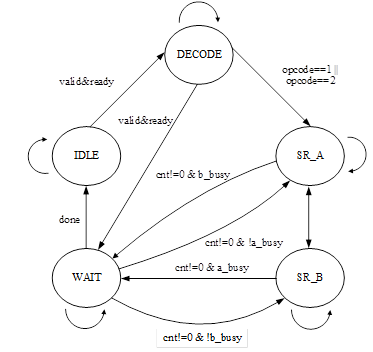

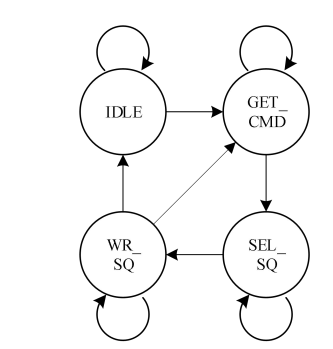

為了提升系統性能,將讀寫劃分為兩個傳輸通道,每個通道可獨立工作。因此需要通過兩個狀態機來實現了讀寫控制。同時,采用乒乓操作的方式進行讀寫,通過A和B兩個緩存區之間的切換來使輸入輸出數據可以無間斷地進行傳輸,并減小NVMe命令執行過程中產生的延遲。

讀狀態機跳轉圖如圖2所示。

圖2 狀態機跳轉圖

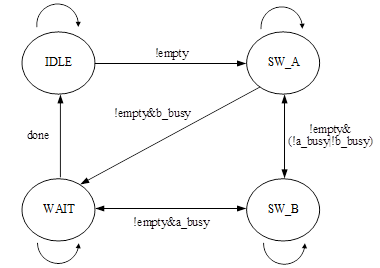

寫狀態機跳轉圖如圖3所示。

圖3 寫狀態機跳轉圖

各狀態說明如下:

IDLE:空閑狀態,該狀態為該模塊上電后的初始化狀態,在該狀態下等待接口轉換模塊輸入的empty信號為低電平時,表示有數據輸入,狀態跳轉至SW_A狀態,否則維持在IDLE狀態。

SW_A:發送A區域寫命令狀態,該狀態下等待緩存區域A存滿后,控制命令生成模塊組裝區域A的NVMe寫命令并通過AXI4_Stream接口發送給NVMe Host控制器。發送完成后若b_busy信號有效且empty信號為低電平時,狀態跳轉至WAIT,若b_busy信號為低電平且empty信號為低電平時,狀態跳轉至SC_B狀態,此外,在設計中還添加了超時檢測機制,通過計數器實現,當長時間無數據輸入時,則控制命令生成模塊組裝相應大小的NVMe寫命令,發送至NVMe Host控制器。

SW_B:發送B區域寫命令狀態,該狀態下根據接口轉換模塊輸入的轉換數據量信息生成相應的NVMe寫命令并通過AXI4_Stream接口發送給NVMe Host控制器。發送完成后若a_busy信號有效且empty信號為低電平時,狀態跳轉至WAIT,若a_busy信號為低電平且empty信號為低電平時,狀態跳轉至SC_A狀態,該狀態下同樣使用超時檢測。

WAIT:等待狀態,在該狀態下等待NVMe Host控制器返回done信號,表示命令執行完畢。若上一個狀態為SW_A,檢測到done信號有效后,且buf_cnt的值不為0,則狀態跳轉至SW_B。若上一個狀態為SW_B,檢測到done信號有效后,且buf_cnt的值不為0,則狀態跳轉至SW_A。否則狀態跳轉至IDLE。

對它感興趣,想看視頻搜B站用戶名: z專注與守望

審核編輯 黃宇

-

控制器

+關注

關注

114文章

17787瀏覽量

193079 -

SSD

+關注

關注

21文章

3109瀏覽量

122221 -

存儲系統

+關注

關注

2文章

433瀏覽量

41891

發布評論請先 登錄

基于FPGA的DDR控制器設計

遠程控制器:4-32 路繼電器控制 + 數據采集,WiFi 通訊打破空間限制

宏集方案 | 如何選擇適合您的過程控制器?

高速ssd存儲系統中數據緩存控制器流程控制設計

高速ssd存儲系統中數據緩存控制器流程控制設計

評論