低噪聲放大器(LNA)設計概念

基本定義?

低噪聲放大器(Low Noise Amplifier, LNA)是射頻接收鏈路前端的關鍵放大模塊,其核心功能是在放大微弱射頻信號時,最大限度保持信號完整性,同時抑制附加噪聲的引入。

設計目標?

2.1 核心性能指標?

噪聲系數最小化

高增益性能

線性度優化

輸入/輸出匹配網絡設計

低功耗控制

2.2 關鍵性能參數?

噪聲系數:典型值<2 dB

增益范圍:15-25 dB

1dB壓縮點指標

輸入/輸出回波損耗參數

穩定性系數

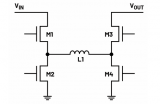

典型電路拓撲?

3.1 共源級放大器?

結構簡單

增益較高

噪聲性能較優

3.2 共柵級放大器?

輸入阻抗匹配特性突出

低噪聲系數

穩定性良好

3.3 級聯架構?

多級聯調設計

噪聲與增益性能均衡

電路復雜度增加

設計關鍵技術?

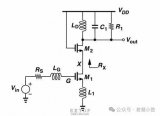

4.1 噪聲匹配?

源端阻抗優化配置

等效輸入噪聲最小化

噪聲圓圖分析方法

4.2 穩定性設計?

寄生振蕩抑制技術

無條件穩定性實現

反饋網絡優化設計

4.3 偏置電路?

靜態工作點精確設定

溫度補償機制

電流鏡偏置方案

設計優化方法?

5.1 工藝選擇?

CMOS工藝

SiGe工藝

GaAs工藝

工藝參數對噪聲系數、增益的影響分析

5.2 版圖設計?

寄生電容/電感抑制

對稱性布局設計

電磁屏蔽與信號隔離

應用場景?

無線通信接收機

衛星通信前端

雷達信號處理系統

傳感器信號調理接口

移動通信基帶電路

審核編輯 黃宇

-

電路設計

+關注

關注

6741文章

2700瀏覽量

219498 -

LNA

+關注

關注

4文章

342瀏覽量

59852

發布評論請先 登錄

LNA-20-01000200-08-10P低噪聲放大器

探索MAX2667/MAX2669:GPS/GNSS超低噪聲系數LNA的卓越之選

功放PCB電路板設計:從噪聲抑制到音質優化

MDD 邏輯IC的功耗管理與優化策略

石墨電極電阻率測定儀中低噪聲放大電路的關鍵設計

電源噪聲的來源與應對策略

輪轂電機HEV能量管理策略優化研究

如何抑制電子電路中的噪聲

RakSmart服務器成本優化策略

芯知識|語音芯片(以廣州唯創電子WT588F02B為例)底噪聲優化指南

解決電路噪聲難題:《電路噪聲防護與優化設計技術白皮書》工程師必備的全面指南

MAX2676帶有天線開關和偏置的GPS/GNSS LNA技術手冊

LNA電路設計及噪聲優化策略

LNA電路設計及噪聲優化策略

評論