隨著數字電路設計的復雜度不斷提升,功耗管理成為了系統設計中不可忽視的重要議題。尤其是在移動設備、消費電子、嵌入式系統等領域,如何降低功耗以提高能源效率和延長電池壽命,已成為設計過程中關鍵的考慮因素之一。對于MDD辰達半導體 邏輯IC(集成電路)而言,合理的功耗管理不僅能提升系統性能,還能有效延長設備的使用壽命。因此,作為FAE,在客戶的設計過程中,協助優化功耗管理是一項重要任務。

一、邏輯IC的功耗類型

邏輯IC的功耗主要可以分為三種類型:

靜態功耗(靜態電流)

靜態功耗指的是當邏輯IC處于不活動狀態時,仍然消耗的電流。它主要由漏電流引起,隨著技術節點的不斷縮小,靜態功耗逐漸成為主要的功耗來源。盡管靜態功耗相對較小,但在長期使用中,累計的功耗不可忽視。

動態功耗(開關功耗)

動態功耗是由于邏輯IC在切換狀態時,輸入輸出端的電容充放電所產生的功耗。它與切換頻率、輸入信號的幅度以及電源電壓的大小直接相關。通常,系統的工作頻率越高,動態功耗越大。

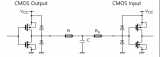

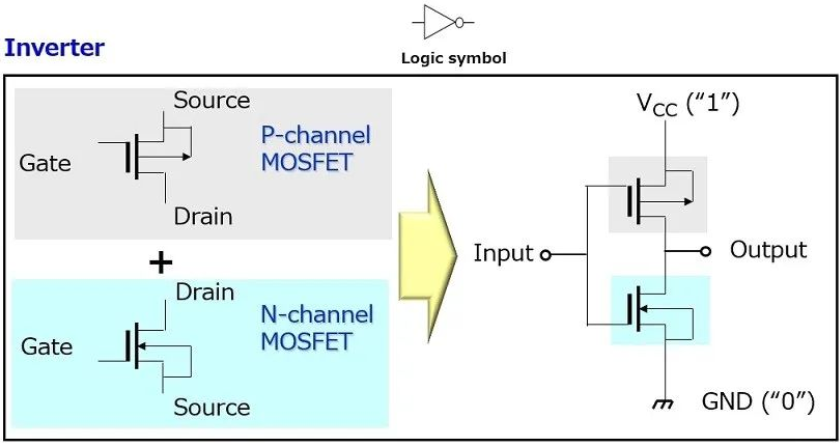

短路功耗

當電路中的PMOS和NMOS同時導通時,會產生短路電流,導致短路功耗。短路功耗主要發生在開關瞬間,尤其在邏輯門切換頻繁的電路中較為明顯。

二、影響功耗的主要因素

工作頻率

工作頻率是影響動態功耗的一個重要因素。系統的工作頻率越高,單位時間內的開關次數越多,導致動態功耗增大。因此,在高速電路設計中,功耗控制尤為關鍵。

電源電壓

電源電壓與功耗之間有著密切的關系。功耗與電壓的平方成正比(P = C * V2 * f),因此,降低電源電壓可以有效減少功耗。但需要注意的是,電壓的降低可能會影響到邏輯電路的性能和穩定性。

電容大小

電路中輸入輸出端的電容越大,切換時所消耗的能量越多,導致功耗增加。尤其是在高速信號傳輸中,電容效應顯著,優化電路中的電容大小對于降低功耗至關重要。

技術節點

隨著工藝節點的縮小,器件的漏電流增加,導致靜態功耗增加。不同工藝節點的功耗特性不同,設計時需要根據實際應用選擇合適的工藝。

三、功耗管理的優化策略

降低工作頻率

降低系統的工作頻率是減少動態功耗的一種有效方法。通過減少不必要的時鐘頻率,尤其是在非高性能要求的時段,能夠顯著降低功耗。例如,可以使用動態頻率調節(Dynamic Frequency Scaling,DFS)技術,在負載較低時自動降低頻率。

采用低功耗邏輯IC

市面上有許多專門設計用于低功耗應用的邏輯IC系列,例如低功耗CMOS(Low-Power CMOS)系列、超低功耗(ULP)系列等。這些邏輯IC通過優化設計來減少漏電流,特別適用于電池供電的設備。

采用動態電壓調節(DVS)技術

動態電壓調節(DVS)是通過根據系統負載動態調整電源電壓來減少功耗。在高負載時,系統提供較高的電壓,以保證性能;在低負載時,系統降低電壓,以降低功耗。DVS技術能夠有效平衡性能與功耗之間的關系。

優化時序與數據傳輸路徑

減少不必要的信號切換是降低動態功耗的關鍵。優化時序設計、使用高效的信號編碼方式(如壓縮編碼)和減少數據路徑長度,都有助于減少切換次數,從而降低功耗。

靜態功耗管理

對于靜態功耗,可以通過降低漏電流來進行管理。在設計時,選擇適當的工藝節點和器件類型,采用多閾值CMOS(Multi-threshold CMOS)技術,能夠有效減小漏電流。此外,使用動態電源管理技術,可以在電路不活動時將其進入低功耗模式,從而減少靜態功耗。

時鐘門控(Clock Gating)技術

時鐘門控技術可以在電路不活動時關閉時鐘信號,減少不必要的開關活動,降低功耗。這種技術特別適用于寄存器文件、時鐘樹等部分,能夠顯著降低系統的動態功耗。

四、FAE優化建議

選擇合適的電源電壓和頻率

在設計過程中,合理選擇系統的電源電壓和工作頻率是功耗管理的基礎。盡量采用低電壓設計,并根據負載情況動態調節頻率和電壓,以平衡性能和功耗。

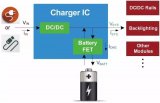

監測功耗并進行動態調節

實現對系統功耗的實時監測和動態調節是功耗優化的重要步驟。可以通過集成的功耗管理芯片或嵌入式傳感器來實時監測系統的功耗,進一步調整策略。

適當的去耦和電源濾波

電源噪聲對功耗的影響不可忽視,使用適當的去耦電容和電源濾波技術,能夠有效穩定電源電壓,減少不必要的功耗浪費。

邏輯IC的功耗管理不僅僅是降低功耗那么簡單,它涉及到設計、工藝、時序以及電源等多個方面。通過合理選擇邏輯IC、優化工作頻率、采用低功耗設計技術,以及采用動態電壓和時鐘管理策略,能夠有效地降低功耗,提高系統的能效和穩定性。作為FAE,在幫助客戶解決功耗管理問題時,應提供全面的支持,確保設計中的功耗優化策略得以實現,最終達到最佳的系統性能和效能。

-

電路設計

+關注

關注

6744文章

2719瀏覽量

219856 -

功耗管理

+關注

關注

0文章

10瀏覽量

7292 -

邏輯IC

+關注

關注

0文章

38瀏覽量

7034

發布評論請先 登錄

輪轂電機HEV能量管理策略優化研究

MCU時鐘管理對功耗優化方向

請問如何優化芯片的功耗管理?

淺談IC設計中邏輯綜合

IC芯片功耗有哪些降低方法?

可穿戴系統電源管理的優化策略

Linux系統的性能優化策略

一種基于全局級模糊邏輯的功率管理策略

MDD 邏輯IC的邏輯電平不兼容問題與解決方案

MDD 邏輯IC的功耗管理與優化策略

MDD 邏輯IC的功耗管理與優化策略

評論