在追求更快、更穩(wěn)的無線通信路上,傳統(tǒng)射頻架構(gòu)深陷帶寬-功耗-成本的“不可能三角”:帶寬每翻倍,系統(tǒng)復雜度與功耗增幅遠超線性增長。傳統(tǒng)方案通過“分立式功放+多級變頻鏈路+JESD204B 接口”的組合試圖平衡性能與成本,卻難以滿足實時性嚴苛的超大規(guī)模 MIMO 通信等場景需求。

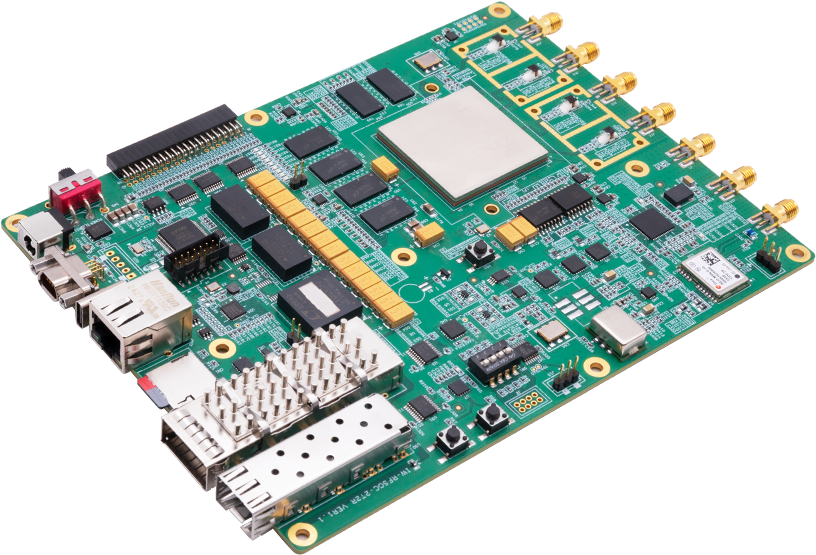

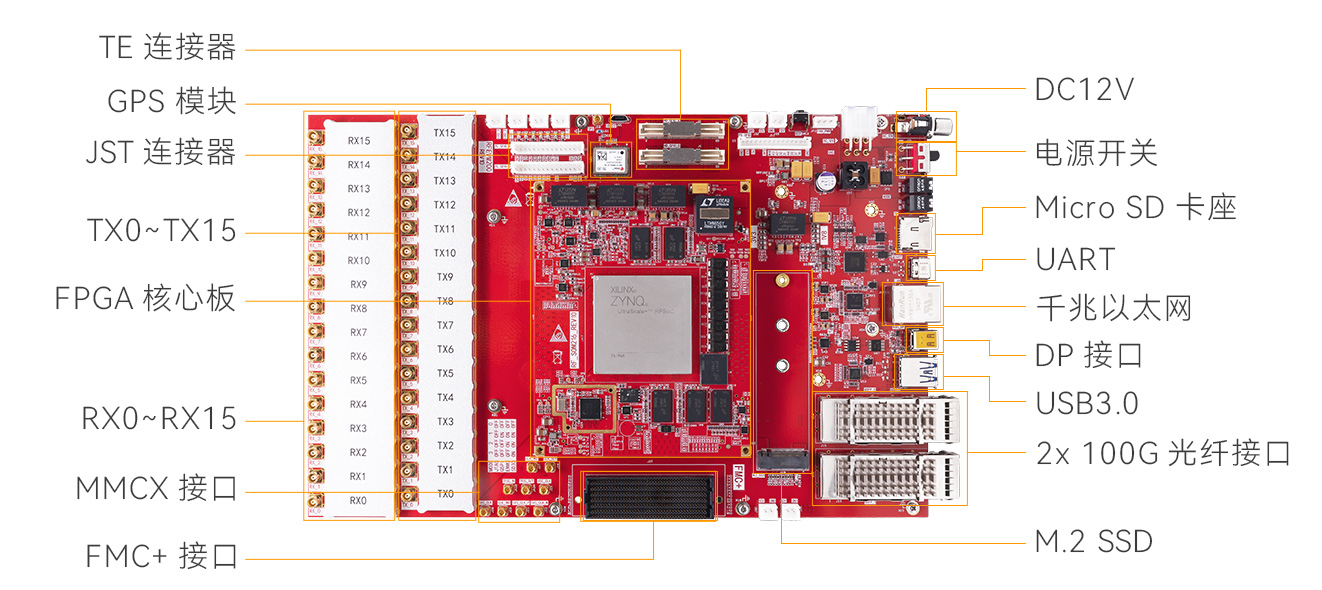

在此背景下,AXW49射頻開發(fā)板以“直采+異構(gòu)”重構(gòu)射頻范式:

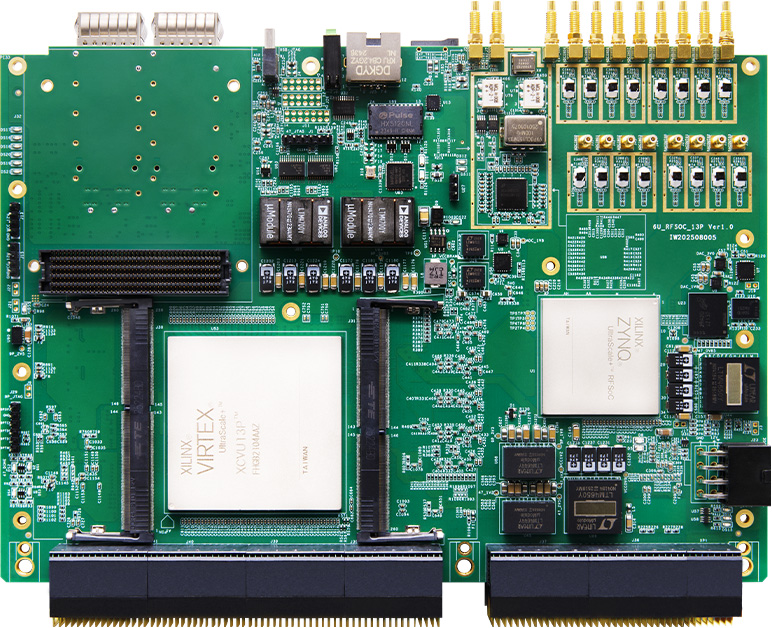

基于AMD Zynq UltraScale+? RFSoC Gen3XCZU49DR芯片的 16 通道 14 位 2.5GSPS ADC 與 16 通道 14 位 9.85GSPS DAC,實現(xiàn)全數(shù)字域直接射頻采樣,消除 JESD204B 接口延遲;

通過集成Kontron X86 COME模塊,構(gòu)建“FPGA 實時+ARM 控制+X86 協(xié)議棧處理”的三級流水線,為高性能射頻信號處理/實時嵌入式系統(tǒng)/高速數(shù)據(jù)存儲場景提供“超密度、零妥協(xié)”的優(yōu)化方案。

-核心優(yōu)勢-

直接射頻采樣

簡化信號鏈,突破帶寬限制

通過集成 ADC/DAC 實現(xiàn)直接射頻采樣,消除傳統(tǒng)模擬混頻與 JESD204B 接口,減少模擬鏈路層級,降低系統(tǒng)延遲與功耗。

異構(gòu)計算FPGA+ARM+X86

全棧低延遲處理

AXW49 融合三類計算單元,實現(xiàn)從實時信號處理到智能決策的全棧加速:

FPGA 實時層(PL端)

16 通道并行處理:支持數(shù)字上下變頻(DUC/DDC)、FFT/FIR濾波,時延低至微秒級,滿足 5G 波束賦形、雷達脈沖壓縮等場景需求。

ARM 控制層(APU/RPU)

四核 Cortex-A53(APU)運行Linux,處理協(xié)議棧、設(shè)備管理;

雙核 Cortex-R5(RPU)運行實時操作系統(tǒng)(RTOS),實現(xiàn)硬實時控制。

X86 協(xié)處理層(Kontron 模塊)

通過高速接口與 FPGA 互聯(lián),執(zhí)行大數(shù)據(jù)量后處理。

高密度擴展

面向未來系統(tǒng)的彈性架構(gòu)

- 通道密度:單板 16 路 ADC/DAC 同步采樣,支持多板級聯(lián),適用于相控陣雷達與 Massive MIMO 基站;

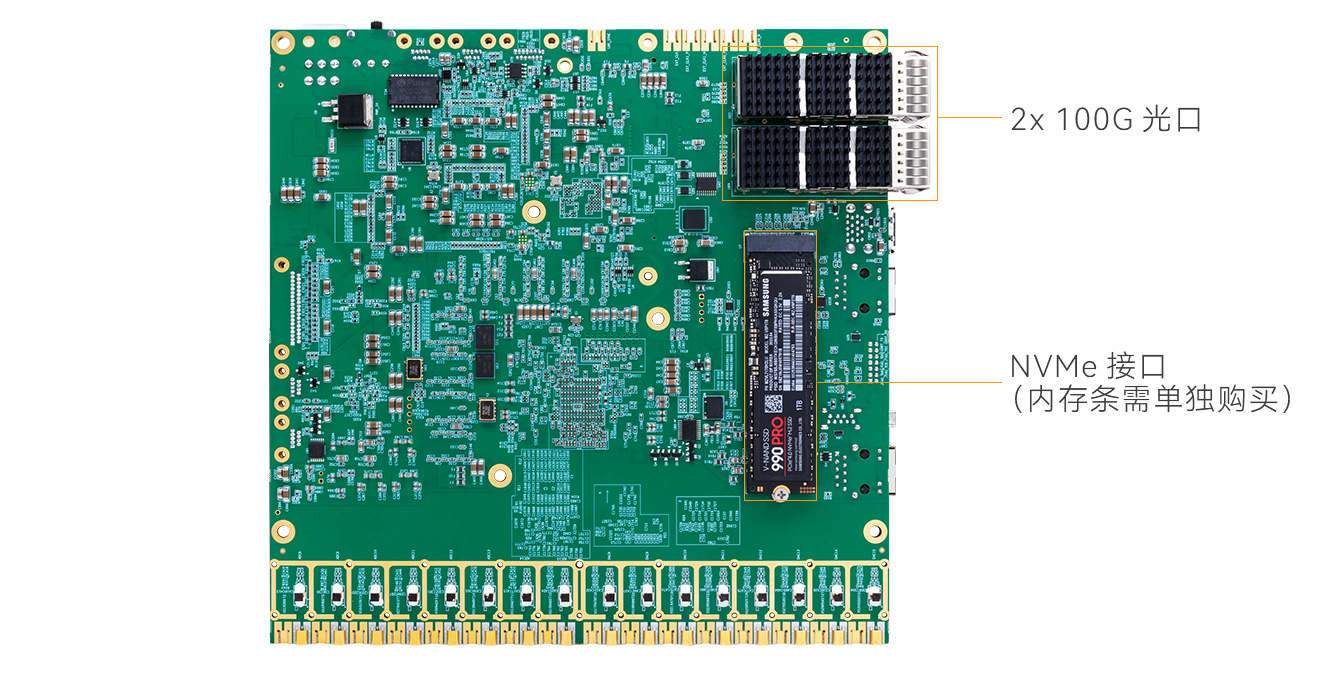

- 數(shù)據(jù)吞吐:雙 100Gbps QSFP28 光口+DDR4+NVMe SSD 分級存儲,實現(xiàn)海量數(shù)據(jù)實時流盤;

- 部署靈活:板載 M.2、SD 卡及多路千兆以太網(wǎng),靈活適配邊緣計算、工業(yè)現(xiàn)場與實驗室研發(fā)。

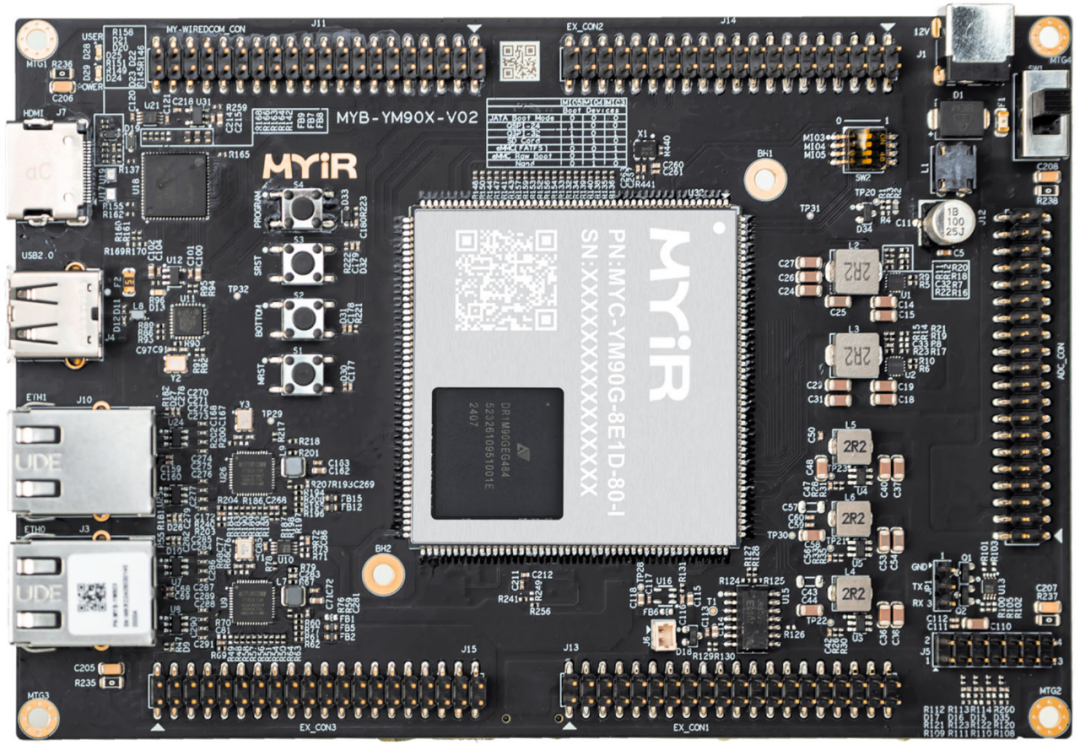

-硬件配置速覽-

主控芯片

基于AMD Zynq UltraScale+ RFSoC Gen3 XCZU49DR,集成可編程邏輯(PL)、四核 ARM Cortex-A53 應用處理單元(APU)、雙核 ARM Cortex-R5 實時處理單元(RPU)。

擴展Kontron X86 COME 協(xié)處理模塊,與 FPGA 協(xié)同,增強通用計算與協(xié)議處理能力。

射頻前端

16 通道 14 位 2.5GSPS ADC+16 通道 14 位 9.85GSPS DAC:直接射頻采樣,支持寬頻信號捕獲。

采用高性能微型 RF 連接器 190-0108-AAD1,確保信號完整性。

存儲系統(tǒng)

內(nèi)存配置:8×DDR4(PS/PL 各 4)、2×1Gb QSPI Flash。

存儲擴展:1×M.2 NVMe、1×SD卡、嵌入式存儲芯片(通過板對板連接器擴展)。

通信與擴展接口

高速光口:2×100 Gbps QSFP28 光口

通用接口:USB3.0(PS 端+U21 擴展)、雙千兆以太網(wǎng)(PS/PL 各 1 路)。

擴展接口:通過 U21 連接器擴展 USB3.0、RJ45、視頻接口。

-典型應用場景-

▲ 5G 通信

Massive MIMO 基站:16 通道實時波束賦形,可實現(xiàn)顯著的占板面積及功耗減少

▲雷達信號處理

滿足更大的應用需求,在預警場景下實現(xiàn)低時延收發(fā),獲得最佳響應時間。

▲衛(wèi)星與儀器測試

利用直接 RF 采樣、高靈活、可重構(gòu)邏輯及軟件可編程性,為信號生成和信號分析構(gòu)建高速度的多功能儀器。

審核編輯 黃宇

-

FPGA

+關(guān)注

關(guān)注

1660文章

22410瀏覽量

636273 -

射頻

+關(guān)注

關(guān)注

106文章

6006瀏覽量

173458 -

RF

+關(guān)注

關(guān)注

66文章

3201瀏覽量

171808 -

RFSoC

+關(guān)注

關(guān)注

0文章

45瀏覽量

3193

發(fā)布評論請先 登錄

RK3506G2新品首發(fā)|微型開發(fā)板只要49!

全方位解析:什么是異構(gòu)開發(fā)板?為什么選GM-3568JHF?

算力躍升!可嵌入整機的 6U VPX 異構(gòu)高性能射頻信號處理平臺 AXW23

基于FPGA開發(fā)板TSP的串口通信設(shè)計

基于FPGA開發(fā)板DE23-Lite的串口通信設(shè)計

璞致電子 UltraScale+ RFSoC 架構(gòu)下的軟件無線電旗艦開發(fā)平臺

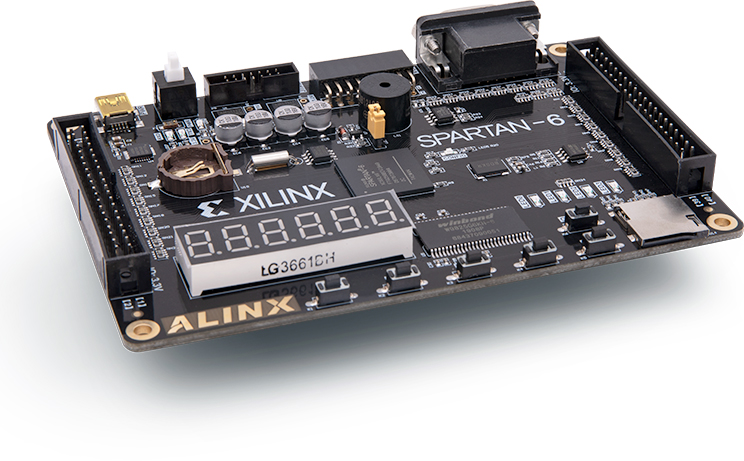

ALINX AMD RFSoC 射頻開發(fā)板選型全攻略!

ALINX AMD RFSoC射頻開發(fā)板選型指南

高性能緊湊型 RFSoC FPGA 開發(fā)平臺 AXW22,重塑射頻開發(fā)體驗

有ARM,NPU,FPGA三種核心的開發(fā)板 — 米爾安路飛龍派開發(fā)板

【干貨分享】:開源小巧的FPGA開發(fā)板——Icepi Zero

一板多能,AXRF49 定義新一代 RFSoC FPGA 開發(fā)平臺

ZU+RFSoC之RFDC API介紹和使用

是德示波器在射頻信號調(diào)制分析中的應用

直采+異構(gòu),看 RFSoC FPGA 開發(fā)板 AXW49 如何應對射頻信號處理高要求

直采+異構(gòu),看 RFSoC FPGA 開發(fā)板 AXW49 如何應對射頻信號處理高要求

評論