“每個公司都會有 PCB 設計規范,包括板層、設計規則等基本的要求。在 KiCad 中如何繼承、管理這些設計規范呢?”

電路板設置

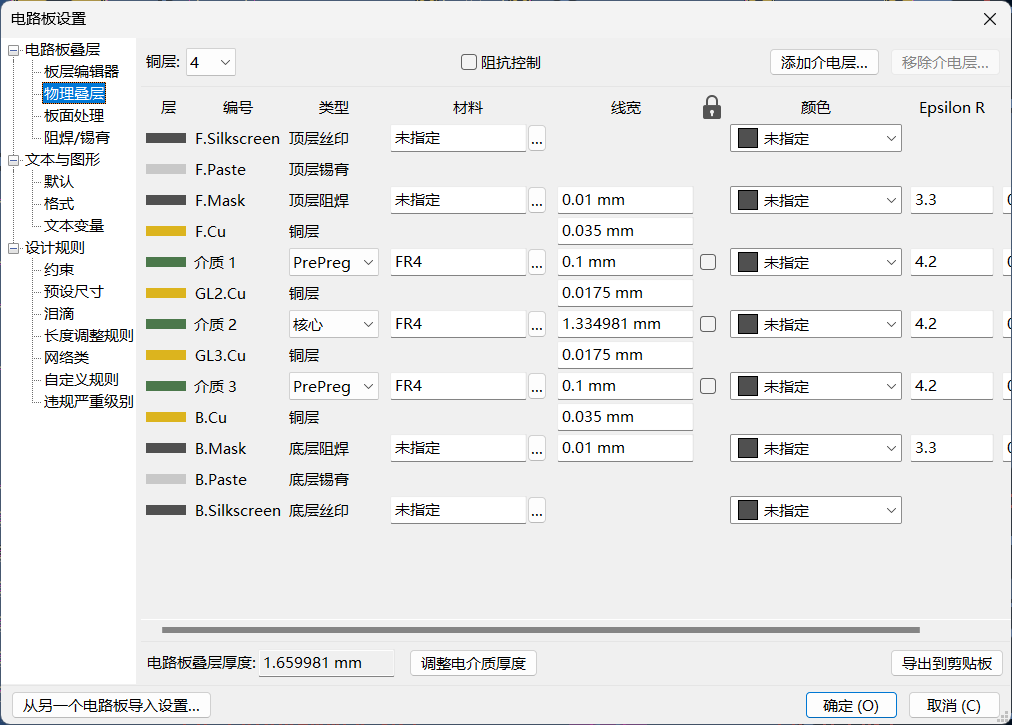

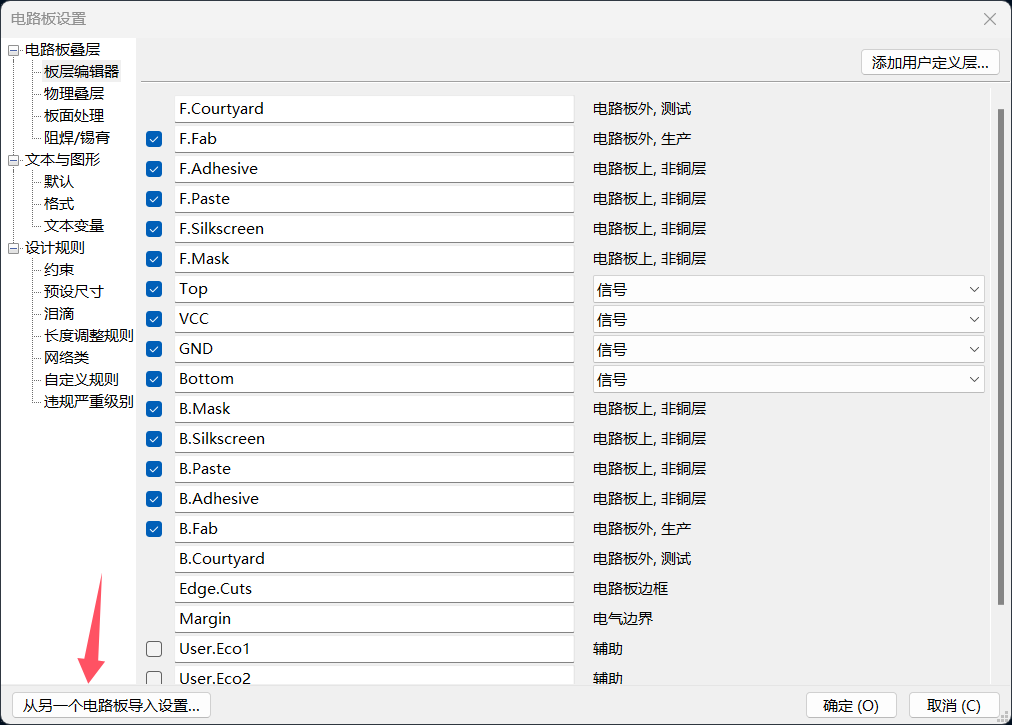

我們先看下工程師必須關心的一些設置。打開電路板設置查看:

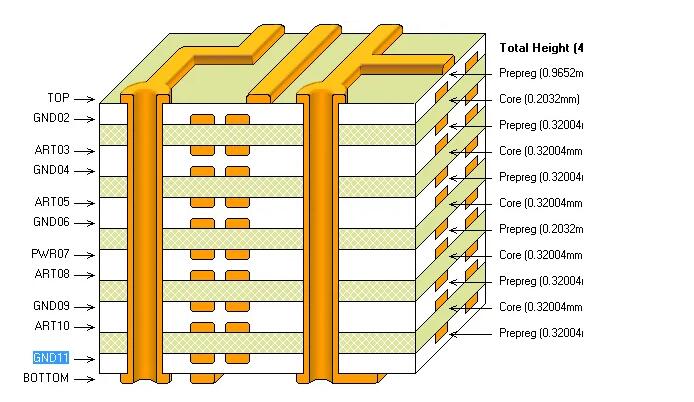

物理疊層 首先需要關注的是“物理層疊”。在這里,你要選擇 PCB 的層數及層疊結構;如果需要做阻抗,還需要關注 Core 和 Prepreg 的 厚度:

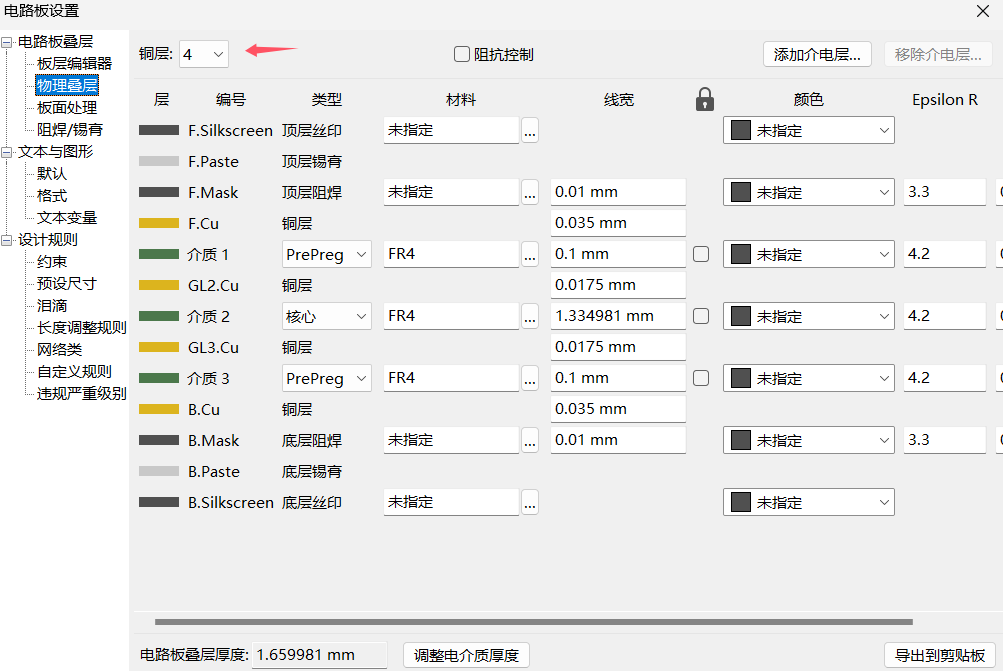

最下方會計算出層疊的總厚度。注意,這一厚度應與板廠常規使用的厚度吻合,比如 1.0mm,1.2mm,1.6mm,2.0mm等。 板層編輯器 再看一下板層編輯器,在這里您可以修改層的名字,如果你習慣了AD的叫法,可以把 F.Cu/B.Cu 改成 Top/Bottom。

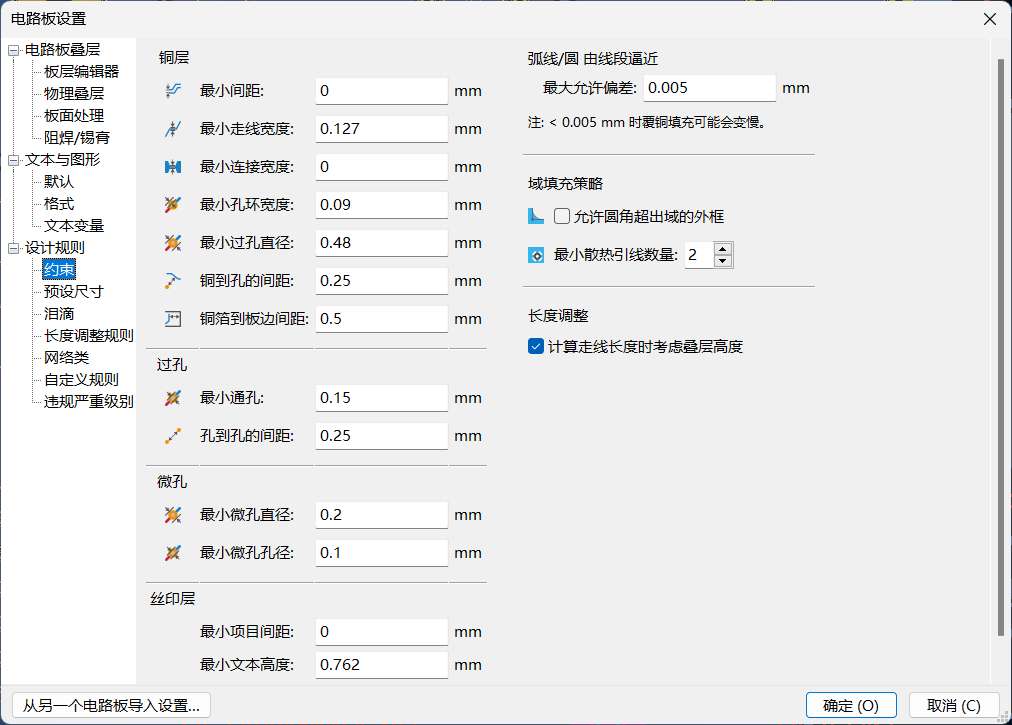

設計規則(約束)

在設計規則的約束頁面,定義了通用的規則,比如線寬/線距,各種孔的尺寸、板邊距等規則。

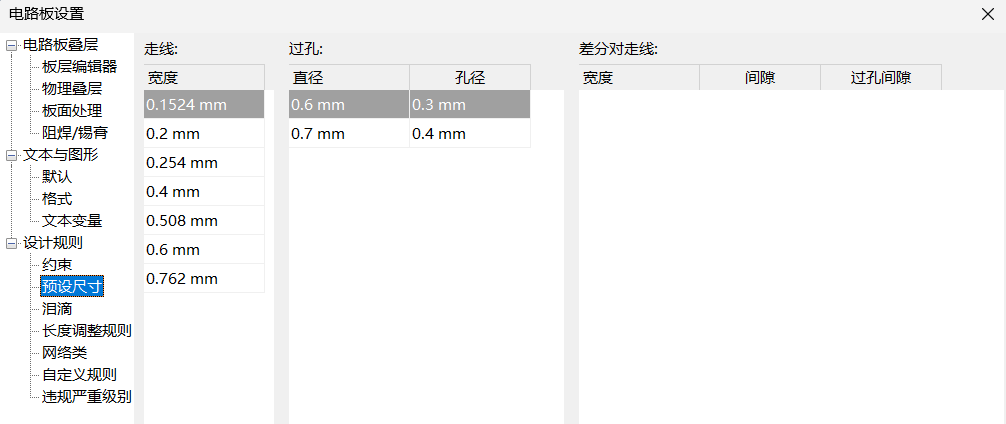

預設尺寸

預設尺寸中可以定義常用的線寬、過孔以及差分對的尺寸:

定義完成后可以在走線時直接選用,非常方便:

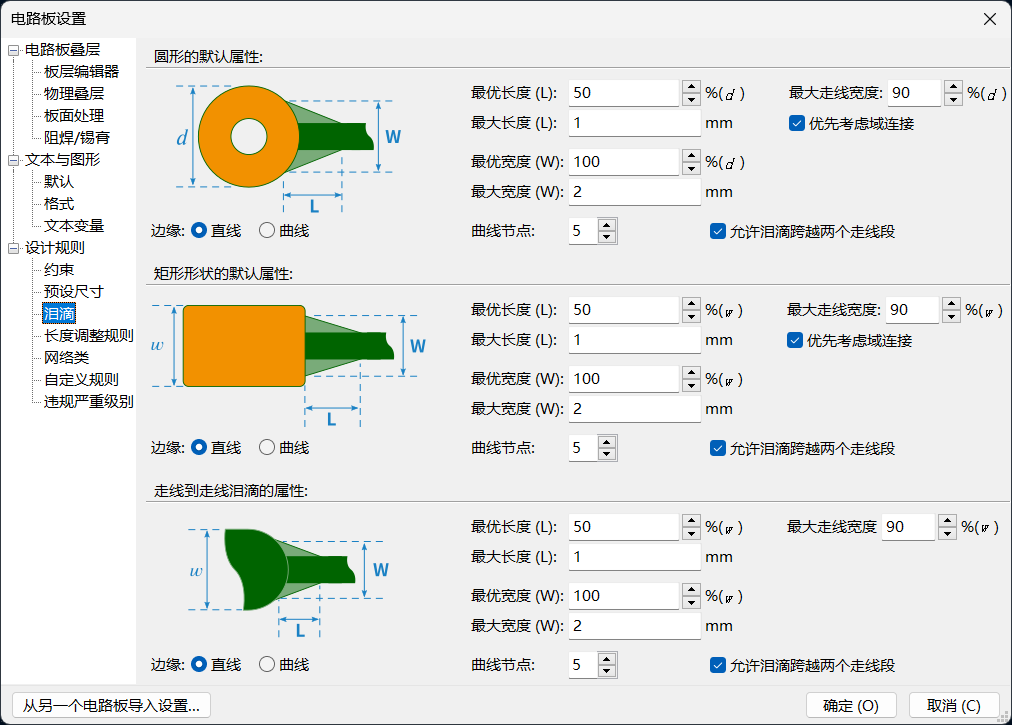

淚滴

可以在這里定義默認的淚滴形狀、規則等:

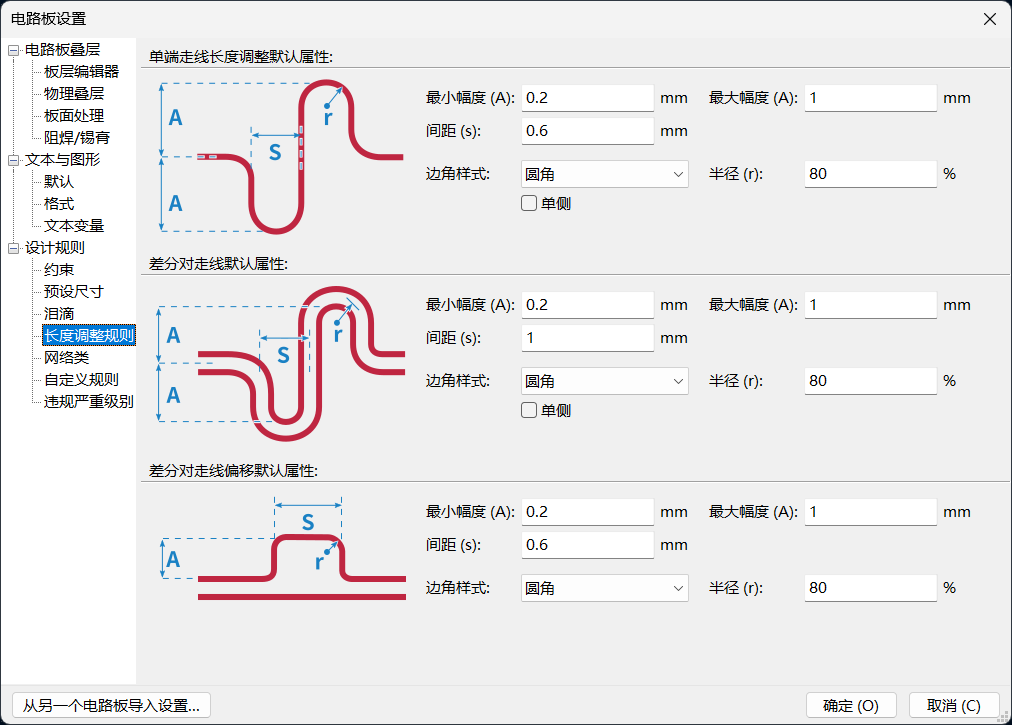

長度調整規則

在這里定義 length tuning 時默認的設置:

網絡類

在這里可以定義習慣使用的網絡類名稱及設計約束,這樣調用不用每次新建 PCB 時都重復定義:

關于如何定義網絡類可以參考:

KiCad 7中添加網絡類(一)

KiCad 7中添加網絡類(二)

怎么給差分信號定義網絡類?

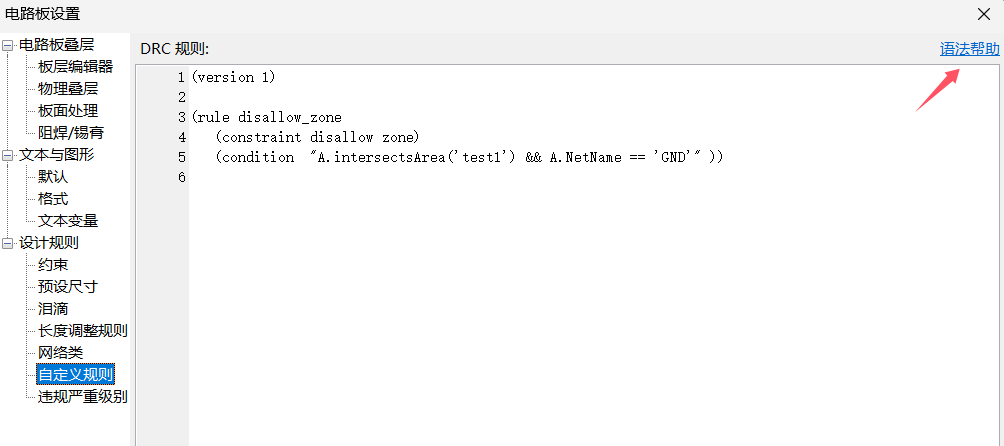

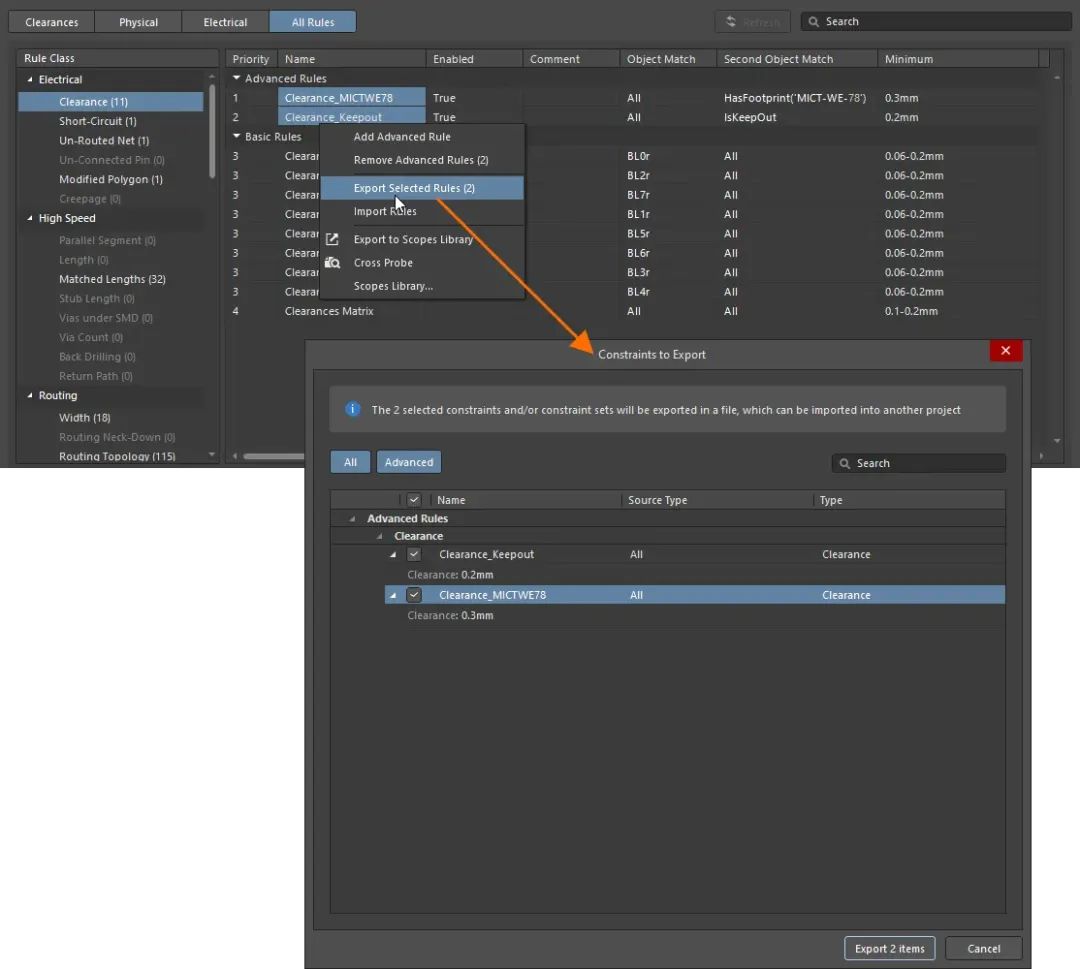

自定義規則

基本約束無法實現的規則可以在這里通過語法定義:

點擊右上方的“語法幫助”,可以查看自定義規則的語法及實例。

也可以參考以下文章學習自定義規則:KiCad 自定義規則語法與應用。

PCB 設置的保存與導出

在 KiCad 中要保存這些規則非常簡單粗暴,沒有特殊的導出按鍵。直接將 PCB 中的內容清空,將 PCB 保存即可。這些設置會保存在 PCB 文件中。

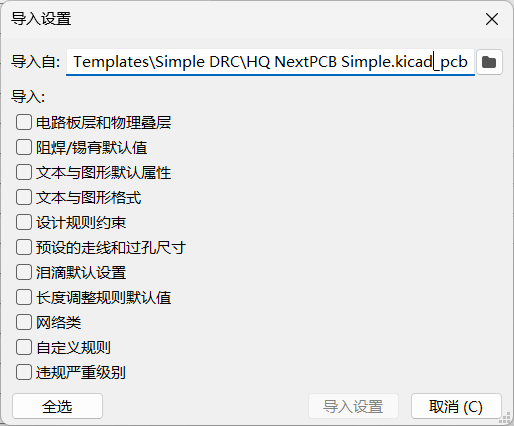

設計規則、層疊導入

也非常簡單粗暴,打開“電路板設置”,點擊下方的“從另一個電路板設置...”:  在“導入設置”中,選確定需要導入的模板 PCB,然后勾選需要導入的內容:

在“導入設置”中,選確定需要導入的模板 PCB,然后勾選需要導入的內容:

所有在電路板設置中的選項,都可以按照要求導入。

結束語

每位工程師都可以創建自己熟悉的層疊結構和設計規則,每次設計新的PCB時直接導入即可。 對于需要阻抗匹配的高速設計,可以結合板層結構和阻抗要求,計算出每個信號層相應網絡的線寬,并定義在網絡類中。這樣可以大大提高設計的統一性、準確性,減小出錯的概率,提高效率!

注意:如果想第一時間收到 KiCad 內容推送,請點擊下方的名片,按關注,再設為星標。

常用合集匯總:

和 Dr Peter 一起學 KiCad

KiCad 8 探秘合集

KiCad 使用經驗分享

KiCad 設計項目(Made with KiCad)

常見問題與解決方法

KiCad 開發筆記

插件應用

發布記錄

審核編輯 黃宇

-

pcb

+關注

關注

4404文章

23878瀏覽量

424270

發布評論請先 登錄

【「Altium Designer 25 電路設計精進實踐」閱讀體驗】+第六章節 PCB設計

PCB Gerber文件如何導出

KiCad 已支持導入 Altium 工程(Project)

如何優化層疊結構以提高PCB線路板整體性能簡述

Simcenter FLOEFD EDA Bridge模塊:使用導入的詳細PCB設計和IC熱特性來簡化熱分析

時源芯微 PCB 布線規則詳解

TSolidX應用:液晶掩膜結構GDSⅡ文件的生成和導出

高層數層疊結構PCB的布線策略

Allegro Skill封裝功能-導出device文件介紹與演示

PCB 設計規則、層疊結構的導入/導出

PCB 設計規則、層疊結構的導入/導出

評論