電子發燒友網報道(文/吳子鵬)當前,終端市場需求呈現多元化、智能化的發展趨勢,芯片制造則已經進入后摩爾定律時代,這就導致先進的工藝制程雖仍然是芯片性能提升的重要手段,但效果已經不如從前,先進封裝得到了業界的廣泛重視。

日前,由博聞創意會展主辦的第八屆中國系統級封裝大會SiP Conference China2024·蘇州站成功召開,大會演講主要圍繞 “AI/大算力應用”“存儲/高速互連應用”“新工藝及材料”三大主題。通過嘉賓的分享可以明顯感受到,在后摩爾定律時代,AI大算力應用對芯片發展有著積極的帶動作用,為了打造更強的高性能計算芯片,產業界從EDA、制造、封裝、存儲等多角度入手,全面推動集成芯片系統化發展。下面,我們來分享幾個來自SiP Conference China2024·蘇州站的解決方案,幫助大家捕捉技術發展的最前沿。

系統級創新打破“四力”挑戰

在大會致辭環節,中國半導體行業協會副秘書長兼封測分會秘書長徐冬梅表示,隨著信息技術的飛速發展,半導體行業迎來了前所未有的變革,特別是在后摩爾定律時代,異構集成和先進封裝技術已經成為行業發展的關鍵推動力。這些創新技術不僅能夠滿足高性能計算、人工智能(AI)、自動駕駛等新興領域對芯片性能的極致追求,更為整個芯片產業鏈帶來了更加廣闊的市場空間。

談到產業變革,芯和半導體副總裁倉巍談到了當前AI快速發展給半導體產業帶來的一些具體挑戰,主要是“四力”——算力、存力、運力和電力。可以簡單理解為,目前GPU等計算芯片的算力發展跟不上AI對于算力的需求,然而內存帶寬、I/O傳輸能力、總線傳輸能力也在限制算力的輸出。此外,高性能計算芯片和大規模數據中心/智算中心消耗了巨量的電能,對電力系統提出了非常高的要求。

對于倉巍談到的“四力”,產業界定然很有感觸,因為它們經常被稱為“四道墻”。為了突破這“四道墻”的限制,產業界進行了非常多的創新,比較典型的創新成果是英偉達公司Blackwell GB200 GPU,擁有2080億個晶體管,可提供高達20petaflops的FP4算力。在實現上,GB200將兩個B200和一個Grace CPU進行配對,再通過NVLink連接在一起。和H100相比,GB200的性能是其7倍,訓練速度是其4倍,且能耗更低。

倉巍認為,英偉達Blackwell GB200 GPU代表著芯片公司向系統發展的大趨勢,也證明集成芯片系統級創新是引領半導體行業克服“四力”挑戰的主要途徑。為了實現集成芯片系統級創新,高頻高速互聯技術、Chiplet異構集成以及配套EDA工具和先進封裝技術將成為后續芯片行業發展的主要技術趨勢。芯和半導體在此過程中,能夠提供端到端的多物理場仿真EDA,賦能AI硬件系統設計。

先進封裝的技術探索

根據市場調研機構TrendForce的預測數據,預計2025年英偉達Blackwell GB200 GPU的出貨量將超過100萬顆,占英偉達高端GPU芯片業務的四成。Blackwell GB200 GPU的成功也表明,基于臺積電CoWoS-S、CoWoS-L或CoWoS-R等先進封裝技術構建系統級封裝(SiP),是提升高性能計算芯片性能的有效途徑。

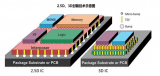

臺積電CoWoS-S、CoWoS-L和CoWoS-R代表著三種不同的技術類型,分別是硅中介層(Silicon Interposer)、重新布線層中介層(RDL Interposer)和結合局部硅互連和RDL中介層(Local Silicon Interconnect and RDL Interposer)。其中,硅中介層優勢在于其精密的制造工藝和優越的電性能,但價格昂貴;重新布線層中介層主要用于降低成本和適應不同類型的器件連接需求;結合局部硅互連和RDL中介層則是利用上述兩者的優點以實現更高效的封裝和連接。

翊杰科技股份有限公司執行長兼總經理蘇進成指出,自CoWoS問世以來,通過在緊湊的平面并排集成多個芯片,與傳統的多芯片模塊(MCM)相比提供了更高的集成度,為了能夠排列更多的芯片、容納更多的晶體管從而提高系統性能,中介層面積需要不斷擴大。通過掩模光刻拼接技術,臺積電CoWoS-S目前將硅中介層面積擴展到相當于三個完整掩模尺寸,最多能夠實現3個SOC/芯片和8個HBM共封。

蘇進成認為,在打造高性能AI計算芯片方面,HBM的重要性也是不容忽視的,是突破“存儲墻”的有效手段。HBM為High Bandwidth Memory的縮寫,即高帶寬內存,可提供高速、高帶寬的內存訪問。同時,HBM采用微凸塊和TSV技術,存儲和算力芯片信號傳輸路徑短,單引腳I/O速率較低,使HBM具備更好的內存能效特性。

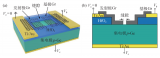

當然,通過先進封裝實現SiP封裝,技術路線并不局限于臺積電的CoWoS,比如臺積電關注的FOPLP(扇出型面板級封裝)技術未來潛力也非常大。FOPLP與扇出型晶圓級封裝(FOWLP)不同之處在于,FOPLP用較大的面板代替了晶圓,使用的材料、設備以及產品的線寬線距等存在差別。一般而言,FOPLP在同一工藝流程中能夠生產出更多的單個封裝體,在同樣面積的基板上能擺放更多的芯片,因而FOPLP具有更好的材料利用率和更低成本。

目前,FOPLP主要用于I/O密度低和粗線寬/線距的低端或中端應用,FOWLP主要用于 I/O密度高和細線寬/線距的高端應用。不過,奕成科技 VP & CTO方立志認為,現在做中低端的FOPLP就是一片紅海,做高端的FOPLP則擁有巨大的市場空間,是打造AI計算方案的可選路徑之一。尤其是在臺積電入局之后,高端FOPLP大有可為。

當然,方立志強調,FOPLP在高端應用中和FOWLP競爭的重點在于,工藝技術能力要和FOWLP相同,這樣才有競爭力。

不過,目前發展高端FOPLP還有非常多的挑戰,包括芯片位移、翹曲、細線路和細間距等。在翹曲方面,由于大型面板的熱膨脹系數(CTE)差異顯著,翹曲問題會導致工藝良率下降,高端AI方案的器件都非常貴,良率低是客戶無法接受的。

對于未來發展,方立志認為,板級封裝比晶圓級封裝更有前景,呼吁更多的業者參與其中。根據奕成科技官網新聞,2023年12月,奕成科技高端板級系統級封裝項目順利實現首款產品量產交付,進入產能爬坡的關鍵階段。

結語

不難看出,面對終端領域的高性能、多元化、智能化的需求,系統級創新已經成為關鍵手段,當前晶圓級封裝由于在高端市場的技術領先優勢,牢牢把控著市場,英偉達Blackwell GB200 GPU的成功也說明了這一點。不過,通過怎樣的先進封裝技術實現SiP封裝,技術路線并不是固定的,FOPLP后續的潛力是巨大的。當然要想打造更好的系統,EDA工具、存儲、高帶寬技術和材料技術也要跟上,SiP Conference China2024·蘇州站也有非常多的嘉賓談到了這些方面的創新。

-

摩爾定律

+關注

關注

4文章

640瀏覽量

81118

發布評論請先 登錄

AI時代算力瓶頸如何破?先進封裝成半導體行業競爭新高地

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+工藝創新將繼續維持著摩爾神話

當摩爾定律 “踩剎車” ,三星 、AP、普迪飛共話半導體制造新變革新機遇

Chiplet與3D封裝技術:后摩爾時代的芯片革命與屹立芯創的良率保障

晶心科技:摩爾定律放緩,RISC-V在高性能計算的重要性突顯

跨越摩爾定律,新思科技掩膜方案憑何改寫3nm以下芯片游戲規則

電力電子中的“摩爾定律”(1)

后摩爾定律時代,提升集成芯片系統化能力的有效途徑有哪些?

后摩爾定律時代,提升集成芯片系統化能力的有效途徑有哪些?

評論