在半導體產(chǎn)業(yè)鏈中,芯片封測作為連接設計與制造的橋梁,扮演著至關重要的角色。它不僅關乎芯片的最終性能表現(xiàn),還直接影響到產(chǎn)品的市場競爭力和成本效益。隨著科技的飛速發(fā)展,芯片封測技術也在不斷創(chuàng)新與進步,以滿足日益增長的智能化、小型化需求。本文將深入探討芯片封測的核心量產(chǎn)工藝,從原材料準備、晶圓切割、封裝成型到最終測試,全面解析這一復雜而精細的過程。

一、引言

芯片封測,即芯片封裝與測試,是將制造完成的晶圓切割成單個芯片,并通過封裝技術將芯片與外部電路連接,同時提供保護和支持的過程。封裝不僅保護了脆弱的芯片不受外界環(huán)境的影響,還通過引腳、焊球等方式實現(xiàn)了芯片與外部電路的電氣連接。測試則是驗證封裝后的芯片是否滿足設計規(guī)格和性能要求,確保產(chǎn)品質(zhì)量的重要環(huán)節(jié)。

二、原材料準備

1.晶圓來源與制造

芯片的原材料主要是高純度硅(Si),其來源于沙子經(jīng)過多步提純和加工制成的單晶硅棒。單晶硅棒經(jīng)過切割、研磨、拋光等工藝,形成表面平滑、厚度均勻的圓片狀晶圓(Wafer)。晶圓是芯片制造的基礎,其上集成了數(shù)以億計的晶體管和其他電子元件。

2.光刻膠與掩膜板

在芯片制造過程中,光刻膠和掩膜板是不可或缺的關鍵材料。光刻膠是一種對光敏感的有機聚合物,通過曝光和顯影過程,可以在晶圓表面形成精細的電路圖案。掩膜板則是一種具有預定電路圖案的透明基板,用于在光刻過程中將圖案轉(zhuǎn)移到光刻膠上。

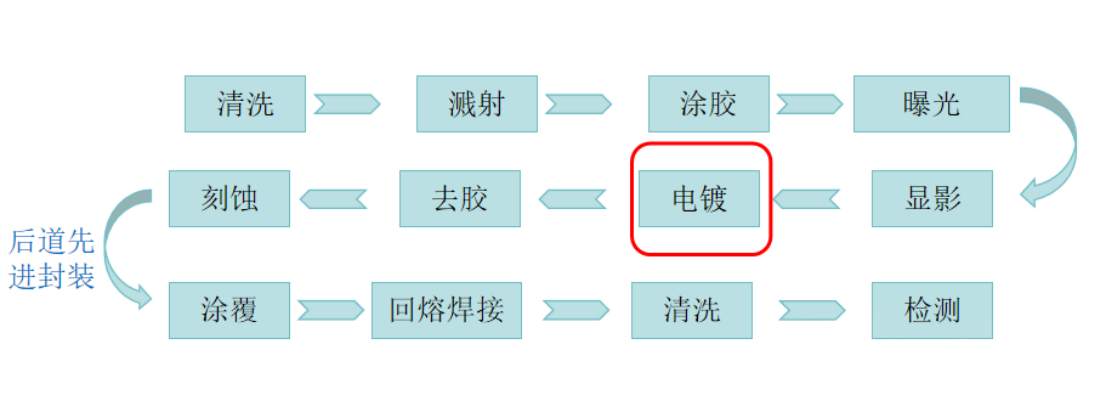

三、晶圓切割

晶圓切割是芯片封測的第一步,也是將晶圓上的芯片分離成獨立個體的關鍵環(huán)節(jié)。在切割之前,通常需要對晶圓背面進行減薄處理,以滿足封裝厚度的要求。減薄過程中,會在晶圓正面粘貼保護膜,以防止電路區(qū)域受損。

晶圓切割主要采用金剛石刀片或激光切割技術。金剛石刀片切割速度快、精度高,適用于大規(guī)模生產(chǎn)。激光切割則具有非接觸、熱影響小等優(yōu)點,特別適用于切割薄晶圓或特殊材料晶圓。切割完成后,晶圓被分割成眾多細小的芯片(Die),這些芯片隨后將進入封裝流程。

四、封裝成型

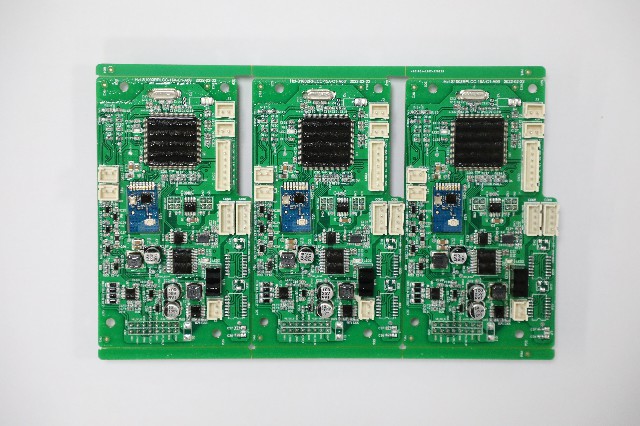

封裝是芯片封測的核心環(huán)節(jié)之一,其目的是保護芯片免受外界環(huán)境的影響,并提供與外部電路的連接接口。封裝技術種類繁多,包括引線框架封裝(如QFP、SOP)、球柵陣列封裝(BGA)、芯片尺寸封裝(CSP)、倒裝芯片封裝(Flip-Chip)等。以下以幾種常見的封裝技術為例進行介紹。

1.引線框架封裝

引線框架封裝是最傳統(tǒng)的封裝形式之一,廣泛應用于各種集成電路芯片。該封裝技術將芯片放置在引線框架的凹槽內(nèi),通過金絲球焊或鋁絲壓焊將芯片上的焊盤與引線框架的引腳相連。隨后,用塑封料將芯片和引腳包裹起來,形成保護殼。引線框架封裝具有成本低、工藝成熟等優(yōu)點,但引腳數(shù)量有限,適用于引腳數(shù)較少的芯片。

2.球柵陣列封裝(BGA)

球柵陣列封裝是一種高性能、高密度的封裝形式,廣泛應用于處理器、存儲器等高端芯片。BGA封裝將芯片倒裝在基板上,通過焊球與基板上的焊盤相連。焊球通常采用錫鉛合金或無鉛合金制成,具有良好的導電性和可靠性。BGA封裝具有引腳數(shù)多、引腳間距小、電氣性能優(yōu)越等優(yōu)點,是現(xiàn)代電子產(chǎn)品中廣泛采用的封裝形式之一。

3.芯片尺寸封裝(CSP)

芯片尺寸封裝是一種盡可能減小封裝尺寸的封裝技術,其封裝體尺寸接近于芯片本身。CSP封裝通過去除傳統(tǒng)封裝中的引線框架和塑封料等部分,實現(xiàn)了封裝尺寸的極大縮小。CSP封裝具有體積小、重量輕、散熱性能好等優(yōu)點,特別適用于便攜式電子設備和空間受限的應用場景。

4.倒裝芯片封裝(Flip-Chip)

倒裝芯片封裝是一種直接將芯片背面朝向基板進行封裝的技術。在倒裝芯片封裝中,芯片上的焊盤通過凸點(Bump)與基板上的焊盤相連。凸點通常采用金、銅等金屬制成,具有良好的導電性和可靠性。倒裝芯片封裝具有短引線、低電感、高速度等優(yōu)點,特別適用于高頻、高速信號處理的應用場景。

五、封裝測試

封裝測試是芯片封測的最后一道工序,也是確保產(chǎn)品質(zhì)量的重要環(huán)節(jié)。封裝測試主要包括功能測試、性能測試和可靠性測試等方面。

1.功能測試

功能測試是驗證封裝后的芯片是否能夠?qū)崿F(xiàn)設計規(guī)格中的各項功能。測試過程中,通過向芯片輸入特定的測試向量(Test Pattern),觀察芯片的輸出響應是否符合預期。功能測試通常包括靜態(tài)測試和動態(tài)測試兩種形式,靜態(tài)測試主要驗證芯片在靜態(tài)狀態(tài)下的電氣特性;動態(tài)測試則模擬實際工作場景下的信號變化,驗證芯片的動態(tài)性能。

2.性能測試

性能測試是對芯片的各項性能指標進行測試和評估的過程。性能測試包括速度測試、功耗測試、噪聲測試等多個方面。速度測試主要驗證芯片的處理速度和響應時間;功耗測試則評估芯片在工作狀態(tài)下的能耗情況;噪聲測試則檢測芯片在工作過程中產(chǎn)生的電磁干擾等噪聲信號。

3.可靠性測試

可靠性測試是評估芯片在長期使用過程中的穩(wěn)定性和可靠性的過程。可靠性測試包括溫度循環(huán)測試、濕度測試、振動測試等多個方面。溫度循環(huán)測試模擬芯片在不同溫度環(huán)境下的工作情況;濕度測試則評估芯片在潮濕環(huán)境下的耐腐蝕性;振動測試則模擬芯片在運輸和使用過程中可能遇到的振動沖擊情況。通過可靠性測試,可以確保芯片在各種惡劣環(huán)境下都能保持穩(wěn)定的性能表現(xiàn)。

六、封裝技術發(fā)展趨勢

隨著半導體技術的不斷發(fā)展,封裝技術也在不斷創(chuàng)新與進步。未來封裝技術的發(fā)展趨勢主要包括以下幾個方面:

1.封裝尺寸持續(xù)縮小

隨著便攜式電子設備和可穿戴設備的普及,對芯片封裝尺寸的要求越來越高。未來封裝技術將繼續(xù)向小型化、微型化方向發(fā)展,以滿足市場需求。

2.高密度封裝技術

隨著芯片集成度的不斷提高,對封裝引腳數(shù)量的需求也在不斷增加。未來封裝技術將更加注重高密度、高引腳數(shù)的實現(xiàn)方式,以滿足高端芯片的應用需求。

3.三維封裝技術

三維封裝技術是一種將多個芯片垂直堆疊在一起的封裝形式。通過三維封裝技術,可以顯著提高芯片的集成度和性能表現(xiàn),同時降低封裝尺寸和成本。未來三維封裝技術將成為封裝領域的重要發(fā)展方向之一。

4.綠色封裝技術

隨著環(huán)保意識的不斷提高,綠色封裝技術將成為未來封裝領域的重要趨勢之一。綠色封裝技術注重減少封裝過程中的有害物質(zhì)排放和能源消耗,同時提高封裝產(chǎn)品的可回收性和再利用性。

七、結論

芯片封測作為半導體產(chǎn)業(yè)鏈中的重要環(huán)節(jié)之一,其技術水平和工藝質(zhì)量直接影響到芯片的最終性能表現(xiàn)和市場競爭力。本文深入探討了芯片封測的核心量產(chǎn)工藝從原材料準備、晶圓切割、封裝成型到最終測試的全過程,并分析了未來封裝技術的發(fā)展趨勢。隨著科技的不斷進步和市場需求的不斷變化,芯片封測技術將繼續(xù)創(chuàng)新與發(fā)展為半導體產(chǎn)業(yè)的繁榮貢獻力量。

-

芯片

+關注

關注

463文章

54007瀏覽量

465929 -

半導體

+關注

關注

339文章

30725瀏覽量

264036 -

封測

+關注

關注

4文章

381瀏覽量

36085

發(fā)布評論請先 登錄

長電科技車規(guī)級芯片封測工廠順利通線

PCB板ATE測試探針卡設計和生產(chǎn)的核心技術要求,你知道多少?

能源數(shù)字化轉(zhuǎn)型核心!一張圖揭秘綠電直連“五流合一”超級架構

功率芯片PCB內(nèi)埋式封裝:從概念到量產(chǎn)的全鏈路解析(中篇)

SMT打樣必看!5大核心質(zhì)控點,從材料到工藝全流程拆解

??PCBA拼板分板全流程解析:從設計到量產(chǎn),每一步都很關鍵!

功率芯片PCB內(nèi)埋式封裝:從概念到量產(chǎn)的全鏈路解析(下篇:封裝工藝制程全解析)

HX4057T替代方案全解析:如何根據(jù)需求選擇芯片

技術干貨 | 從偏移誤差到電源抑制比,DAC核心術語全解析

揭秘半導體電鍍工藝

芯知識|廣州唯創(chuàng)電子語音芯片開發(fā)全流程解析:從選型到量產(chǎn)的實踐指南

當我問DeepSeek國內(nèi)芯片封測有哪些值得關注的企業(yè),它這樣回我

從技術研發(fā)到市場拓展:萬年芯在封測領域的進階之路

芯片封測揭秘:核心量產(chǎn)工藝全解析

芯片封測揭秘:核心量產(chǎn)工藝全解析

評論