當(dāng)今處理器一共有三個最強(qiáng)大的架構(gòu),其中之一是以intel和AMD為代表的x86架構(gòu),另外一個是手機(jī),平板處理器所使用的ARM架構(gòu),最后一個便是我國龍芯處理器所選擇的MIPS架構(gòu)。這三大處理器架構(gòu)中,x86和ARM是商業(yè)化進(jìn)程最為優(yōu)秀的兩大架構(gòu)。也正是因?yàn)檫@兩大架構(gòu)的商業(yè)化進(jìn)程太為出色,所以我國的龍芯處理器才被很多人批判為最嚴(yán)重的選擇性失誤。

但是從處理器的設(shè)計(jì)和能耗比來說,如果要說最經(jīng)典的RISC處理器,那么非MIPS莫屬,就連它的競爭對手,也不得不承認(rèn)它的優(yōu)雅,它被作為處理器教科書的典范,很多其他的處理器,都能看到它的身影。

為什么史上最強(qiáng)IC公司Intel和最早的RISC公司收到ARM的步步蠶食?我們今天來了解一下,歡迎大家在“評論”發(fā)表自己觀點(diǎn)。

隨著ARM在智能手機(jī)市場獨(dú)占鰲頭,如同兩把尖刀刺入intel和MIPS的腹地。

眾所周知,基于MIPS的MCU的應(yīng)用廣泛多元,包括工業(yè)、辦公自動化、汽車、消費(fèi)電子系統(tǒng)和先進(jìn)技術(shù),如無線通信等。此外,我們看到目前可穿戴和超便攜市場的需求不斷增長,瞄準(zhǔn)這一領(lǐng)域的公司迫切希望硅IP供應(yīng)商如Imagination等提供高效的解決方案,以便可以輕易集成進(jìn)那些全功能產(chǎn)品中。

MIPS的前世今生

MIPS是世界上很流行的一種RISC處理器。MIPS的意思是“無內(nèi)部互鎖流水級的微處理

器”(Microprocessor without interlocked piped stages),其機(jī)制是盡量利用軟件辦法避免流水線中的數(shù)據(jù)相關(guān)問題。它最早是在80年代初期由斯坦福(Stanford)大學(xué)Hennessy教授領(lǐng) 導(dǎo)的研究小組研制出來的。MIPS公司的R系列就是在此基礎(chǔ)上開發(fā)的RISC工業(yè)產(chǎn)品的微處理器。這些系列產(chǎn)品為很多計(jì)算機(jī)公司采用構(gòu)成各種工作站和計(jì)算 機(jī)系統(tǒng)。

MIPS技術(shù)公司是美國著名的芯片設(shè)計(jì)公司,它采用精簡指令系統(tǒng)計(jì)算結(jié)構(gòu)(RISC)來設(shè)計(jì)芯片。和英特爾采用的復(fù)雜指令系統(tǒng)計(jì)算結(jié)構(gòu)(CISC)相比, RISC具有設(shè)計(jì)更簡單、設(shè)計(jì)周期更短等優(yōu)點(diǎn),并可以應(yīng)用更多先進(jìn)的技術(shù),開發(fā)更快的下一代處理器。MIPS是出現(xiàn)最早的商業(yè)RISC架構(gòu)芯片之一,新的 架構(gòu)集成了所有原來MIPS指令集,并增加了許多更強(qiáng)大的功能。

1986年推出R2000處理器,1988年推出R3000處理器,1991年推出第一款64位商用微處理器R4000。之后,又陸續(xù)推出R8000(于 1994年)、R10000(于1996年)和R12000(于1997年)等型號。1999年,MIPS公司發(fā)布MIPS 32和MIPS 64架構(gòu)標(biāo)準(zhǔn)。2000年,MIPS公司發(fā)布了針對MIPS 32 4Kc的新版本以及未來64位MIPS 64 20Kc處理器內(nèi)核。

在MIPS芯片的發(fā)展過程中,SGI公司在1992年收購了MIPS計(jì)算機(jī)公司,1998年,MIPS公司又脫離了SGI,成為MIPS技術(shù)公司; MIPS32 4KcTM 處理器是采用MIPS技術(shù)特定為片上系統(tǒng)(System-On-a-Chip)而設(shè)計(jì)的高性能、低電壓 32位MIPS RISC 內(nèi)核。采用MIPS32TM體系結(jié)構(gòu),并且具有R4000存儲器管理單元(MMU)以及擴(kuò)展的優(yōu)先級模式,使得這個處理器與目前嵌入式領(lǐng)域廣泛應(yīng)用的 R3000和R4000系列(32位)微處理器完全兼容.

新的 64 位 MIPS 處理器是RM9000x2,從“x2”這個標(biāo)記判斷,它包含了不是一個而是兩個均具有集成二級高速緩存的64位處理器。RM9000x2 主要針對網(wǎng)絡(luò)基礎(chǔ)設(shè)施市場,具有集成的 DDR 內(nèi)存控制器和超高速的 HyperTransport I/O 鏈接。處理器、內(nèi)存和 I/O均通過分組交叉連接起來的,可實(shí)現(xiàn)高性能、全面高速緩存的統(tǒng)一芯片系統(tǒng)。除通過并行處理提高系統(tǒng)性能外,RM9000x2 還通過將超標(biāo)量與超流水線技術(shù)相結(jié)合來提高單個處理器的性能。

64位處理器MIPS 64 20Kc的浮點(diǎn)能力強(qiáng),可以組成不同的系統(tǒng),從一個處理器的Octane工作站到64個處理器的Origin 2000服務(wù)器;這種CPU更適合圖形工作站使用。MIPS最新的R12000芯片已經(jīng)在SGI的服務(wù)器中得到應(yīng)用,目前其主頻最大可達(dá)400MHz。

MIPS處理器是八十年代中期RISC CPU設(shè)計(jì)的一大熱點(diǎn)。MIPS是賣的最好的RISC CPU,可以從任何地方,如Sony, Nintendo的游戲機(jī),Cisco的路由器和SGI超級計(jì)算機(jī),看見MIPS產(chǎn)品在銷售。目前隨著RISC體系結(jié)構(gòu)遭到x86芯片的競爭,MIPS有 可能是起初RISC CPU設(shè)計(jì)中唯一的一個在本世紀(jì)盈利的。和英特爾相比,MIPS的授權(quán)費(fèi)用比較低,也就為除英特爾外的大多數(shù)芯片廠商所采用。

MIPS的系統(tǒng)結(jié)構(gòu)及設(shè)計(jì)理念比較先進(jìn),其指令系統(tǒng)經(jīng)過通用處理器指令體系MIPS I、MIPS II、MIPS III、MIPS IV到MIPS V,嵌入式指令體系MIPS16、MIPS32到MIPS64的發(fā)展已經(jīng)十分成熟。在設(shè)計(jì)理念上MIPS強(qiáng)調(diào)軟硬件協(xié)同提高性能,同時簡化硬件設(shè)計(jì)。

中國龍芯2和前代產(chǎn)品采用的都是64位MIPS指令架構(gòu),它與大家平常所知道的X86指令架構(gòu)互不兼容,MIPS指令架構(gòu)由MIPS公司所創(chuàng),屬于 RISC體系。過去,MIPS架構(gòu)的產(chǎn)品多見于工作站領(lǐng)域,索尼PS2游戲機(jī)所用的“Emotion Engine”也采用MIPS指令,這些MIPS處理器的性能都非常強(qiáng)勁,而龍芯2也屬于這個陣營,在軟件方面與上述產(chǎn)品完全兼容。

MIPS 技術(shù)公司則是一家設(shè)計(jì)制造高性能、高檔次及嵌入式32位和64位處理器的廠商。在通用方面,MIPS R系列微處理器用于構(gòu)建SGI的高性能工作站、服務(wù)器和超級計(jì)算機(jī)系統(tǒng)。在嵌入式方面,MIPS K系列微處理器是目前僅次于ARM的用得最多的處理器之一(1999年以前MIPS是世界上用得最多的處理器),其應(yīng)用領(lǐng)域覆蓋游戲機(jī)、路由器、激光打印 機(jī)、掌上電腦等各個方面。

由于服務(wù)器RISC處理器市場的激烈競爭結(jié)果導(dǎo)致HP 公司放棄它的PA-RISC和“私生子”Alpha 兩種類型服務(wù)器處理器,而“Alpha技術(shù)”則被Intel和AMD吸收應(yīng)用到他們自身的處理器中; MIPS處理器應(yīng)用范圍則較廣,對于作為服務(wù)器RISC處理器來說,主要是應(yīng)用于專門的圖形工作站/服務(wù)器上;相對來說,應(yīng)用面較專業(yè),因而競爭較少。就 目前的服務(wù)器RISC處理器來說,主要是IBM 的POWER和SUN 的UltraSPARC 兩大處理器之間的競爭;相對而言,IBM在這場RISC處理器競爭中是個大贏家。

MIPS VS ARM

以RISC技術(shù)為基礎(chǔ),再加上MIPS架構(gòu)中的可擴(kuò)展硬軟件設(shè)計(jì),使得MIPS的解決方案比ARM的同類解決方案性能更高、功耗更低且面積更小。MIPS科技原來主要瞄準(zhǔn)高性能工作站與服務(wù)器,而ARM最初針對低端移動系統(tǒng)開發(fā)基本內(nèi)核。MIPS充分利用它在高性能設(shè)計(jì)方面的經(jīng)驗(yàn),向主流嵌入式系統(tǒng)市場轉(zhuǎn)型。ARM則繼續(xù)沿用其原有性能有限的架構(gòu),相比MIPS,它處于不利地位。

MIPS32 4K?處理器內(nèi)核系列包括MIPS32 M4K?內(nèi)核,其應(yīng)用程序執(zhí)行速度超過同類ARM Cortex?-M系列內(nèi)核。這一優(yōu)勢部分可歸功于更高效的MIPS指令集架構(gòu)和優(yōu)化軟件工具,但主要原因還是在于MIPS架構(gòu)具有眾多專為更高的性能級和應(yīng)用效率而設(shè)計(jì)的出色特性,其中包括一般是在微控制器設(shè)計(jì)中實(shí)現(xiàn)的加速功能。例如:

? MIPS 內(nèi)核包含32個GPR(通用寄存器),而ARM內(nèi)核只有16個GPR。這意味著寄存器溢出更少,從而性能更高。

? MIPS內(nèi)核包含有影子寄存器組,而ARM內(nèi)核沒有。使用映像寄存器可加速中斷處理保存/恢復(fù)功能,減少上下文切換(context switching)和中斷延遲中所需要的周期。

? MIPS架構(gòu)主要執(zhí)行單一操作指令,而ARM指令在寫入GPR之前執(zhí)行多個操作(如移位操作、算術(shù)操作、條件校驗(yàn)位等等),故MIPS更容易達(dá)到更高的時鐘頻率。

? MIPS架構(gòu)采用比ARM更簡單的存儲器尋址模式工作,故更容易達(dá)到更高的時鐘工作頻率。

? MIPS架構(gòu)的預(yù)測執(zhí)行較少,這大大降低了其邏輯復(fù)雜性,并使MIPS內(nèi)核能夠達(dá)到更高的頻率。

? M4K與M14K具有5級流水線結(jié)構(gòu),故無需預(yù)測分支方向。而ARM內(nèi)核采用了復(fù)雜的分支預(yù)測和分支推測邏輯。

? MIPS架構(gòu)實(shí)現(xiàn)了帶延遲的分支,而ARM結(jié)構(gòu)不這樣;這意味著,利用MIPS,在短流水設(shè)計(jì)時可獲得更高效率。

? MIPS同時提供32位和64位架構(gòu),MIPS64架構(gòu)具有后向兼容性和更高的性能。ARM只有32位架構(gòu),而且并非所有版本都后向兼容。

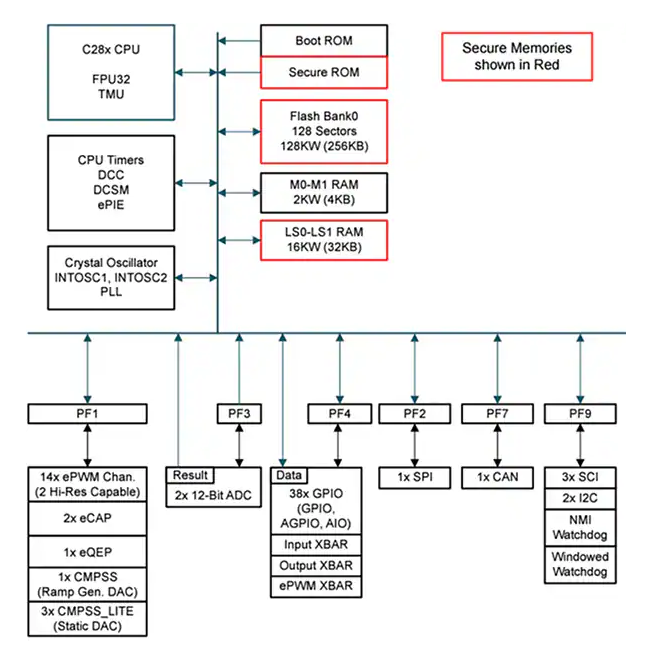

M4K 執(zhí)行流水線

M4K內(nèi)核的性能可達(dá)1.5 DMIPS/MHz,而根據(jù)ARM網(wǎng)站公布的數(shù)據(jù),Cortex-M3的性能只有1.25 DMIPS/MHz,比前者低約20% (ARM Cortex-M0的性能甚至更低,僅0.9 DMIPS/MHz,比MIPS32 M4K內(nèi)核低40%;Cortex-M0 還存在眾多其它局限性,我們接下來會討論到)。換言之,Cortex-M3 需要使用高20%的時鐘頻率才能達(dá)到M4K內(nèi)核的性能,但隨之產(chǎn)生更多的功耗。

類似的,如第4節(jié)的“性能基準(zhǔn)”所述,在采用CoreMark 基準(zhǔn)時,M4K內(nèi)核可達(dá)到2.297 CM/MHz的性能,比同類的基于Cortex-M3的解決方案高20-30%。MIPS已把業(yè)內(nèi)越來越獲認(rèn)可的CoreMark基準(zhǔn)視為比Dhrystone MIPS更精確的CPU性能測量標(biāo)準(zhǔn)。

M4K執(zhí)行單元采用5級流水線微架構(gòu),如圖2所示,而Cortex-M3內(nèi)核的執(zhí)行則基于3級流水線架構(gòu)。因此M4K內(nèi)核能夠采用更高的最大時鐘頻率,每秒鐘處理更多的指令,從而獲得比Cortex-M3更高的性能和執(zhí)行效率。

在M4K內(nèi)核中,所有ALU和移位操作都在單周期內(nèi)完成。旁路邏輯(Bypass logic)包含在流水線中,在所有流水線級完成之前提供快速數(shù)據(jù)存取以供下一條指令所用。由于執(zhí)行特定任務(wù)的周期縮短,性能得以提高。

MIPS架構(gòu)是龍芯發(fā)展的唯一選擇

在自MIPS中國看來,龍芯處理器的架構(gòu)選擇并沒有錯誤,相反的如果龍芯要想得到更好的發(fā)展,選擇MIPS才是最為正確的道路。這又是為何呢?這還要從這三大架構(gòu)的擁有者談起。

x86架構(gòu)的擁有者intel可以算作是技術(shù)合作上最摳門兒的一位,在推出x86架構(gòu)之后,intel就只將這一架構(gòu)授權(quán)給過AMD和VIA等幾個芯片公司。而在VIA退出x86架構(gòu)處理器競爭之后,intel便不再給任何公司x86架構(gòu)授權(quán)。所以從x86架構(gòu)上入手,龍芯處理器顯然是行不通的。intel的x86架構(gòu)行不通,那么ARM架構(gòu)是否就能行得通呢?答案當(dāng)然也是否定的。

x86被intel獨(dú)占幾十年,奉行的是肥水不流外人田的政策

ARM公司是一家非常優(yōu)秀的芯片設(shè)計(jì)公司,但自身并不生產(chǎn)處理器,而是將自身的設(shè)計(jì)licensing賣給需要處理器的公司,而后交給他們生產(chǎn)或者是找人代工。也許有人要問了,既然ARM向外賣出架構(gòu)設(shè)計(jì),那么為何龍芯不去選擇ARM架構(gòu)呢?其實(shí)不然,ARM之所以能夠發(fā)展成為一家非常成功的商業(yè)性公司,靠的就是芯片的架構(gòu)設(shè)計(jì),倘若架構(gòu)設(shè)計(jì)被別人奪走了,那么自己就丟掉了賴以生存的飯碗。所以ARM雖然對外進(jìn)行l(wèi)icensing授權(quán),卻不允許購買者進(jìn)行任何對ARM架構(gòu)有更改的設(shè)計(jì)。倘若個更改了設(shè)計(jì),那么這便違反了合作協(xié)定。ARM便有權(quán)撤回licensing授權(quán)。我國的龍芯要是選擇了ARM架構(gòu)的話,那么基本上也就被捆住了腳步,無法發(fā)展出屬于自己的高性能處理器了。

自身雖然強(qiáng)大,但因考慮到市場發(fā)展的問題ARM也對外妥協(xié)過。目前高通,蘋果和NVIDIA這三家公司便是ARM體系中較為特殊的幾個。因?yàn)檫@三家公司在芯片設(shè)計(jì)領(lǐng)域的特殊地位,ARM為了能夠拉攏他們站立在自己的陣營中,對這三家公司開出了特別通行證。在其他芯片公司只能使用licensing去生產(chǎn)芯片的時候,高通,蘋果和NVIDIA卻能夠自行設(shè)計(jì)基于ARM架構(gòu)的處理器。也正是拉攏到了高通,蘋果和NVIDIA,才使得ARM擁有了更多的支持者。但即便這樣,我們也不得不佩服ARM的老狐貍作風(fēng),在給出架構(gòu)授權(quán)后,ARM依然會通過升級下一代架構(gòu)為由讓高通,蘋果和NVIDIA再掏一回錢購買架構(gòu)授權(quán)。這樣ARM就可以再賺一把。相信看到這里您應(yīng)該了解到龍芯不選擇ARM的原因了。

那么是什么本領(lǐng)讓MIPS最終成為了我國龍芯處理器的設(shè)計(jì)架構(gòu)呢?答案非常簡單,那就是架構(gòu)授權(quán)。也許有人又問了,ARM不也是給授權(quán)嗎?那為什么還選MIPS呢?面對這樣的問題,MIPS和ARM雖然都是對外進(jìn)行架構(gòu)授權(quán)的公司,但意義完全不同。ARM對外出售的是設(shè)計(jì)方案授權(quán)(licensing),與ARM的商業(yè)化相比,MIPS倒像是學(xué)院派的公司。MIPS的架構(gòu)授權(quán),并不限制任何對MIPS架構(gòu)的更改。換句話說,就是MIPS公司給授權(quán)者一張白紙,而白紙上僅僅寫著一行字,MIPS公司同意你設(shè)計(jì)生產(chǎn)MIPS架構(gòu)處理器,至于你設(shè)計(jì)成什么樣,性能有多高,經(jīng)過多少代更改,MIPS一概不管,只要你不把架構(gòu)徹底改變就行了。與ARM相比,MIPS是一個完全開放的架構(gòu),對龍芯未來的發(fā)展沒有任何的限制,這與intel給AMD x86架構(gòu)授權(quán),而不是給設(shè)計(jì)圖紙的道理是完全一樣的。在加上MIPS本身經(jīng)過幾十年的發(fā)展,已經(jīng)擁有了眾多的應(yīng)用軟件,綜合考慮來看,MIPS是最為適合龍芯處理器發(fā)展的架構(gòu)選擇。

MIPS的意思是“無內(nèi)部互鎖流水級的微處理器”(Microprocessor without interlocked piped stages),其機(jī)制是盡量利用軟件辦法避免流水線中的數(shù)據(jù)相關(guān)問題。

互鎖的發(fā)生主要有以下幾種情況,

一是由于流水線中的2個處理模塊同時使用同一資源產(chǎn)生冒險(xiǎn),此時等待資源的流水級以及前面的流水級都要等待;

二是由于在某一流水級的操作需要多個時鐘周期,整個流水線上的各個流水級等待多周期操作的完成。當(dāng)互鎖發(fā)生后,互鎖處理模塊暫停流水線直到互鎖解決。

如果從不同流水級同時發(fā)出暫停流水線的請求,也要判斷暫停流水線請求的優(yōu)先級。

MIPS的流水線的特點(diǎn):

一條經(jīng)典的5段流水線

每一個周期作為一個流水段;

在各段之間加上鎖存器(流水寄存器)。

MIPS的意思是“無內(nèi)部互鎖流水級的微處理器”(Microprocessor without interlocked piped stages),其機(jī)制是盡量利用軟件辦法避免流水線中的數(shù)據(jù)相關(guān)問題。

1、流水寄存器保證了流水線中不同段的指令不會相互影響。每個時鐘周期結(jié)束之后,該段的所有執(zhí)行結(jié)果都保存在流水段寄存器中,在下一個時鐘周期開始作為下一個段的輸入。

需要確定處理器在每一個時鐘周期都進(jìn)行什么樣的動作。

要保證在同一個周期沒有兩條指令使用相同的數(shù)據(jù)通路資源。

可以采用流水線方式下簡化的RISC數(shù)據(jù)通路圖來表示。

上圖藍(lán)色小方框表示寄存器。

MIPS流水線方式實(shí)現(xiàn)時,應(yīng)解決好以下幾個問題:

1、要保證不會在同一時鐘周期要求同一個功能段做兩件不同的工作。

例如:不能要求ALU同時做有效地址計(jì)算和算術(shù)運(yùn)算。

2、避免IF段的訪存(取指令)與MEM段的訪存(讀/寫數(shù)據(jù))發(fā)生沖突。

可以采用分離的指令存儲器和數(shù)據(jù)存儲器;

一般采用分離的指令Cache和數(shù)據(jù)Cache。

ID段和WB段都要訪問同一寄存器文件.

如何解決對同一寄存器的訪問沖突?

把寫操作安排在時鐘周期的前半拍完成,把讀操作安排在后半拍完成。

上圖中,邊框畫實(shí)線表示操作,畫虛線表示不做任何操作。

流水寄存器的作用

將各段的工作隔開,使得它們不會互相干擾。

保存相應(yīng)段的處理結(jié)果。

流水線寄存器在兩個相鄰的流水段之間既傳遞數(shù)據(jù)也傳遞控制信息。后面流水段需要的數(shù)據(jù),必須能從一個流水寄存器復(fù)制到下一個流水寄存器,直到不再需要為止。

所以流水寄存器與非流水通路中使用的臨時寄存器不一樣。

解決數(shù)據(jù)沖突的問題

讓一條指令從ID段到EX段的操作稱為發(fā)射指令。

對于MIPS定點(diǎn)流水線,所有的數(shù)據(jù)沖突均可以在ID段檢測到。

如果存在數(shù)據(jù)沖突,就在相應(yīng)的指令流出ID段之前(也就是發(fā)射前)將之暫停。完成該工作的硬件稱為流水線的互鎖機(jī)制。

采用數(shù)據(jù)定向的思想避免數(shù)據(jù)相關(guān)

兩種動態(tài)調(diào)度算法

記分牌算法和Tomasulo算法是兩種比較典型的動態(tài)調(diào)度算法。

盡量減少數(shù)據(jù)沖突造成的流水線性能影響。

-

intel

+關(guān)注

關(guān)注

19文章

3508瀏覽量

191265 -

mips

+關(guān)注

關(guān)注

1文章

242瀏覽量

49432 -

龍芯處理器

+關(guān)注

關(guān)注

1文章

25瀏覽量

11478

發(fā)布評論請先 登錄

TAS3103A數(shù)字音頻處理器:特性、架構(gòu)與應(yīng)用詳解

Cortex-M0 處理器介紹

關(guān)于協(xié)處理器自定義指令的實(shí)現(xiàn)

基于E203 NICE協(xié)處理器擴(kuò)展指令

基于E203 NICE協(xié)處理器擴(kuò)展指令2.0

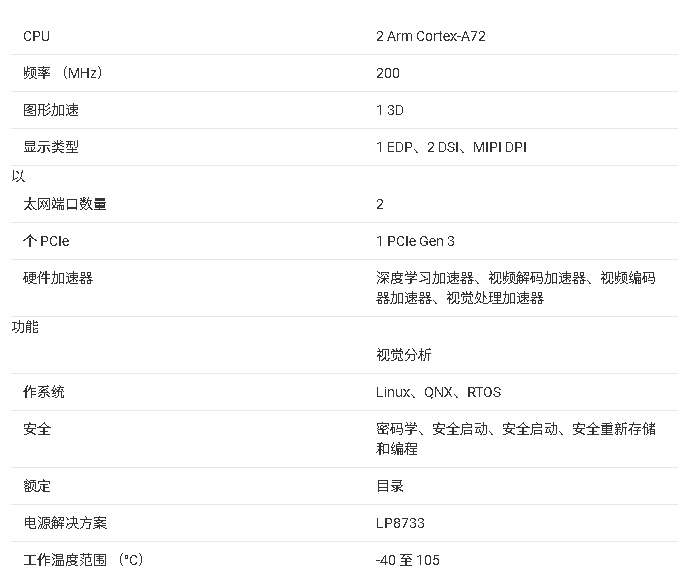

?AM68A/AM68處理器技術(shù)文檔摘要

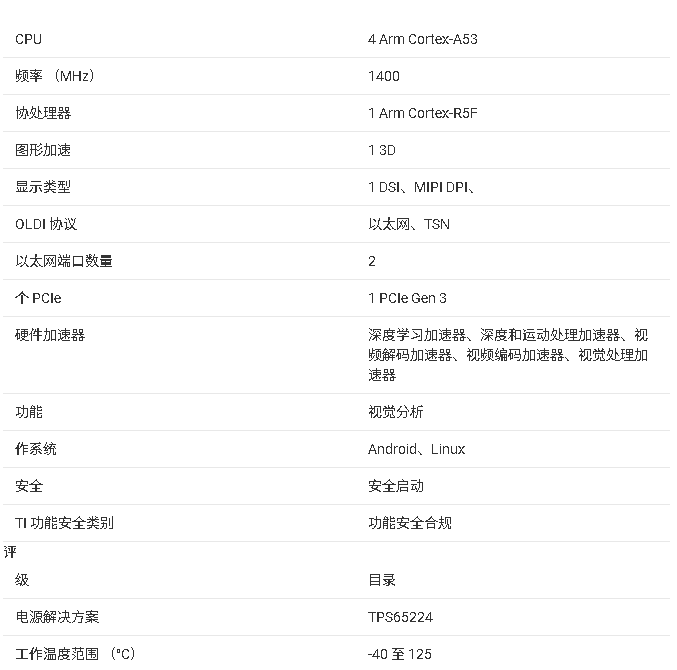

AM67x處理器技術(shù)文檔總結(jié)

什么是ARM架構(gòu)?你需要知道的一切

德州儀器AM68x Jacinto 8處理器技術(shù)解析

明晚開播 |開源芯片系列講座第28期:高性能RISC-V微處理器芯片

直播預(yù)約 |開源芯片系列講座第28期:高性能RISC-V微處理器芯片

格羅方德擬收購人工智能和處理器IP供應(yīng)商MIPS

AMD嵌入式處理器為您的應(yīng)用添能助力

龍芯處理器支持WINDOWS嗎?

技術(shù)分享 | 如何在2k0300(LoongArch架構(gòu))處理器上跑通qt開發(fā)流程

處理器MIPS架構(gòu)的知識您都知道么?沒關(guān)系這篇文章告訴你

處理器MIPS架構(gòu)的知識您都知道么?沒關(guān)系這篇文章告訴你

評論