一、Efinity工程

io_memoryClk是與存儲器接口共用的時鐘,需要連接正確。

由于鈦金系列是有片上晶振的,所以有些客戶可能會選擇片上晶振作為SOC的系統時鐘或者選擇片上晶振作為PLL的參考時鐘,再由該PLL的輸出時鐘作為SOC的系統時鐘,但是由于片上晶振頻率偏差比較大,所以UART的波特率是不準確的,這也是為什么UART出問題的原因。

FLASH

flash管腳interface設置。

flash出問題也是一個很常見的問題,

之前遇到有客戶反饋riscv 燒寫到flash啟動不了,原因是riscv必須要控制flash,因為bootloader會讀取flash中的數據用于加載APP;

(2)flash的IO輸入輸出都要添加IO寄存器,之前遇到有客戶不能讀寫flash的情況。

Ext_flash_clk | Ext_flash_cs | |

Mode | output | output |

I/O Standard | 1.8V LVCMOS | 1.8V LVCMOS |

Connection Type | -- | -- |

Register Option | register | register |

Double Data I/O Option | none | none |

Enable Serialization | No | No |

Clock Pin Name | soc_clk | soc_clk |

Pull Option | - | - |

Drive Strenght | 4 | 4 |

Instance Name | Ext_falsh_dx | ||

Base | Output | ||

Mode | inout | Constant Output | none |

I/O Standard | 1.8V lvcmos | Register Option | register |

Input | Double Dat | none | |

Connection Type | normal | Enable Serialization | No |

Register Option | register | Drive Strength | 4 |

Clock | Clk | Enable Slew Rate | No |

Double data | None | Static Delay Setting | 0 |

Pull Option | None | Output Enable | |

Enable Schmitt | No | Register Option | Register |

Enable bus hold | No | Oputput Clock | |

Static Delay setting | 0 | Pin Name | Clk |

Inverted | No | ||

二、RISCV 工程

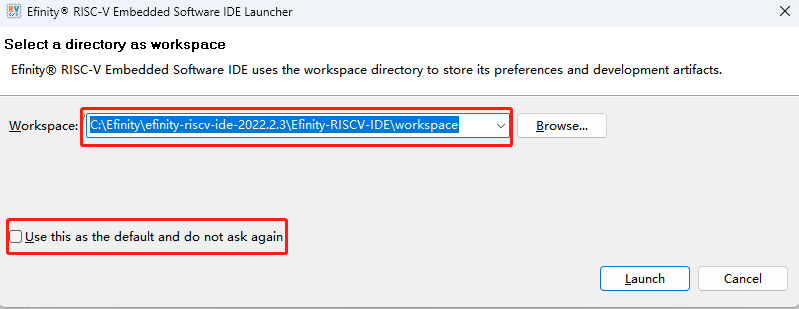

自從新版本的Efinity RISC-V IDE發布之后,這直沒有時間操作一下,它為RISC-V ' C '和' c++ '軟件開發提供了一個完整、無縫的環境;今天終于安裝了,但安裝自不必多說,一路點擊下去就可以了。來體驗一把。

2.1 打開IDE自帶工程。

(1)首先打開軟件。

step1:選擇工程的工作空間。如果工作空間長時間不變可以勾選Use this as the default and do not ask agin。

與老版本的區別是,新版本可以將該選擇到任何地方。

step2:生成sapphire的example。

step2: Import工程。選擇Import Projectes... 或者在Project Explorer中右擊,然后選擇Import... 或者File -> Import.

step3:在打開的Import對話框中選擇Efinix Projects-> Efinix Makefile Project可以導入。

step4:選擇bsp位置,這里我選擇

D:\FPGA_Prj\09_T120F324\01_RISCV_DEMO\T120F324_devkit\embedded_sw\efx_soc\bsp

如果是FreeRTOS的話,兩個都要輸入。

setp5:選擇下一步,然后勾選相應工程前面的方框,點擊finish即可以導入相應的demo工程。

step6:右鍵選擇build Project.

step7:run或者debug。

從2022版本之后,只要把路徑轉換到soc之后,不需要再設置debug路徑

這里以gpioDemo為例。

進入debug調試界面。

查看串口打印信息,在Window->Show View ->Terminal-> open the termianl。選擇Serial Terminal設置相關的串口信息。

其實在Debug時經常會報出以下問題:

Error:nodevicefound

Error:unabletoopenftdidevicewithvid0403,pid6014,description'ELITES-232DL',serial'*'atbuslocation'*'

這個錯誤其實并不陌生,文檔也有一個相關的記錄.

目前易靈思的下載器主要使用的是FTDI的 FT232,FT2232和FT4232方案。下圖是FT2232和FT4232芯片的原理圖,FT2232有channel 0,1兩個通道,在下圖已經標出。FT4234有channel 0,1,2,3共4個通道;而ELITES-232DL使用的是FT232,它只有channel 0.所以在使用不同的下載噐方案時,尤其是在對RISCV進行debug時就是使用不同的配置參數;否則就會報上面的錯誤。

那么怎么區別下載器使用的是什么芯片方案及對應的JTAG channel號呢?這個在打開programmer之后,就可以看到相應的ID.位置如下圖所示。而channel號是由易靈思的驅動來指定的,下表中列出JTAG使用的channel號。

| FTDI器件 | ID | JTAG channel |

| FT232 | 0403:6014 | 0 |

| FT2232 | 0403:6010 | 1 |

| FT4232 | 0403:6011 | 1 |

在上面的圖中我們還把USB Target用紅色框框了出來,因為不同的下載器名字是不一樣的,也是要修改的。

知道了上面的信息之后,我們就可以很清楚的知道我們的下載器使用的器件情況。

到現在我們可以對上面的報錯進行修改了,出現上面的報錯時應該怎么樣修改呢?這里還要分兩種情況,一種是hard jtag,另一種是soft的JTAG。區別在于修改的文件不同。

對于hard jtag,我們需要把embedded_sw\soc_xx\bsp\efinix\EfxSapphireSoc\openocd\ftdi.cfg(或者ftdi_ti.cfg,其中ftdi.cfg用于trion系列,而ftdi_ti.cfg 用于鈦金系列)修改成下載器讀出來的名字,這里包括ftdi_device_desc,ftdi_vid_pid及ftdi_channel三個參數,只需要按照上面的說明配置即可。

比如以YLS_DL下載器為例,

它使用的是FT2232的方案。修改結果如圖。

它使用的是FT2232的方案。修改結果如圖。

對于soft jtag,老版本的EFinity修改的是c232hm_ddhsl_0.cfg文件,而在2023.1版本的RISCV中已經沒有c232hm_ddhsl_0.cfg文件了。代之的是一個external.cfg文件。里面的內部與上面的是一樣的。

另外也遇到過修改了上面的問題還是存在問題的,經過確認客戶安裝的驅動是libusb-win32,可以用zadig的libusbk試試。

2.2、新建工程

File -> New -> Project...

可以選擇Standalone也可以選擇FreeRTOS

三、接口操作

APB3接口

請在公眾號中搜索"APB3接口應用"

GPIO

請在公從號中搜索"SOC GPIO操作”

四、邏輯文件與RISCV工程文件合并燒寫

在programmer中點擊Combine Multiple Image Files。打開Combine Multiple Image Files對話框,

選擇Generic Image Combination.并選擇右側的“*”添加文件,邏輯文件是生成的hex文件,RISCV工程生成的是bin文件。

輸入output file 文件名。指定地址,邏輯文件地址為0,

軟核的起始地址是大工程中指定的起始文件,最后點擊Aplly。

把合成的文件燒寫到flash。

最后:

我們會為各種應用提供相應的demo,歡迎關注我們的硬件平臺

原文標題:Efinity RISC-V IDE入門使用-4

文章出處:【微信公眾號:易靈思FPGA技術交流】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1660文章

22411瀏覽量

636271

發布評論請先 登錄

Vol.4 | 進迭時空孫彥邦:RISC-V的答案,不是篩選“幸存者”,而是集結“共建者”

為什么RISC-V是嵌入式應用的最佳選擇

進迭播客 | Vol.2 對話陳志堅:離開大廠RISC-V芯片創業4年,見500投資人,被拒 90%,我為何從沒想過放棄?

進迭播客 |「RISC-V 圓桌白話錄」首期正式上線!

大灣區RISC-V生態全景展示:RISC-V生態發展論壇、開發者Workshop和生態應用專區

普華基礎軟件亮相2025 RISC-V中國峰會

RISC-V 手冊

2025新思科技RISC-V科技日活動圓滿結束

Efinity RISC-V IDE入門使用-5

RISC-V 發展態勢與紅帽系統適配進展

RISC-V International CEO:RISC-V 應用全面開花,2031 年滲透率將達 25.7%

RISC-V和ARM有何區別?

RISC-V賽道的“硬核”突圍之路

FPGA與RISC-V淺談

原來,它們用的都是國產RISC-V芯片

Efinity RISC-V IDE入門使用-4

Efinity RISC-V IDE入門使用-4

評論