當柵與襯底之間存在壓差時,它們之間存在電場,靜電邊界條件使多晶硅靠近氧化層界面附近的能帶發生彎曲,并且電荷耗盡,從而形成多晶硅柵耗盡區。該耗盡區會在多晶硅柵與柵氧化層之間產生一個額外的串聯電容。當柵氧化層厚度減小到 2nm 以下,此電容的影響也會變得越來越嚴重,已經不再可以忽略。

多晶硅柵耗盡的寬度不像襯底量子效應那么復雜,它只需要采用簡單的靜電學就可以估算柵耗盡區的寬度。重摻雜的柵的摻雜濃度比輕摻雜的溝道的摻雜濃度要高,在亞閾值區,氧化層界面電位移的連續性意味著柵極的能帶彎曲小于襯底的能帶彎曲。考慮一個偏置到反型區的NMOS 的n型重摻雜的多晶硅,平帶電壓(VFB)和襯底電壓降(Φs)、柵電壓降(Φg)、氧化層電壓降(Vox)之和等于柵壓(Vg):

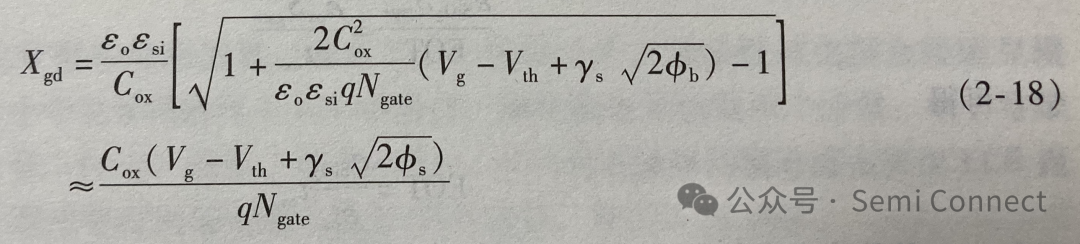

利用柵氧化層的邊界條件和高斯定理對公式(2-17)進行化簡求解,當Vg>Vth時,求得柵耗盡的寬度Xgd的公式如下:

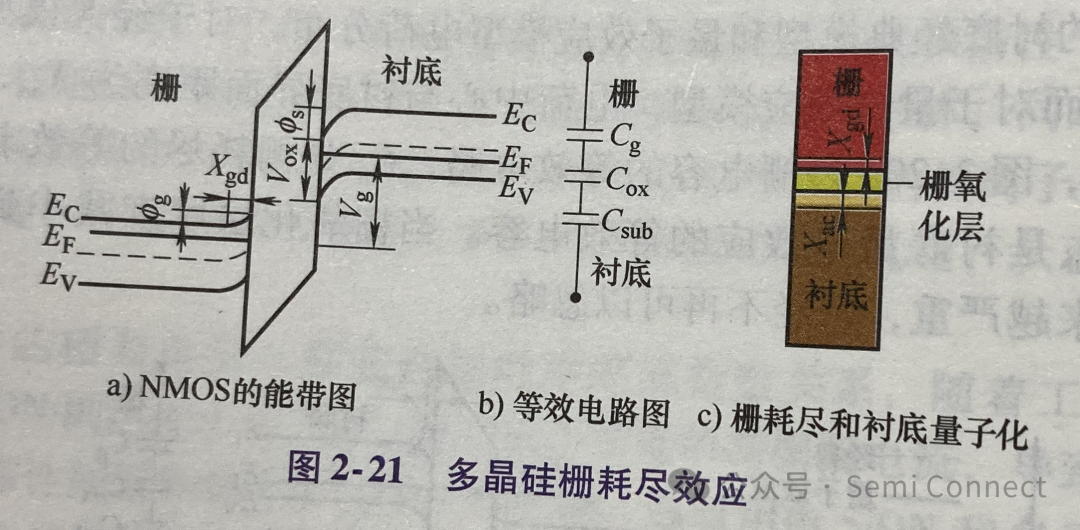

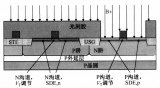

圖2~21a所示為柵極耗盡層的寬度Xgd,圖2-21b所示為柵耗盡的等效電容、柵氧化層的等效電容和襯底量子效應的等效電容的等效電路圖,圖2-21c所示為柵耗盡和襯底量子化的示意圖。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

多晶硅

+關注

關注

3文章

249瀏覽量

30663 -

靜電

+關注

關注

2文章

553瀏覽量

38241 -

NMOS

+關注

關注

3文章

401瀏覽量

36824

原文標題:多晶硅柵耗盡效應

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

【轉】一文看懂MOS器件的發展與面臨的挑戰

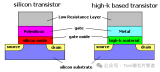

隧穿的效應,從而降低柵極漏電流及其引起的功耗。但是利用HK介質材料代替SiON也會引起很多問題,例如導致多晶硅柵耗盡效應形成高阻柵,HK介質材料與多

發表于 09-06 20:50

分析MOS管未來發展與面臨的挑戰

業界不斷開發出一系列的先進工藝技術,例如多晶硅柵、源漏離子注入自對準、LDD離子注入、polycide、Salicide、SRD、應變硅和HKMG技術。另外,晶體管也從MOSFET演變為FD-SOI

發表于 11-06 13:41

低溫多晶硅的工作原理是什么?

低溫多晶硅制程是利用準分子雷射作為熱源,雷射光經過投射系統後,會產生能量均勻分布的雷射光束,投射于非晶矽結構的玻璃基板上,當非晶矽結構玻璃基板吸收準分子雷射的能量后,會轉變成為多晶硅結構,因整個處理過程都是在600℃以下完成,所以一般玻璃基板皆可適用。

發表于 09-18 09:11

低溫多晶硅,低溫多晶硅是什么意思

低溫多晶硅,低溫多晶硅是什么意思

低溫多晶硅的全稱是“Low Temperature Poly-Silicon(LTPS,多晶硅又簡稱為p-Si

發表于 03-27 11:42

?1076次閱讀

多晶硅生產流程是什么_單晶硅與多晶硅的區別

本文已多晶硅為中心,主要介紹了多晶硅的技術特征、單晶硅與多晶硅的區別、多晶硅應用價值以及多晶硅行業走勢概況及預測進行分析。

發表于 12-18 11:28

?6.3w次閱讀

多晶硅柵(Poly-Si Gate)

多晶硅柵光刻工藝使用的光刻機是同一技術代集成電路工藝線中最先進、最昂貴的設備,它采用 UV 光源進行曝光,波長從g線(436nm)到DUV(248pm 和 193nm),以及 193nm 浸沒式;在光刻掩模版上采用了 OPC和PSM等技術

多晶硅柵工藝的制造流程

與亞微米工藝類似,多晶硅柵工藝是指形成 MOS器件的多晶硅柵極,柵極的作用是控制器件的關閉或者導通。淀積的多晶硅是未摻雜的,它是通過后續的源漏離子注入進行摻雜,PMOS 的柵是p型摻雜,NMOS 的柵是n型摻雜。

為什么采用多晶硅作為柵極材料

本文解釋了為什么采用多晶硅作為柵極材料 ? 柵極材料的變化 ? 如上圖,gate就是柵極,柵極由最開始的鋁柵,到多晶硅柵,再到HKMG工藝中的金屬柵極。 ? 柵極的作用 ? 柵極的主要作用是控制

多晶硅柵耗盡效應簡述

多晶硅柵耗盡效應簡述

評論