▼關注微信公眾號:硬件那點事兒▼

Part 01

前言

Part 02

實例計算

W0=(Vesd0-Vcl)*Vcl*Cesd0

其中Vesd0表示規格書中IC允許承受的最大ESD電壓(比如下圖的5000V),可以在規格書中找到這個參數,Vcl表示IC內部ESD防護模塊的鉗位電壓(比如下圖的64V),Cesd0表示IC ESD測試的放電電容(比如下圖的100pF)。

W1=(Vesd1-Vcl*(1+Cext/Cesd1))*Vcl*Cesd1

其中Vesd1表示產品實際測試的最大ESD電壓,比如8KV,Vcl表示IC內部ESD防護模塊的鉗位電壓,Cext表示外部添加的ESD電容,Cesd1表示產品實際測試的ESD 放電電容(比如330pF)。

3.添加的外部ESD電容容值如何計算?

基于IC實際吸收的ESD能量W1要小于IC允許的最大ESD脈沖能量W0可以計算出外部電容的最小容值:

Cext_min=((Vesd1-Vcl)*Cesd1/Vcl)-W0/Vcl*Vcl

以接觸放電8KV,源電容330pF,放電電阻2kΩ,可以計算出Cext_min>33nF。

有問題歡迎在評論區留言交流哦!

有問題歡迎在評論區留言交流哦!

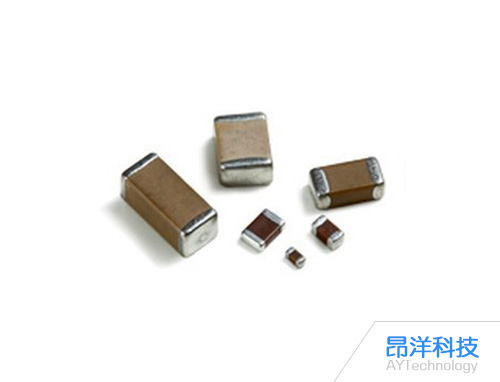

原文標題:一種新的MLCC陶瓷電容用于電路靜電ESD保護的電容容值計算方法

文章出處:【微信公眾號:硬件那點事兒】歡迎添加關注!文章轉載請注明出處。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

發布評論請先 登錄

相關推薦

熱點推薦

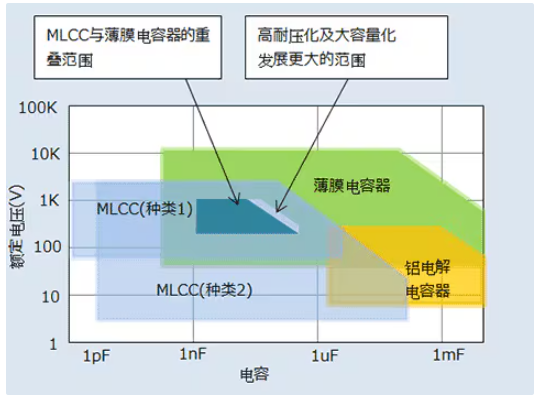

貼片電容 MLCC 的容值隨電壓變化的特性是怎樣的?

貼片電容MLCC的容值隨電壓變化的特性主要表現為直流偏壓特性,即電容值隨施加直流電壓的增加而降低,且這一

信維低損耗MLCC電容,提升電路效率優選

損耗 :信維低損耗MLCC電容采用高純度陶瓷介質材料(如鈦酸鋇基復合陶瓷),通過優化配方和工藝,將介質損耗角正切(tanδ)降低至極低水平(如≤10??)。這

yageo電容-國巨陶瓷電容-國巨陶瓷貼片電容的詳細介紹

國巨(YAGEO)陶瓷貼片電容(MLCC)是高性能、高可靠性的電子元件,具有多樣化的尺寸、電容值、電壓范圍和溫度特性,廣泛應

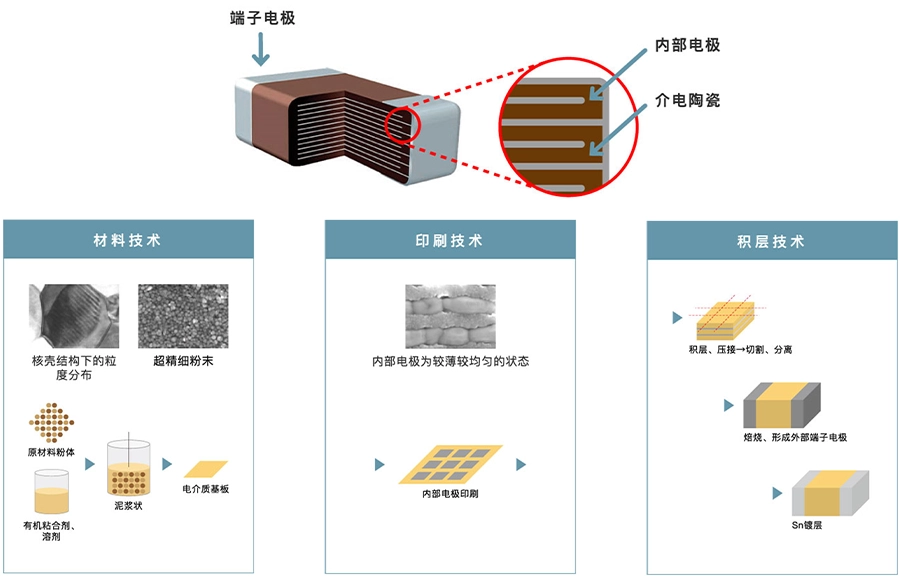

三星貼片電容的疊層陶瓷技術(MLCC)詳解

三星貼片電容的疊層陶瓷技術,即MLCC(Multi-layer Ceramic Capacitors,多層陶瓷電容器),是

啊? 你的貼片陶瓷電容還在嘯叫呢?

小、穩定性高、損耗低、耐壓高 缺點:容值小,最大僅有1nF,價格高Ⅱ類介質MLCC:優點:容值大,體積小,價格低缺點:損耗和絕緣性較Ⅰ類低

3.選用高耐壓的貼片陶瓷

發表于 03-14 11:29

一種新的MLCC陶瓷電容用于電路靜電ESD保護的電容容值計算方法

一種新的MLCC陶瓷電容用于電路靜電ESD保護的電容容值計算方法

評論