現(xiàn)代社會的各個方面都需要先進的人工智能(AI)來處理,例如對周圍環(huán)境的識別、行動決策和運動控制,這包括工廠、物流、醫(yī)療、城市中的服務機器人以及安全攝像頭等應用場景。然而,要在邊緣端實現(xiàn)人工智能,我們需要克服兩大挑戰(zhàn):功耗和靈活性。

在云端,我們可以配備足夠的電源和冷卻機制來支持復雜的AI模型,但邊緣端的設備往往限制了功耗,這可能導致運行時間的縮短和成本的增加。此外,隨著AI模型不斷發(fā)展,專用的AI加速硬件很快就會過時,這意味著我們需要一種更靈活的解決方案來支持新開發(fā)的AI模型。因此,嵌入式端的AI加速成為一個重要的解決方案,它可以在邊緣設備上實現(xiàn)AI任務的高效執(zhí)行,并為新的AI模型提供靈活性和支持。

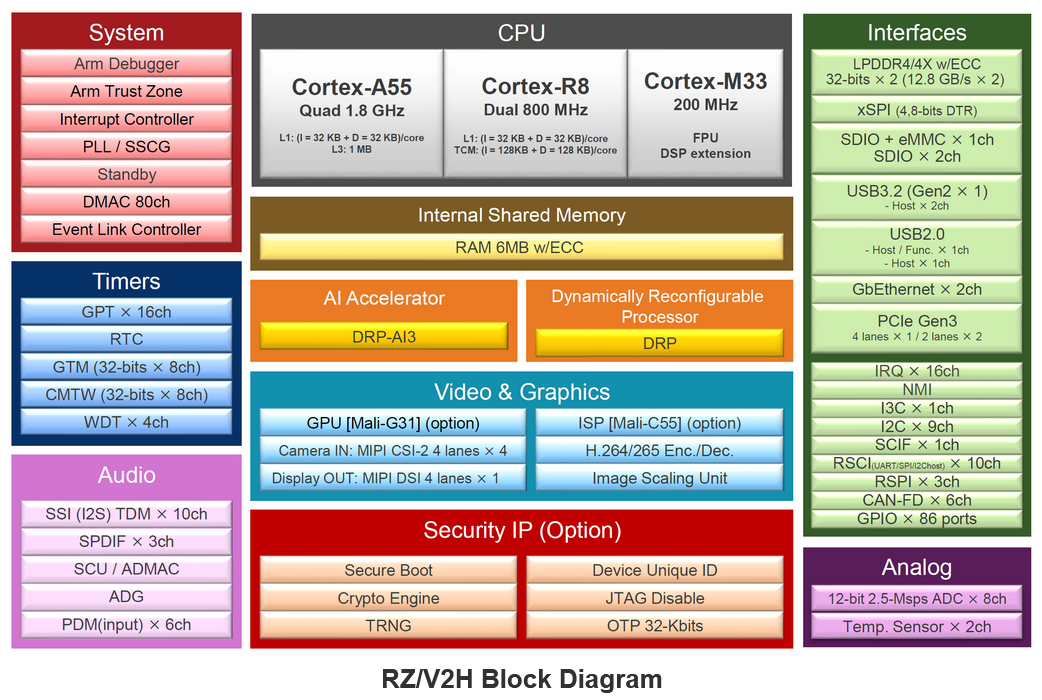

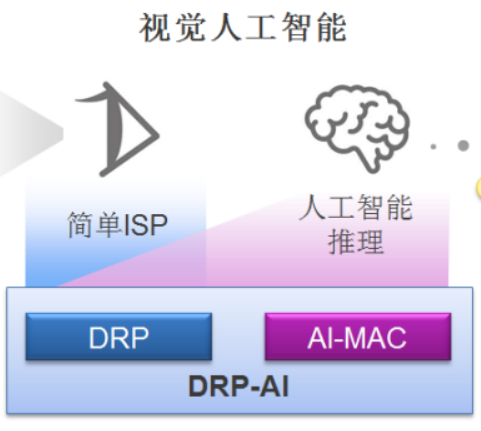

為了滿足市場需求,瑞薩自主研發(fā)了用于AI加速的處理器DRP-AI(Dynamically Reconfigurable Processor for AI人工智能動態(tài)可配置處理器),該處理器集成與RZ/V系列芯片中。

DRP-AI處理器具備邊緣端設備所需的低功耗和靈活性,經(jīng)過多年技術迭代已發(fā)展到第三代,實現(xiàn)了比上一代高約10倍的能效。DRP-AI3(集成與RZ/V2H)能夠適應AI的進一步發(fā)展和高性能機器人等應用的復雜要求。

DRP-AI3解決了低功耗挑戰(zhàn),并實現(xiàn)了高實時處理。它為具有AI能力的產(chǎn)品提供了更高性能和更低功耗。接下來,我們將深入了解DRP-AI3是如何實現(xiàn)這些目標的。

1軟、硬結合系統(tǒng)性地實現(xiàn)AI模型的高速和低功耗

量化

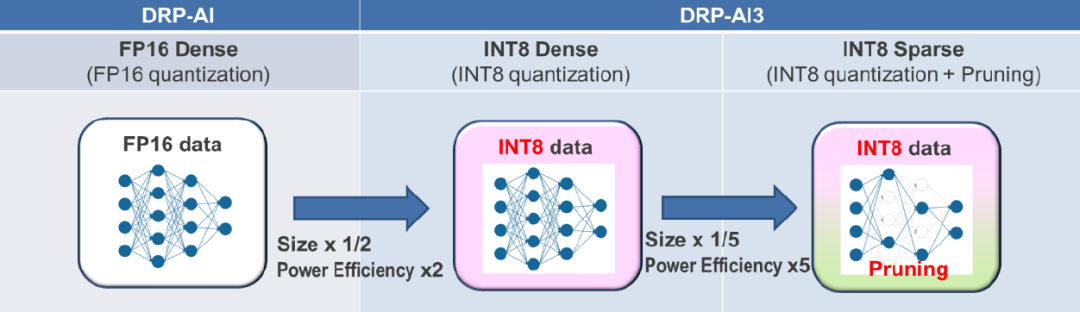

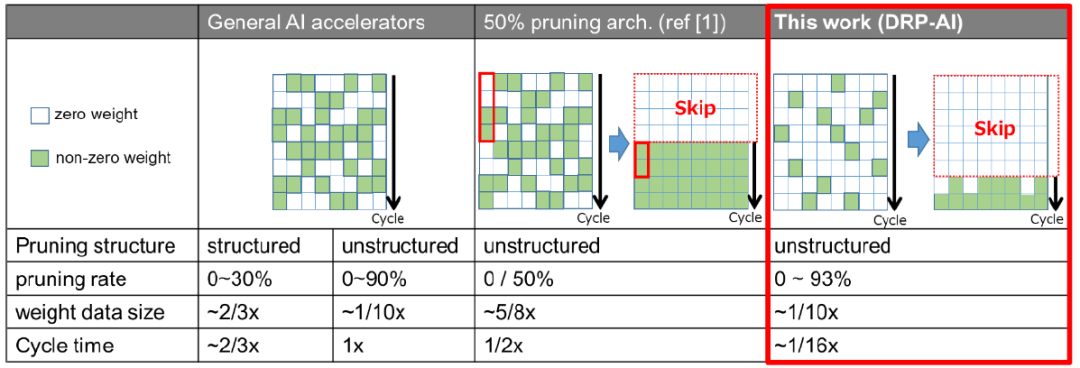

從傳統(tǒng)的16位浮點運算更改為8位整數(shù)運算(INT8)。該方法也是現(xiàn)在比較流行的一種運算處理方式。

修剪

采用靈活的N:M修剪方法

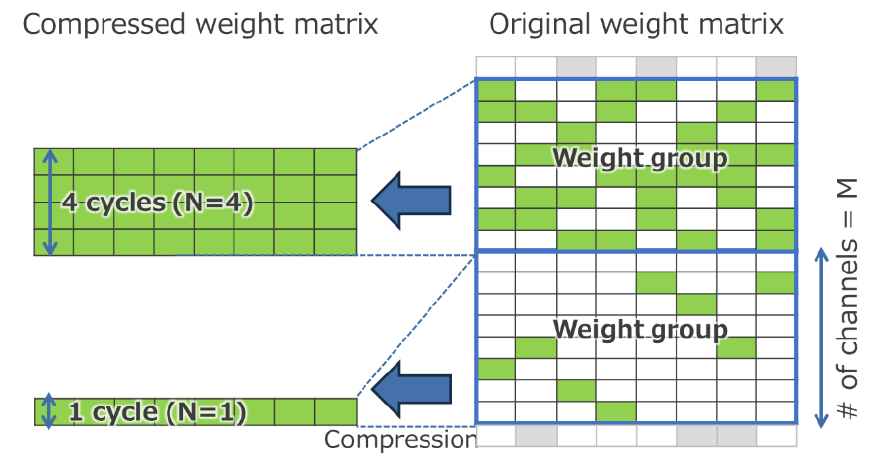

N:M技術的基本概念是將原始權重矩陣劃分為M行的權重矩陣組,并將其重構為較小的N行權重矩陣組。在每組中,只提取有效權重,然后對新的權重矩陣組進行并行運算。DRP-AI3引入了一個新功能,它可以通過自由切換每個權重矩陣組的N值來調(diào)整運算周期的數(shù)量,從而可以在實際的AI模型中對局部變化的修剪率執(zhí)行最優(yōu)的運算處理。這種精細改變N的能力還允許詳細設置整個權重矩陣的修剪率,根據(jù)用戶對功耗、操作速度和識別精度的要求進行最佳的修剪處理。

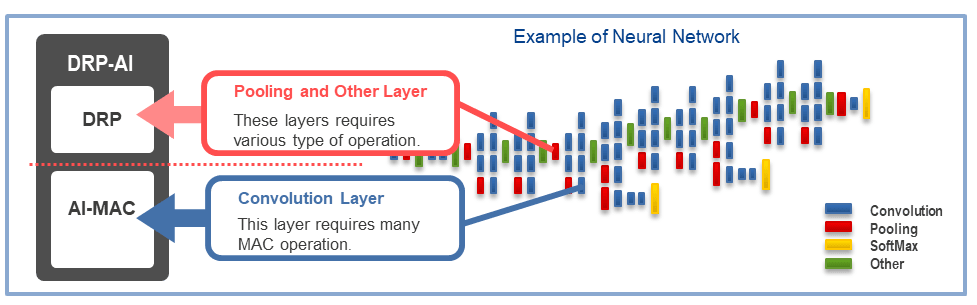

2AI系統(tǒng)架構實現(xiàn)高功效

通過數(shù)據(jù)重用技術減少外部存儲器通信

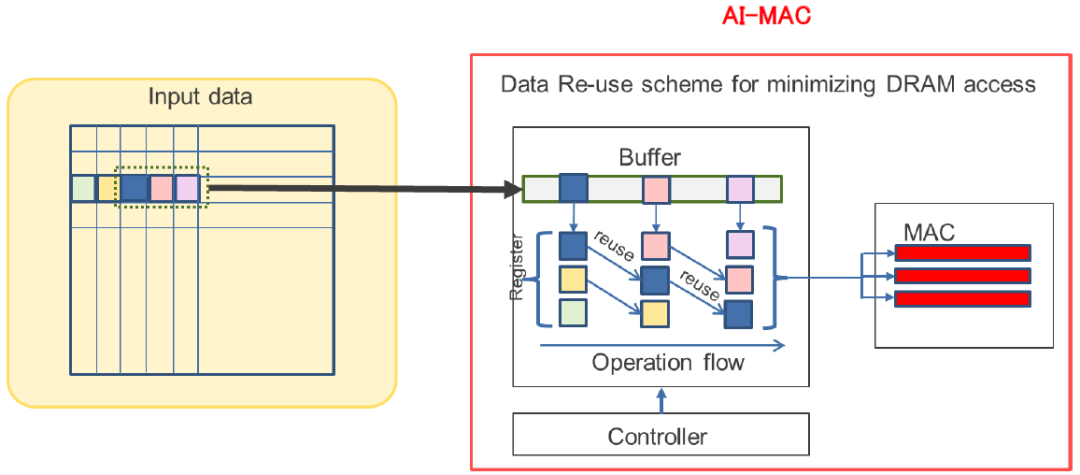

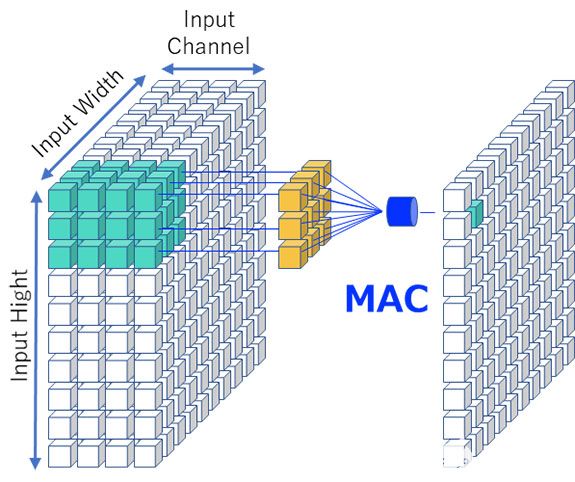

DRP-AI采用了一種有效地重用一次輸入到AI-MAC的技術。例如,在3x3濾波器的卷積運算中,一個數(shù)據(jù)像素用于九個濾波器運算。im2col被廣泛用作GPU中的高度并行運算方法,它以矩陣運算的順序擴展所有圖像數(shù)據(jù)作為輸入到GPU的預處理步驟。然而,這會導致一個像素的數(shù)據(jù)信息出現(xiàn)九次,數(shù)據(jù)的數(shù)量增加了九倍,進而增加了功耗和通信帶寬的消耗。相比之下,AI-MAC可以通過將取入與MAC算術單元相對應的寄存器中的數(shù)據(jù)移位到相鄰寄存器來重用數(shù)據(jù),從而避免了重復存儲和傳輸數(shù)據(jù),減少了功耗和通信帶寬的消耗。

通過采用如下圖所示的配置,與GPU相比,從外部存儲器和內(nèi)部緩沖器到AI-MAC的數(shù)據(jù)加載的數(shù)量可以減少多達九倍。這種優(yōu)化方案顯著降低了數(shù)據(jù)移動所需的功率和通信帶寬消耗。此外,AI-MAC不僅可以對輸入數(shù)據(jù)進行重用,還可以對輸出和權重信息進行重用,從而將對外部存儲器的訪問減少了一個數(shù)量級以上。

使用輸入的零數(shù)據(jù)控制功耗

人工智能模型計算的一個特點是每一層的權重數(shù)據(jù)和輸入/輸出數(shù)據(jù)中“零”值的比例很高,這被稱為稀疏化。例如,在圖像識別模型中,所有層50%以上的輸入和輸出數(shù)據(jù)平均為零值。這主要是因為許多人工智能模型使用激活函數(shù)(如ReLU),該函數(shù)會將乘積和運算的所有負結果替換為零。在DRP-AI中,通過引入切換技術來減少不必要的計算能力。該切換技術預先檢測何時在操作的每個元素輸入中輸入零,并防止不必要的操作。

操作調(diào)度流程

除了數(shù)據(jù)重用技術之外,優(yōu)化外部數(shù)據(jù)訪問或MAC處理等操作的順序和定時對于有效的AI執(zhí)行至關重要。換句話說,調(diào)度操作流程可以最大化DRP-AI的性能。

例如,通過調(diào)度外部存儲器訪問定時,可以在AI-MAC操作期間提前讀取下一操作的權重信息并將其存儲在緩沖器中,從而防止和減少外部存儲器訪問延遲。這種方式也可應用于內(nèi)部存儲器訪問和任何內(nèi)部算術處理的定時中,調(diào)度可以避免每個處理之間不必要的等待時間和功耗的產(chǎn)生。由于DRP-AI工具自動生成這種優(yōu)化的調(diào)度,用戶能夠輕松應對。

瑞薩開發(fā)的DRP-AI3(人工智能動態(tài)可重構處理器)是一種獨特的AI加速器。它將嵌入式端所需的低功耗和靈活性與人工智能模型輕量級的處理能力相結合,相較于以前的模型,DRP-AI3的能效提高了10倍(10 TOPS/W)。

瑞薩將繼續(xù)擴大研發(fā)RZ/V系列,以提供更多配備這種卓越AI加速器的MPU產(chǎn)品。

-

處理器

+關注

關注

68文章

20249瀏覽量

252177 -

瑞薩

+關注

關注

37文章

22481瀏覽量

90847 -

AI

+關注

關注

91文章

39746瀏覽量

301338

發(fā)布評論請先 登錄

基于瑞薩RZ/V2H AI微處理器的解決方案:高性能視覺AI系統(tǒng)

嵌入式AI加速器DRP-AI 詳細介紹

Banana Pi 與瑞薩電子攜手共同推動開源創(chuàng)新:BPI-AI2N

Banana Pi 發(fā)布 BPI-AI2N & BPI-AI2N Carrier,助力 AI 計算與嵌入式開發(fā)

瑞薩電子推出支持入門級AI應用設計的全新RZ/V2L MPU

工程師說 | 引入DRP-AI TVM以簡化AI模型的實施

瑞薩電子RZ/V2系列MPU簡介

RZ/V2L DRP-AI支持包版本.7.41發(fā)布說明

瑞薩發(fā)布下一代動態(tài)可重構人工智能處理器加速器

瑞薩推出集成DRP-AI加速器的RZ/V2N,擴展中端AI處理器陣容,助力未來智能工廠與智慧城市發(fā)展

瑞薩電子RZ/V系列微處理器助力邊緣AI開發(fā)

瑞薩高性能AI加速處理器DRP-AI解析

瑞薩高性能AI加速處理器DRP-AI解析

評論