1?

院校簡介

//

河北工程大學是河北省重點骨干大學,河北省人民政府與水利部共建高校,河北省重點支持的國內一流大學建設高校,河北省文明單位,坐落在中國歷史文化名城、“成語典故之都”邯鄲市。

學校現有工學、理學、管理學、農學、醫學、文學、經濟學、法學、藝術學、教育學、歷史學11個學科門類。招生專業72個,其中工程類專業47個,占比達65.2%。擁有河北省唯一的服務國家特殊需求博士人才培養項目—水資源水環境調控及綜合管理,擁有河北省唯一的水利工程博士后科研流動站。工程學學科進入ESI排名全球前1%。擁有水利工程、地質資源與地質工程、機械工程、管理科學與工程等17個碩士學位授權一級學科

機械與裝備工程學院是河北工程大學辦學歷史最悠久的學院之一,學院設有6個教學系,建設有機械設計制造及其自動化、車輛工程、材料成型及控制工程、機器人工程、測控技術與儀器、機械電子工程(3+4)等6個本科專業。建設有1個國家級一流本科專業“機械設計制造及其自動化”,1個省級一流本科專業“車輛工程”,1個新工科專業“機器人工程”,“測控技術與儀器”專業已經通過工程教育認證申請。

2?

實驗室狀態

創龍教儀聯合河北工程大學共同建設高性能DSP+FPGA教學平臺,在機械與裝備工程學院-精密測量實驗室,針對DSP+FPGA課程,探討了該課程的應用方向,制定學生課程學習的培養計劃。

TL6678F-TEB相關實驗(部分) | |

DSP實驗環境搭建與CCS開發基礎 | 安裝CCS與串口調試工具 CCS工程新建、編譯和導入 |

DSP算法實驗 | 有限沖激響應濾波器(FIR)算法 無限沖激響應濾波器(IIR)算法 快速傅立葉變換(FFT)算法 一維FFT性能測試算法 |

圖像類實驗 | 圖像旋轉、縮放和反色 灰度圖像直方圖、直方圖均衡化 邊緣檢測 灰度圖像二值化 RGB24圖像灰度轉換 |

SYS/BIOS實驗 | 創建任務實驗 定時器控制實驗 創建硬件中斷實驗 執行軟件中斷實驗 SYS/BIOS時間戳實驗 SYS/BIOS時間戳實驗 |

MultiCore實驗 | 圖像旋轉 圖像縮放 邊緣檢測 RGB24圖像灰度轉換 |

綜合類實驗 | CameraLink 工業相機實時檢測與處理 圖像拼接、復原、超分辨率重建 目標跟蹤、人臉檢測 |

參與交流的黃老師,孫老師等和學生們對TL6678F-TEB相關實驗案例表現出十足的熱情,并對創龍教儀專業的技術能力與認真的工作態度表示了肯定。

面對日新月異的技術發展,創龍教儀在不斷學習與探索新技術與高校新需求之間的聯系,并通過與高校間的交流學習助力高校培養能夠適應新社會生產需求的高級人才,以響應國家二十大“產教融合”的方針!

3?

特色案例

實驗名稱:

CameraLink工業相機實時檢測與處理綜合實驗

實驗目的:

(1)了解TI C66x DSP和Xilinx FPGA平臺的優勢和應用。

(2)了解CameraLink工業相機和MJPEG。

(3)學習基于TI C6678 DSP和Xilinx FPGA實現CameraLink工業相機實時檢測與處理。

實驗原理:

CameraLink工業相機簡介

CameraLink工業相機是指具有CameraLink接口滿足工業要求的相機。CameraLink接口是由AIA協會推出的數字圖像信號串行通訊接口協議,是在ChannelLink技術基礎上發展而來的。CameraLink標準支持的最高數據傳輸率可達680MB/s。

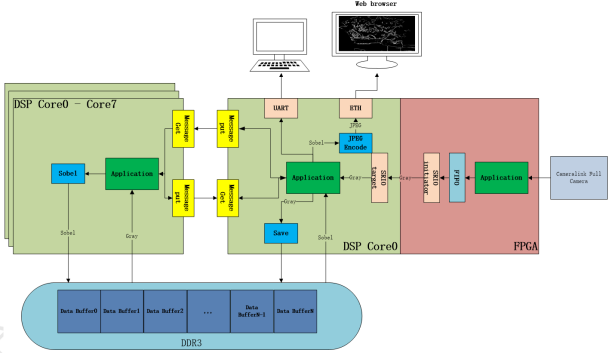

FPGA端作為SRIO Initiator,DSP端作為SRIO Target。FPGA端通過SRIO SWRITE和乒乓方式,將數據傳輸至DSP端的0x90000000和0x90500000的DDR地址空間。

DSP端project目錄下包括兩個工程,分別為主核工程與從核工程。主核工程編譯后默認生成的可執行文件適用于DSP ETH1網口,如需重新生成適用于DSP ETH0網口的可執行文件,請參考關鍵代碼小節進行源碼修改。從核工程編譯后生成的可執行文件為srio_image_processing_slave.out。

工程解析

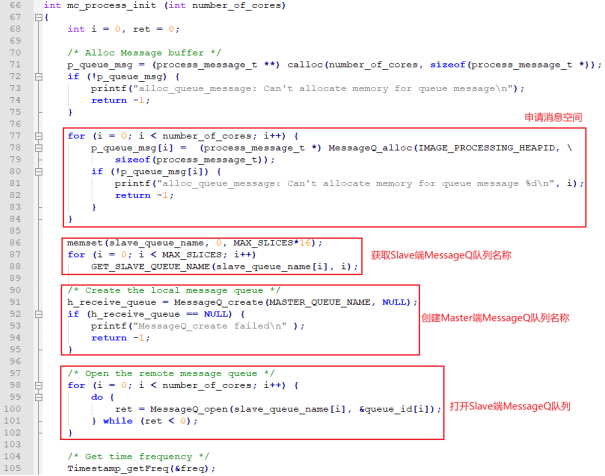

Image_processing_master任務調用mc_process_init函數,初始化和打開對應消息隊列,用于傳輸消息。

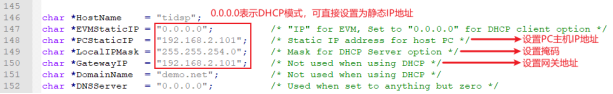

默認使用DHCP模式自動獲取DSP ETH1網口IP地址。如需修改為靜態IP地址,或修改為使用DSP ETH0網口,可參考如下說明進行配置。

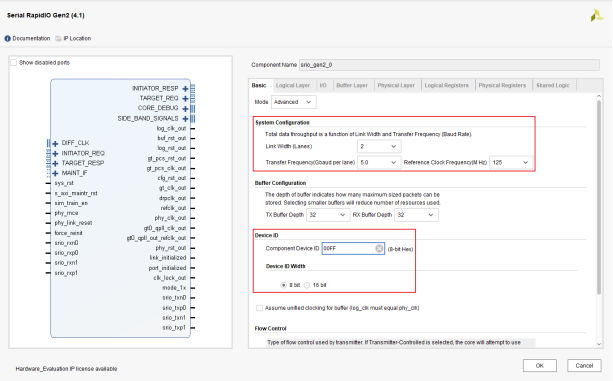

本案例使用Serial RapidIO Gen2 IP核實現SRIO Initiator,使用HELLO(Header Encoded Logical Layer Optimized)格式,支持NREAD、NWRITE、NWRITE_R、NWRITE_R、DOORBELL、MESSG等Response Packet操作。

實驗設備

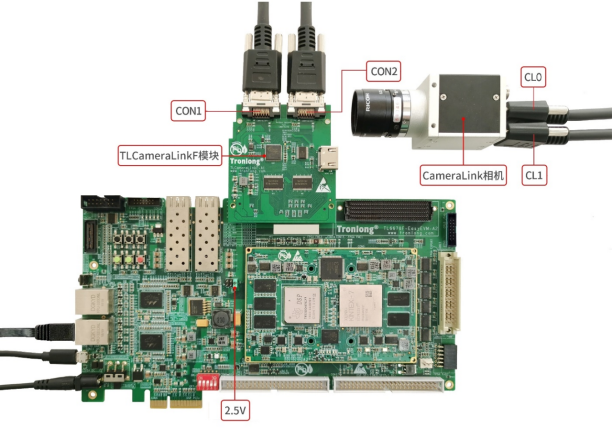

硬件:TL6678F-TEB,CameraLink黑白相機(型號:RS-A5241-CM107-S00),CameraLink視頻采集模塊(型號:TLCameraLinkF),路由器(動態IP需要,如采用靜態IP方式可不需要)。

軟件:Vivado2017.4,CCS5.5,Windows7以上操作系統。

硬件連接

(1)用Micro USB串口線將PC端連接實驗主板調試串口。

(3)將FPGA下載器連接開發板FPGA端JTAG接口(CON10)到PC端。

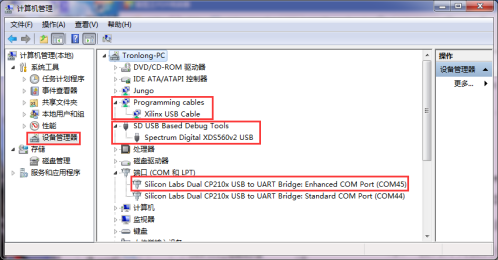

(4)打開設備管理器查看Enhanced COM port口的COM口號、查看仿真器和下載器連接是否正常。

(5)打開并設置串口調試軟件,波特率為115200。

(6)將TLCameraLinkF模塊連接至評估板FPGA FMC2接口,評估板J1跳線帽選擇2.5V檔位,以配置FMC IO的BANK電壓為2.5V。請將CameraLink相機的CL0通過數據線連接至TLCameraLinkF模塊的CON1接口,將CameraLink相機的CL1通過數據線連接至TLCameraLinkF模塊的CON2接口。

(7)用網線連接實驗主板和路由器,實驗主板默認ETH1口,要保證開發板與PC端保持在同一網段下。

(8)撥碼開關撥到NO BOOT模式:000XX(備注:XX為1或0均可)。

(9)實驗箱上電。

實驗現象

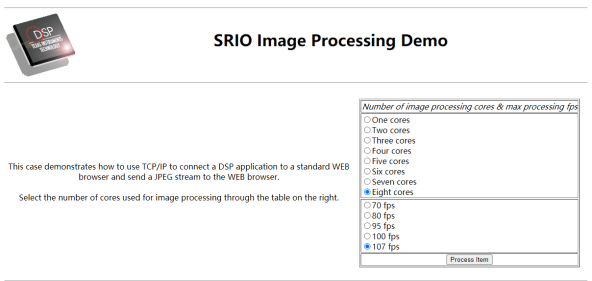

在PC機瀏覽器輸入評估板IP地址打開網頁界面,在網頁界面中選擇處理核心數量為Eight cores,選擇本案例所使用相機的最高處理幀率為107fps。

點擊"Program Item",網頁將顯示經DSP端進行Sobel(邊緣檢測)算法處理后的圖像。

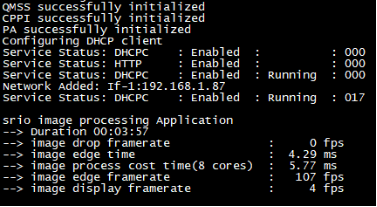

同時,DSP端串口調試終端將會打印處理信息。

4?

設備概述

//

產品型號:TL6678F-TEB

處理器類型:TI TMS320C6678 + Xilinx Kintex-7

-

dsp

+關注

關注

561文章

8244瀏覽量

366614 -

FPGA

+關注

關注

1660文章

22411瀏覽量

636265 -

機器人

+關注

關注

213文章

31075瀏覽量

222195

發布評論請先 登錄

產教融合新標桿:小眼睛科技助力北理工-紫光同創國產FPGA課賽結合實驗室隆重揭牌!

北京理工大學集成電路與電子學院和紫光同創國產FPGA課賽結合實驗室揭牌

基于DSP與FPGA異構架構的高性能伺服控制系統設計

怎么建設高性能多核DSP+FPGA實驗室?一起來河北工程大學看看

怎么建設高性能多核DSP+FPGA實驗室?一起來河北工程大學看看

評論